A wiring method for integrated circuit vlsi

A technology of integrated circuit and wiring method, which is applied in the direction of CAD circuit design, etc., can solve the problems of reducing the length of wiring lines and cannot be optimized, and achieve the effect of reducing the length of wiring lines

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The preferred embodiments of the present invention will be described below with reference to the accompanying drawings. It should be understood that the preferred embodiments described herein are only used to illustrate and explain the present invention, but not to limit the present invention.

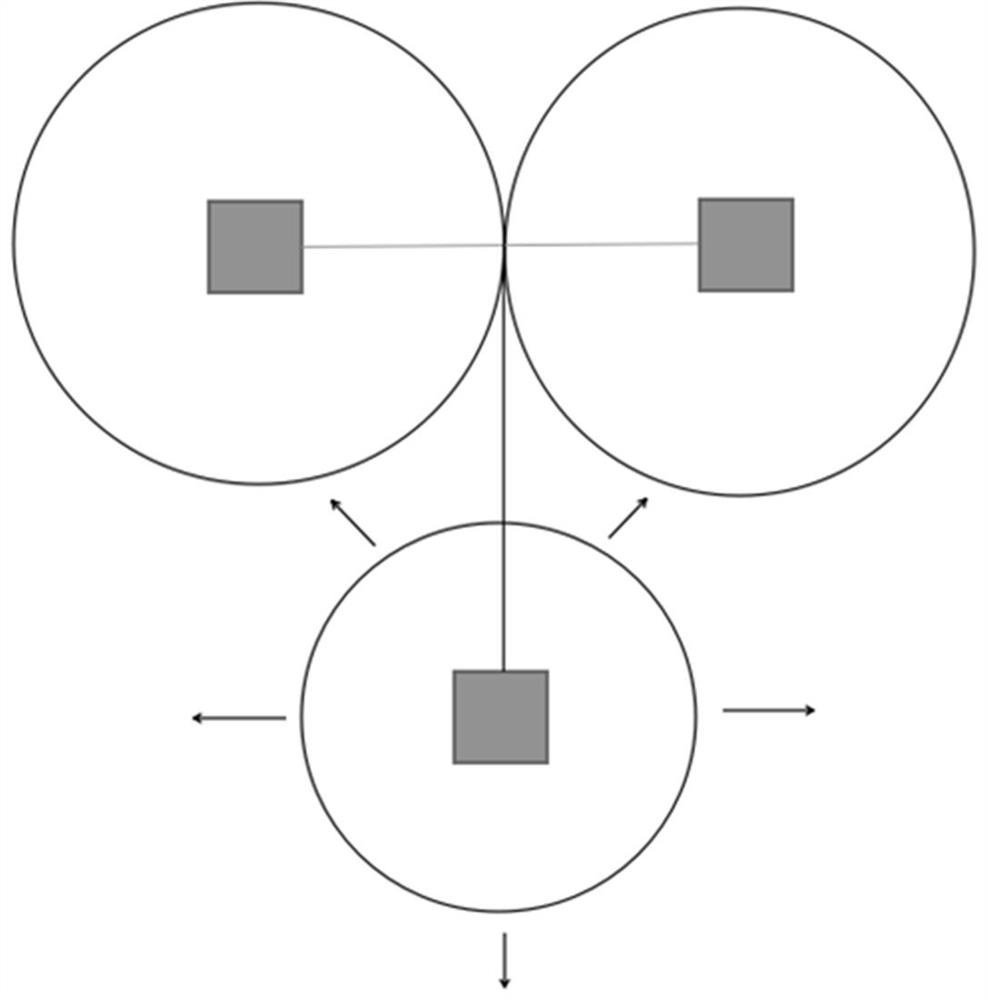

[0031] In the embodiment of the present invention, the processing and analysis are performed with multiple port graphs of a single wire net, and the processing methods for multi-port graphs of a multi wire net are similar in the following.

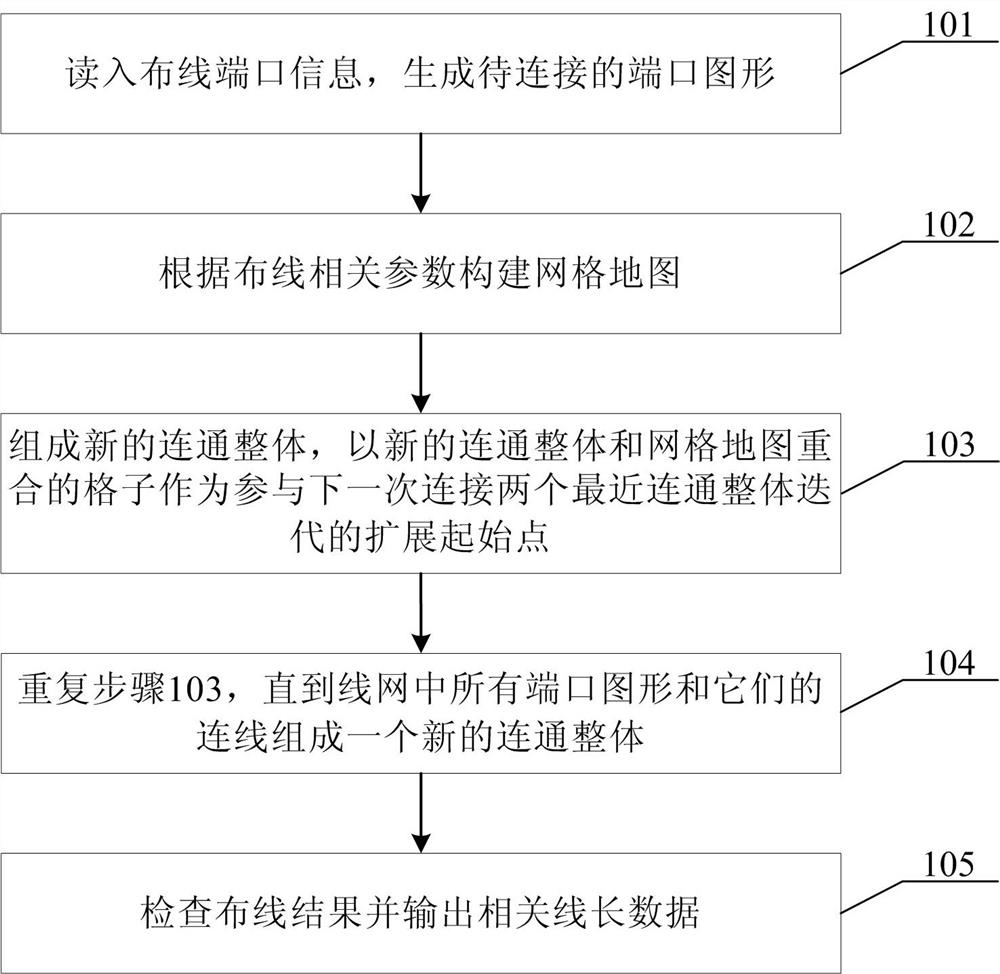

[0032] figure 1 For the wiring method flow chart of a kind of integrated circuit VLSI according to the present invention, the following will refer to figure 1 , a wiring method of an integrated circuit VLSI of the present invention will be described in detail.

[0033] First, in step 101, wiring port information is read in, and a port pattern to be connected is generated. In this step, a plurality of port patterns waiting to be connected f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More