Super-large-scale heterogeneous FPGA (Field Programmable Gate Array) layout method considering clock constraint

A super-large-scale, layout-based technology, applied in instrumentation, computing, electrical and digital data processing, etc., can solve problems such as poor FPGA layout results, and achieve the effect of improving FPGA performance, reducing wiring line length, and improving layout quality.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The technical solution of the invention will be described in detail below in conjunction with the accompanying drawings.

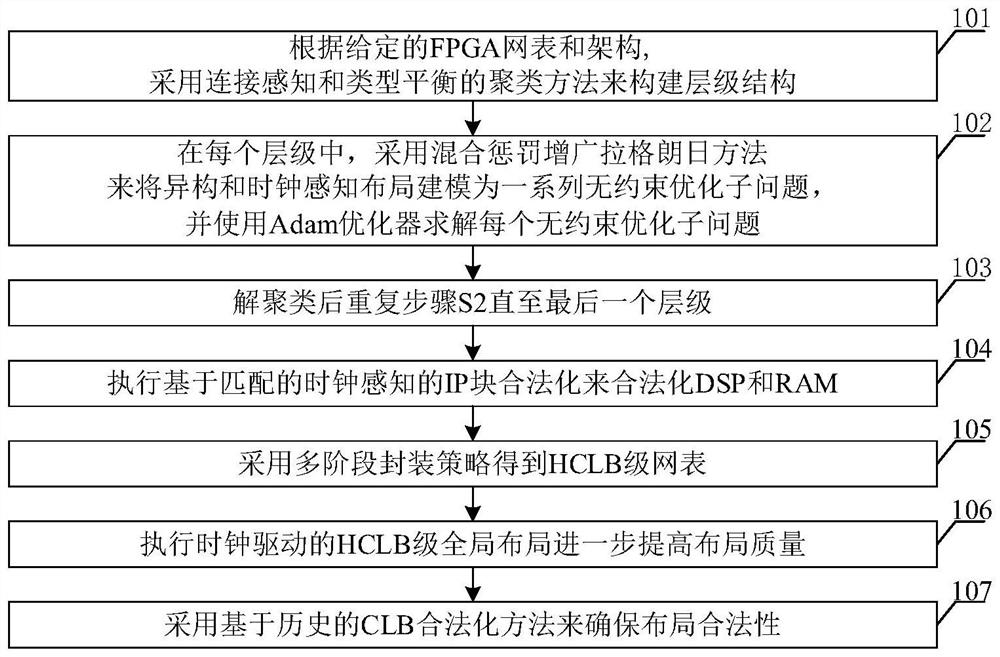

[0052] The present invention provides a super-large-scale heterogeneous FPGA layout method considering clock constraints. The method first performs connection-aware and type-balanced clustering based on a given netlist and architecture, and then uses hybrid penalty augmentation considering heterogeneity and clock-awareness. The wide Lagrangian method and Adam-based optimizer are used for multi-level module placement, followed by IP legalization and multi-stage packaging, and finally CLB-level global layout and CLB legalization. Such as figure 1 As shown, the method includes the following steps:

[0053] 101. According to a given FPGA netlist and architecture, a hierarchical structure is constructed by using a connection-aware and type-balanced clustering method;

[0054] 102. In each level, a hybrid penalized augmented Lagrangian method is used to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More