Liquid crystal writing film local erasing voltage loading control method

A technology of erasing voltage and control method, which is applied in the input/output process of electrical digital data processing, instruments, and data processing, etc., can solve the problem of excessive capacitance of liquid crystal writing film, uneven thickness of coating glue, affecting local erasing effect and other issues, to achieve the effect of improving yield, reducing quality and processing accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

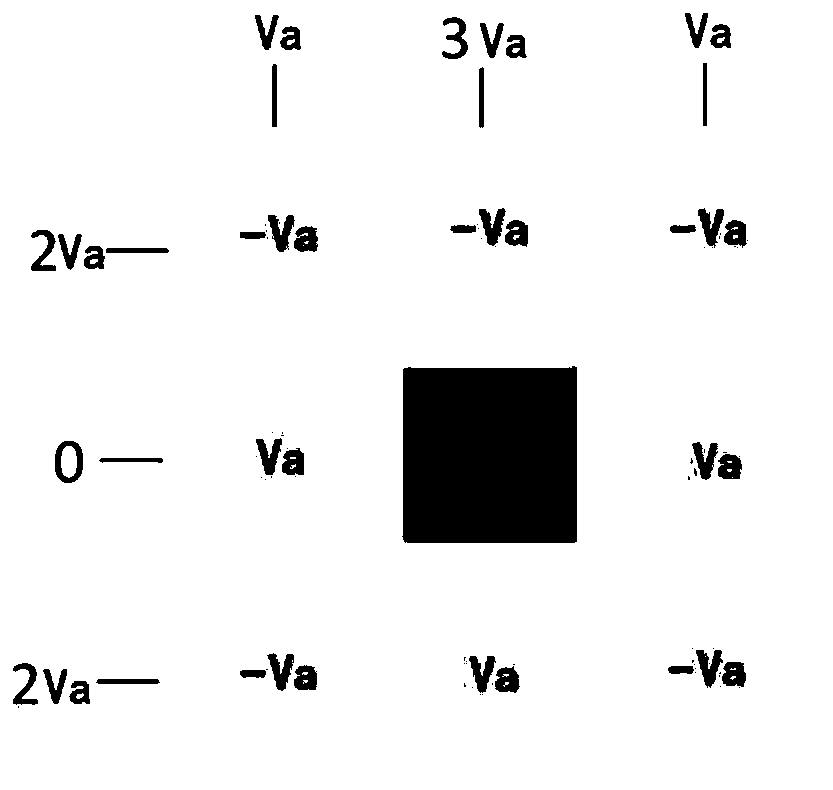

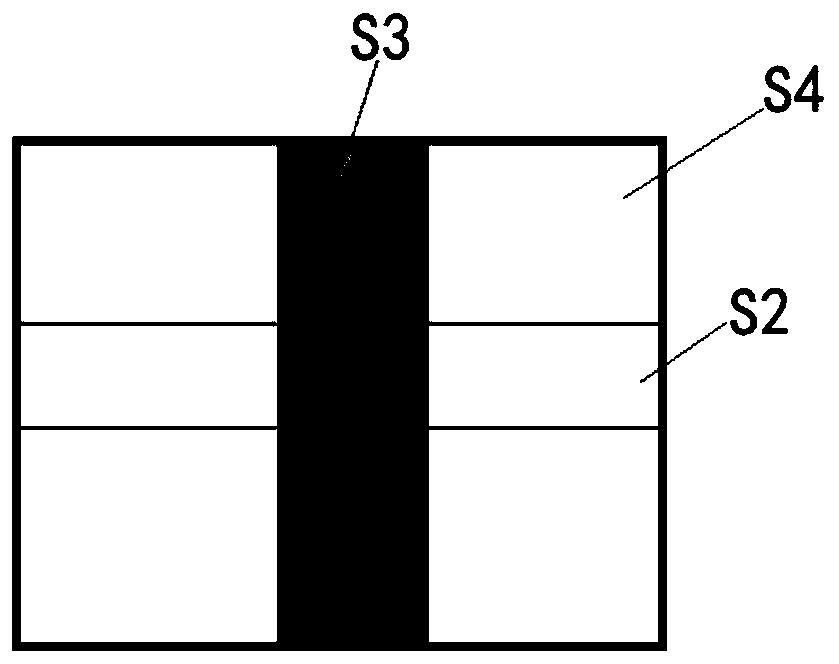

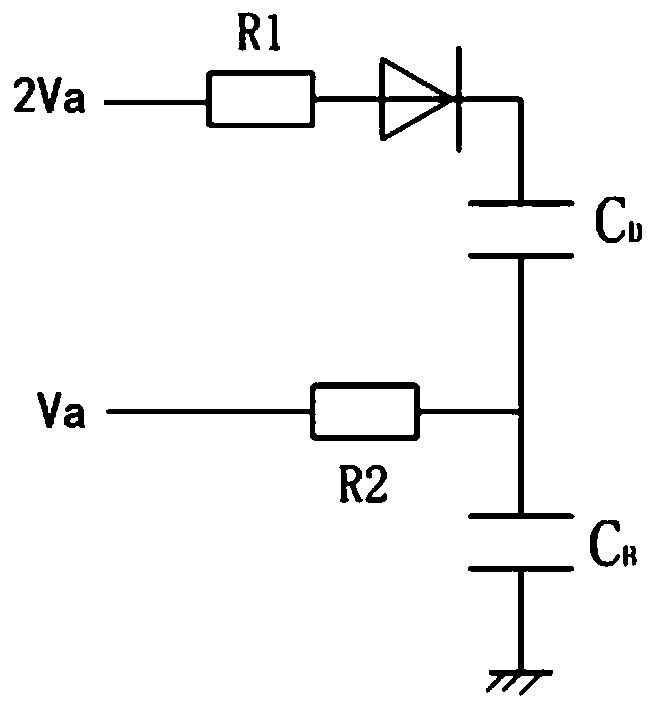

[0063] Based on the above description of the existing problems in the prior art, the embodiment of the present invention discloses a local erasing voltage loading control method for liquid crystal writing film, including a control method for boosting process and a control method for stepping down process; wherein, the liquid crystal writing film Located between two conductive layers, the two conductive layers are respectively divided into two or more than two conductive regions. In this embodiment, the first conductive layer is divided into two or more lateral conductive regions that are insulated from each other, and the second conductive layer is divided into two or more vertical conductive regions that are insulated from each other; The conductive regions on the second conductive layer and the conductive regions on the second conductive layer are vertically interlaced with each other in space. By dividing the conductive layer, the writing film is divided into a network stru...

Embodiment 2

[0101] In one or more embodiments, a method for controlling local erasing voltage loading of a liquid crystal writing film is disclosed, including a method for controlling a voltage boosting process and a method for controlling a voltage reduction process; wherein, the structure of the liquid crystal writing film is the same as that in Example 1, No longer.

[0102] The boosting process control method disclosed in this embodiment is specifically:

[0103] applying a first voltage to a conductive region of the first conductive layer covering the partially erased region, and applying a second voltage to a conductive region set outside the conductive region on the first conductive layer covering the partially erased region;

[0104] Applying a third voltage to all the conductive regions on the second conductive layer; the third voltage makes the electric field formed between the first conductive layer and all the conductive regions on the second conductive layer smaller than the ...

Embodiment 3

[0143] On the basis of Embodiment 1 and Embodiment 2, the embodiment of the present invention discloses a specific application product using a partial erasing voltage loading control method, such as:

[0144] The local erasing voltage generation and control method of the present invention is applied to a writing board, a drawing board or a blackboard to realize the local erasing function.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More