Heterogeneous multi-core processor for bus equipment connection adjustment

A technology of multi-core processors and bus devices, applied in the direction of electrical digital data processing, instruments, computers, etc., can solve the problems of access impact, inability of CPU to access shared memory immediacy and isochronism guarantee, time impact, etc., to achieve Immediate and isochronous guarantee, the effect of improving access performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The following will clearly and completely describe the technical solutions in the embodiments of the application with reference to the drawings in the embodiments of the application. Apparently, the described embodiments are only some of the embodiments of the application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protection of this application.

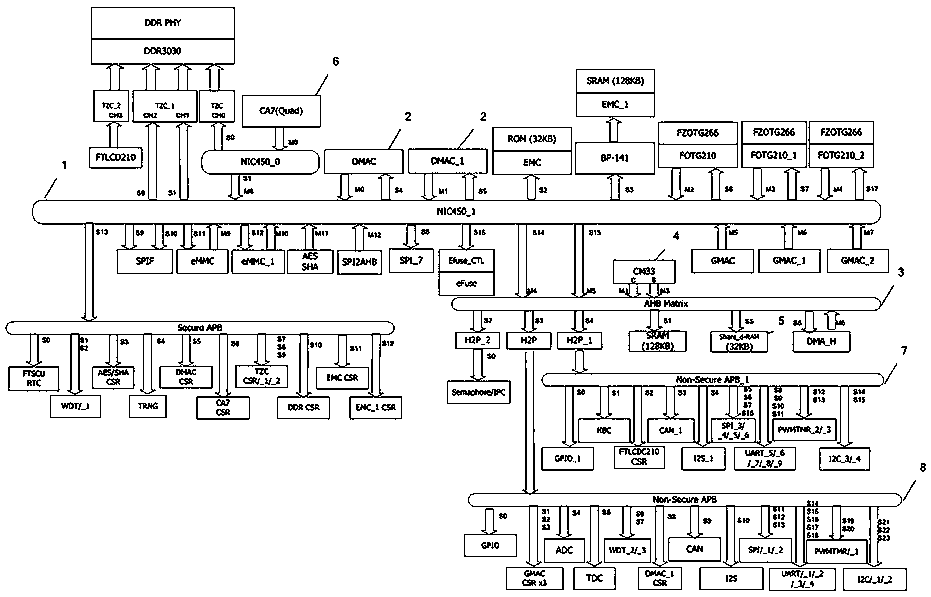

[0024] see image 3 , which shows a schematic structural diagram of a heterogeneous multi-core processor for bus device connection adjustment provided by an embodiment of the present application. The heterogeneous multi-core processor for bus device connection adjustment provided by an embodiment of the present application may include an architecture bus 1. The bus device 2 connected to the architecture bus 1, the first communication bus 3 connected to the architecture bus 1, the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More