A low-voltage multifunctional charge-trapping synaptic transistor and its preparation method

A technology of charge trapping and transistors, applied in the field of charge trapping synaptic transistors, which can solve the problems of high operating voltage, single function, and undeveloped synaptic transistors, and achieve the effect of enhancing the interface electric field and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be described in detail below through specific examples in conjunction with the accompanying drawings.

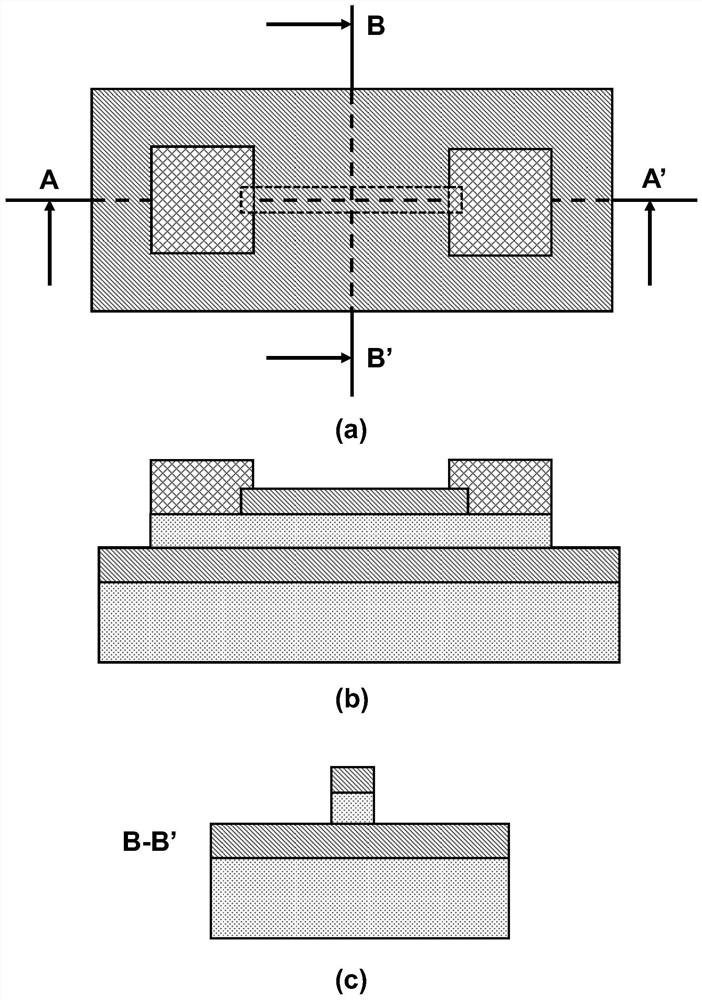

[0043] Such as Figure 1 to Figure 8 As shown, a low-voltage multifunctional charge-trapping synaptic transistor was fabricated according to the following steps:

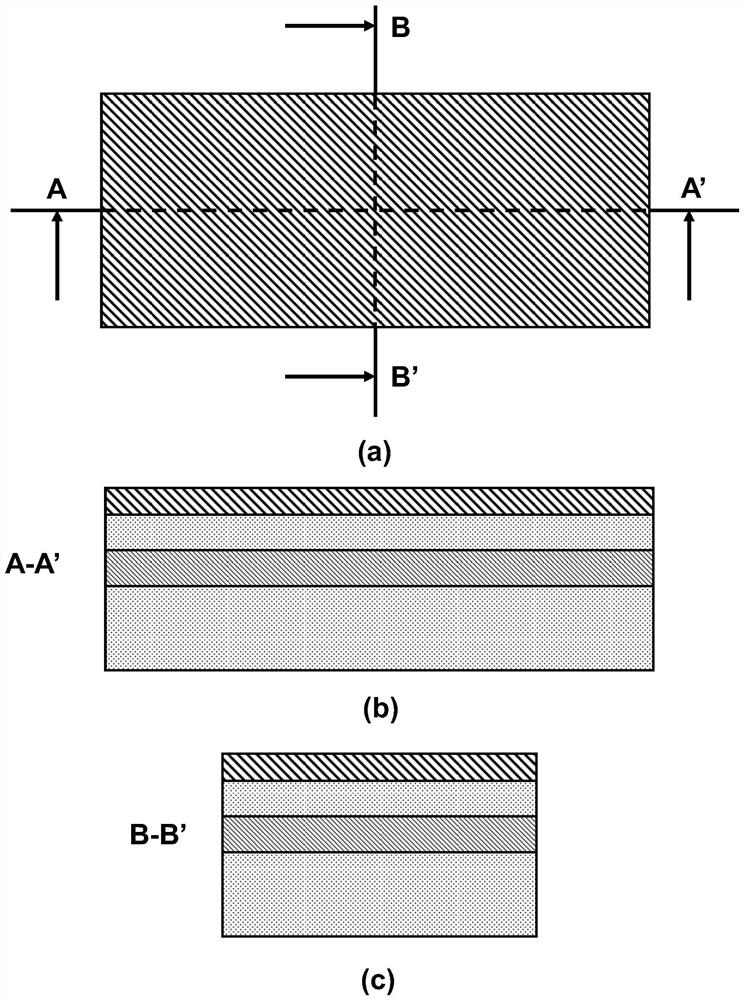

[0044] 1) Thinning the silicon film of the SOI substrate, the specific operation method is dry oxygen oxidation or hydrogen-oxygen synthesis to oxidize the surface silicon film to form a silicon oxide film, and then rinse the surface silicon oxide film with hydrofluoric acid solution, and then spin Coated with HSQ electron beam glue, such as figure 1 shown. It is also possible to use a bulk silicon substrate, and then deposit a silicon oxide film and a polysilicon film in sequence to form an SOI substrate.

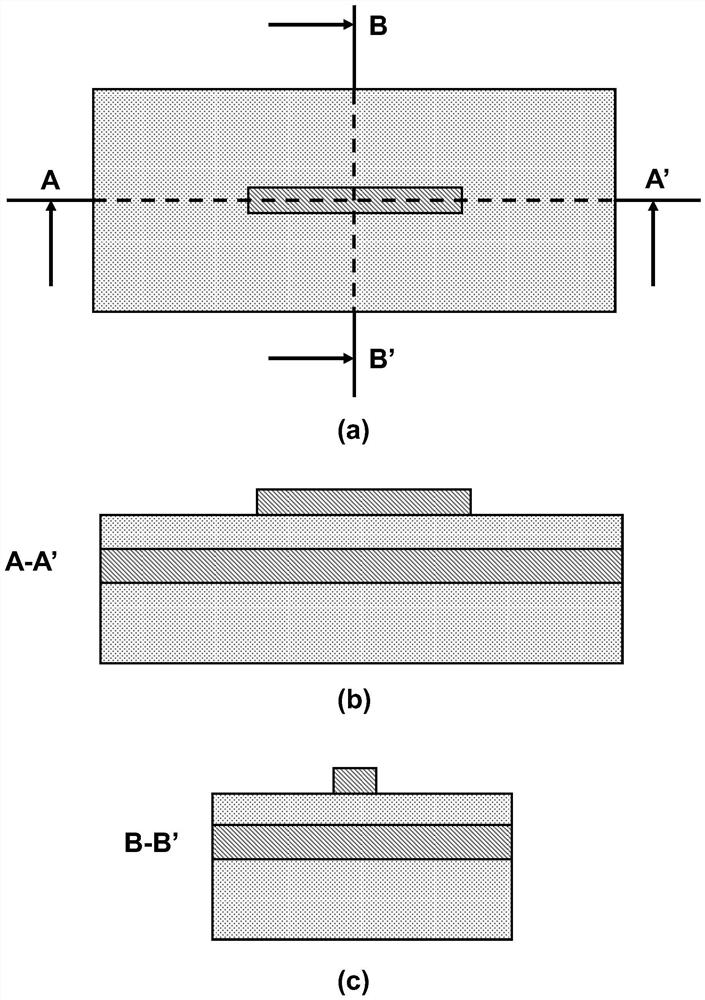

[0045] 2) Using electron beam lithography to define the nanowire mask, the width of the nanowire mask is the line width of the subsequent silicon nanowires, such as figu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More