Memory and forming method thereof

A memory and bit line technology, applied in the field of memory and its formation, can solve problems such as difficulty in balancing, and achieve the effect of increasing the size of the bottom and improving the transmission performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

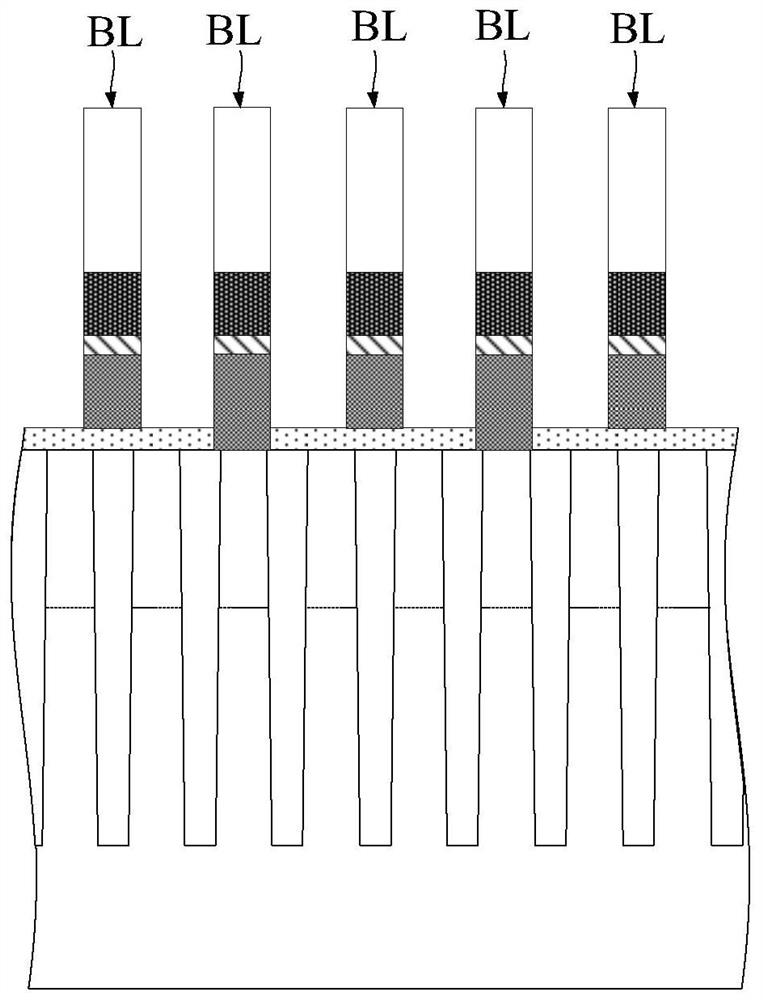

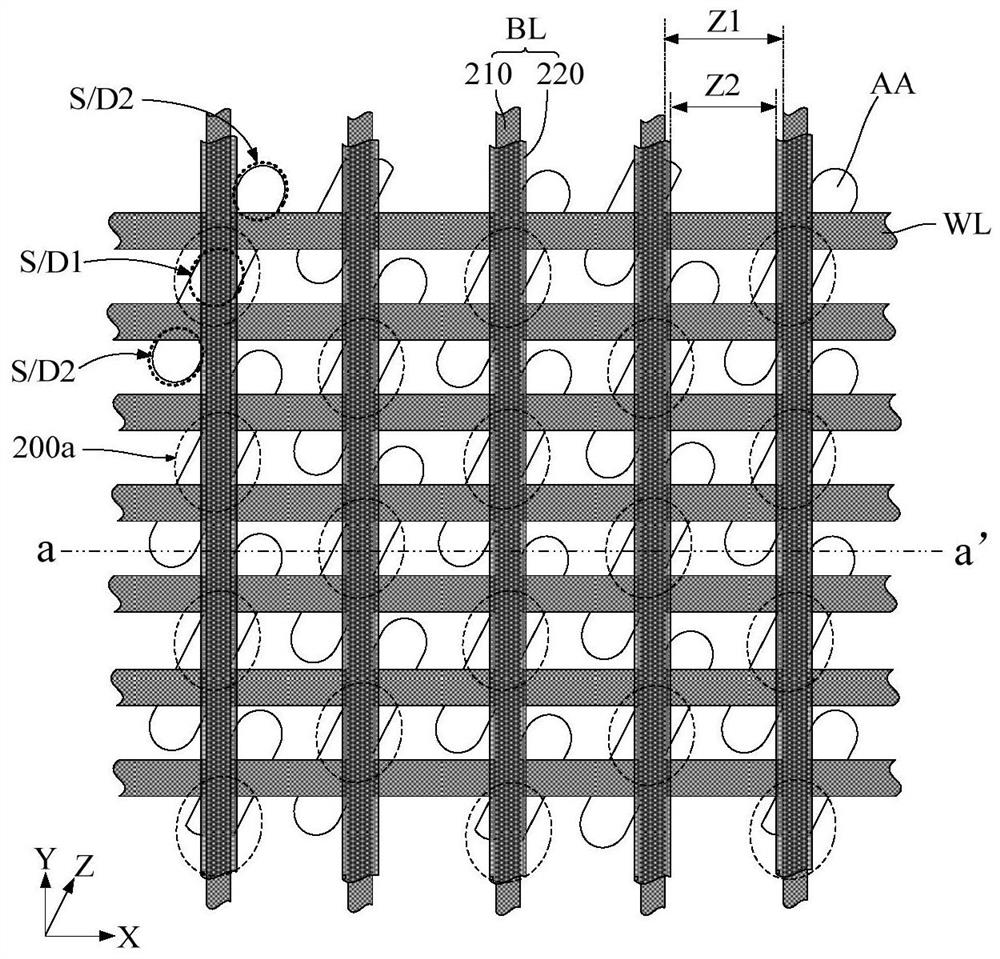

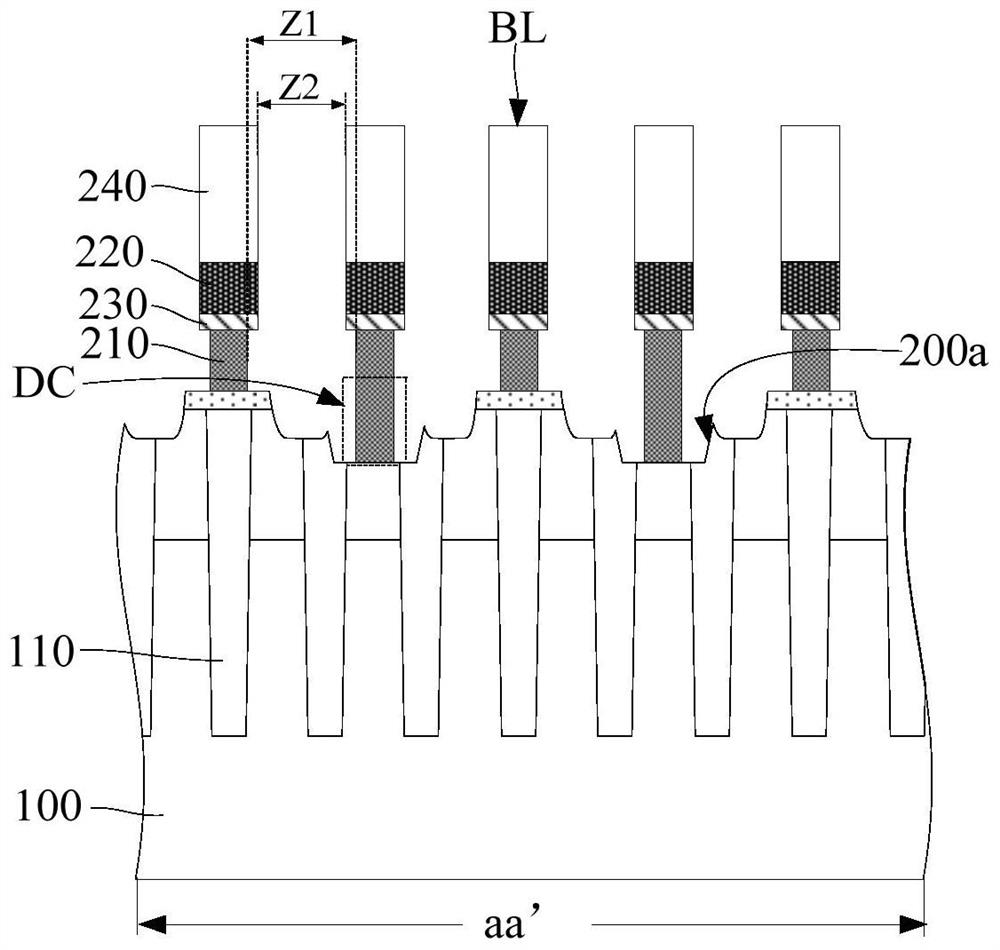

[0056] Figure 2a is a memory in Embodiment 1 of the present invention, which shows a top view of a bit line, Figure 2b for Figure 2a Shown is a schematic cross-sectional view of the memory in Embodiment 1 of the present invention along the aa' direction. It should be noted that, in order to illustrate the memory structure in this embodiment more clearly, Figure 2a The illustration of some components is omitted in , for example Figure 2a The substrate and part of the insulating layer etc. are not shown in the figure.

[0057] combine Figure 2a and Figure 2bAs shown, in this embodiment, the memory includes a substrate 100 and a bit line BL formed on the substrate 100, the bit line BL has a first conductive layer 210 and a second conductive layer 220, and the The width dimension of the first conductive layer 210 is smaller than the width dimension of the second conductive layer 220 above it.

[0058] Specifically, a plurality of active regions AA are formed in the s...

Embodiment 2

[0168] The difference from Embodiment 1 is that in the method for forming the memory of this embodiment, when performing the first etching process, the first etching process includes sequentially etching the second conductive material layer and the first conductive material layer, the side boundary of the first conductive material layer after the first etching process is flush with the side boundary of the second conductive layer; then, in the second etching process, the etchant only The sidewall of the first conductive material layer is etched downward to further reduce the size of the first conductive material layer laterally, so that the size of the formed first conductive layer is smaller than the size of the second conductive layer.

[0169] Figure 14 It is a schematic structural diagram of the formation method of the memory in Embodiment 2 of the present invention after the first etching process is performed.

[0170] specific reference Figure 14 As shown, when perform...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More