Efficient test method based on hierarchical test vectors

A technology of test vectors and test methods, which is applied in the direction of measuring electricity, measuring devices, and measuring electrical variables, etc., can solve problems such as low efficiency, many internal connections, and complex structures, so as to reduce the number, speed up the test speed, and improve the test efficiency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

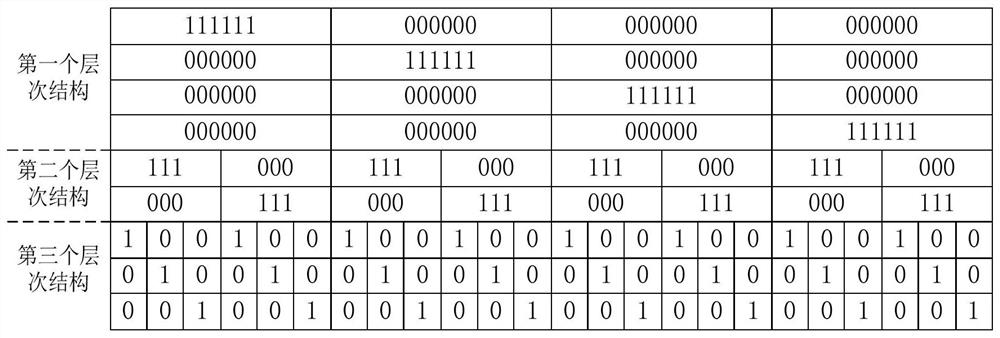

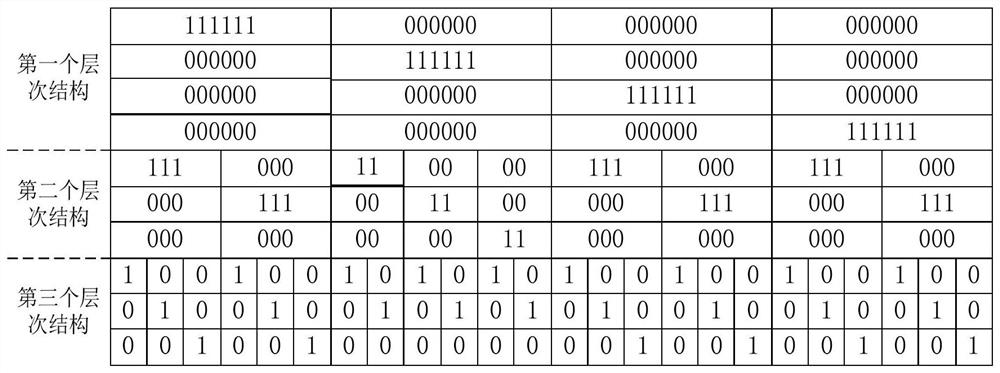

[0027] This application provides a high-efficiency testing method based on hierarchical test vectors, which is based on a stimulus generation circuit (TPG) to generate hierarchical test vectors to test the interconnection path to be tested, which is different from the conventional walking-1 algorithm. Test vectors, this kind of hierarchical test vectors can reduce the test vectors on the basis of ensuring 100% test coverage to speed up the test speed and improve the test efficiency. The method of this application is:

[0028]1. The interconnection paths to be tested are divided into layers according to the circuit structure to which the interconnection paths to be tested belong, and all the interconnection paths to be tested form K different hierarchical structures, K≥2. Each hierarchical structure includes several parallel structural units,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More