Method for real-time full duplex reliable communication between MCU and multiple FPGAs by using SPIs

A full-duplex, reliable technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problem that the communication speed between MCU and FPGA has not been effectively improved, real-time and reliable transmission of variable-length data cannot be performed reliably, full-duplex and bus are not fully utilized, etc. problem, to achieve the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

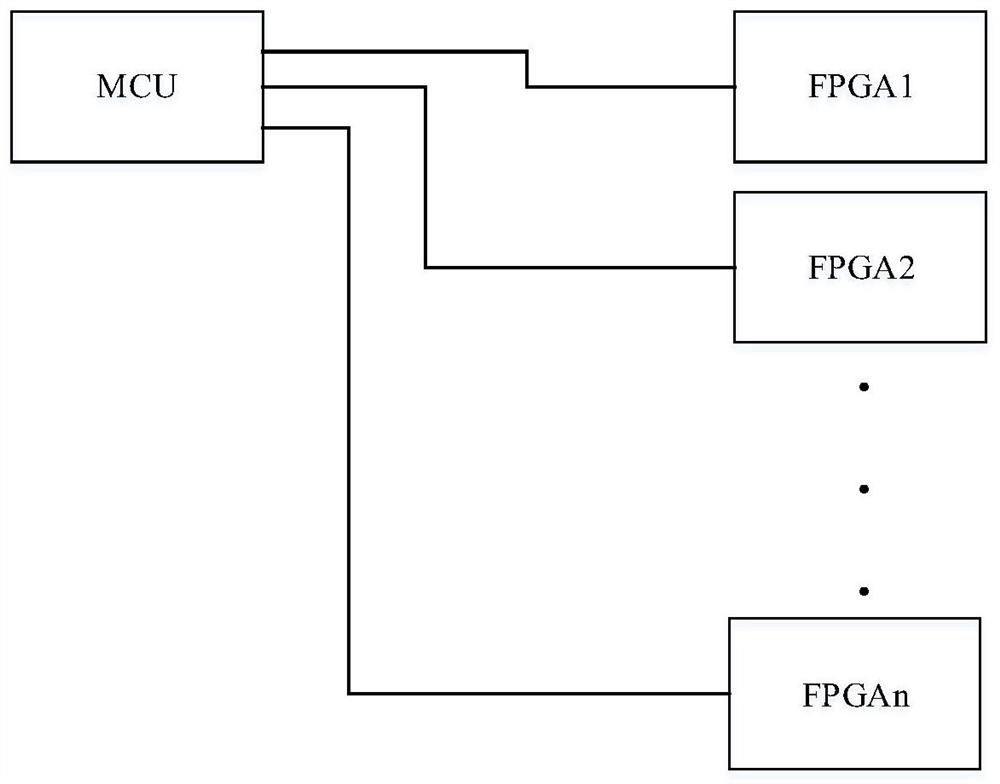

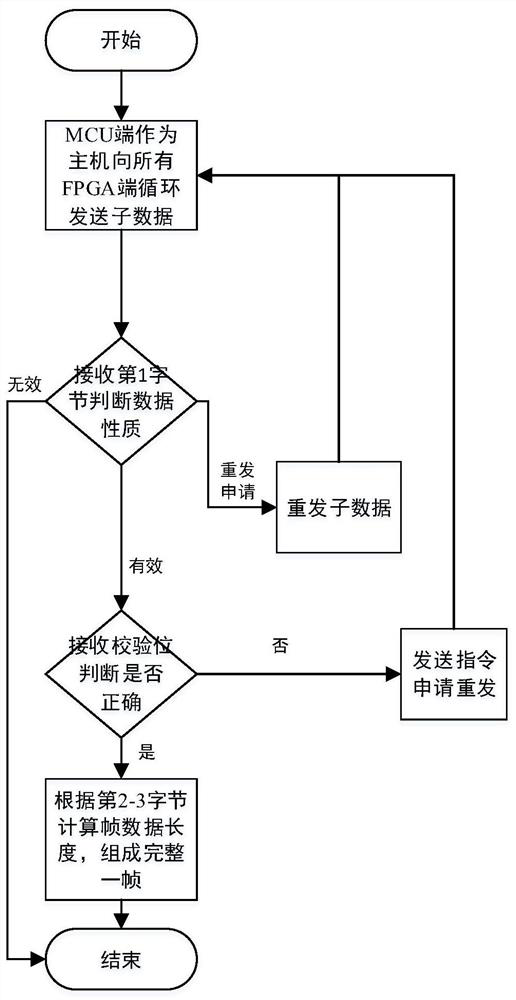

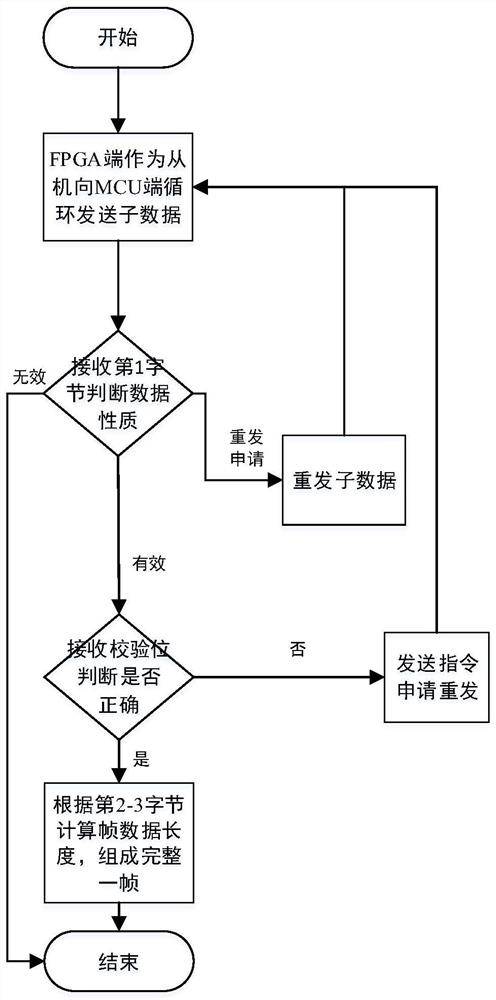

[0046] A kind of MCU provided by the present invention uses SPI to carry out the method for real-time full-duplex reliable communication with a plurality of FPGAs, MCU is connected with a plurality of FPGAs, such as figure 1 As shown, the MCU is the host, the FPGA is the slave, and the MCU communicates with multiple FPGAs using SPI.

[0047] The clock phase (CPHA) and clock polarity (CPOL) of SPI can be 0 or 1 respectively, and the corresponding four combinations constitute the four modes of SPI, which are:

[0048] Mode 0: CPOL=0, CPHA=0;

[0049] Mode 1: CPOL=0, CPHA=1;

[0050] Mode 2: CPOL=1, CPHA=0;

[0051] Mode 3: CPOL=1, CPHA=1.

[0052] Clock polarity CPOL, that is, the level of the clock signal SCLK when the SPI is idle (1: high level when idle; 0: low level when idle);

[0053] Clock phase CPHA, that is, on which edge of SCLK ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com