Vector matrix arithmetic unit in memristor memory and arithmetic method

A vector matrix and operation method technology, applied in the field of analog circuits, can solve problems such as the inability to calculate high-precision floating-point numbers, and achieve the effect of relatively small circuit area overhead, small circuit area overhead, and small array area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

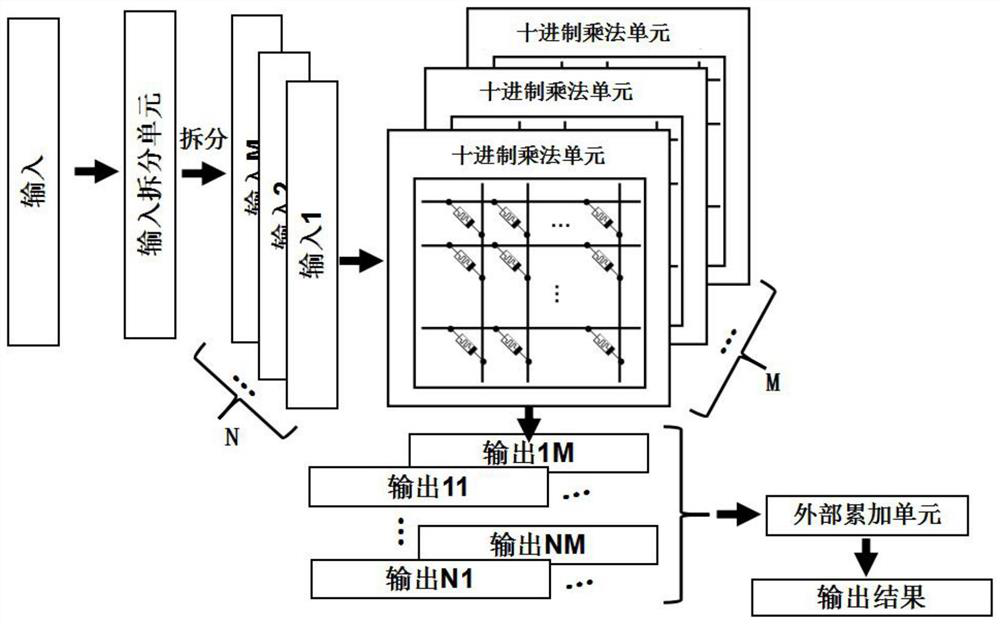

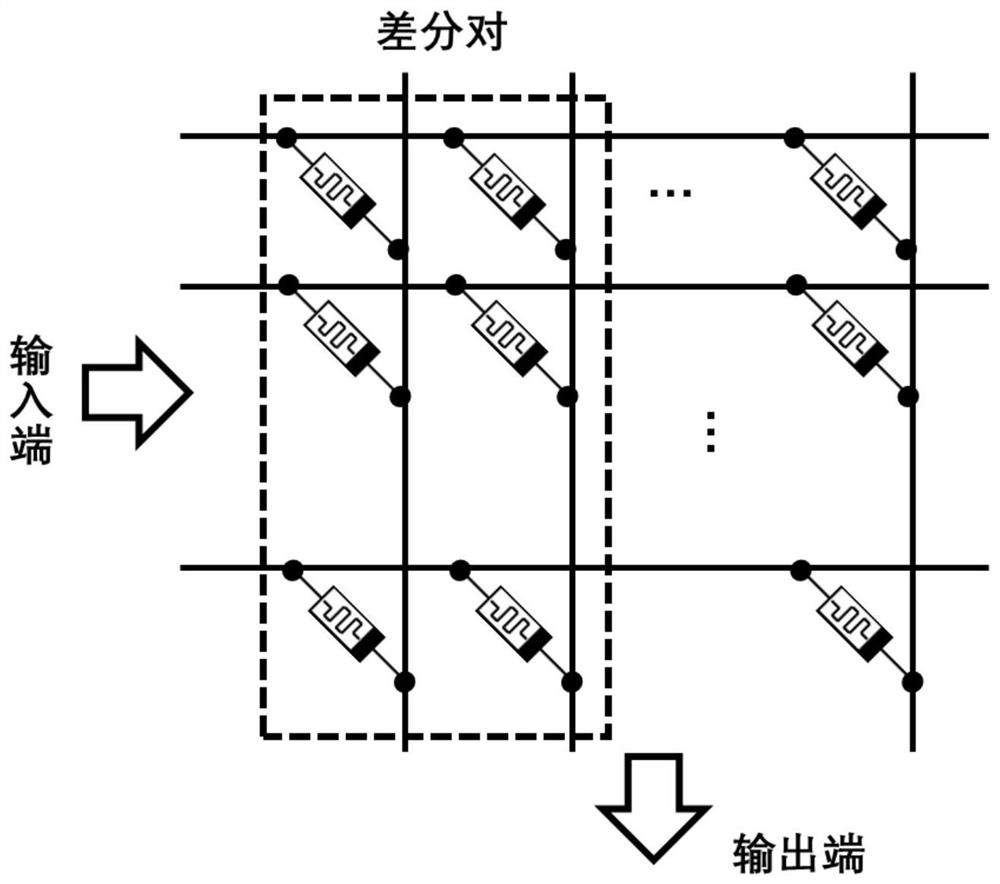

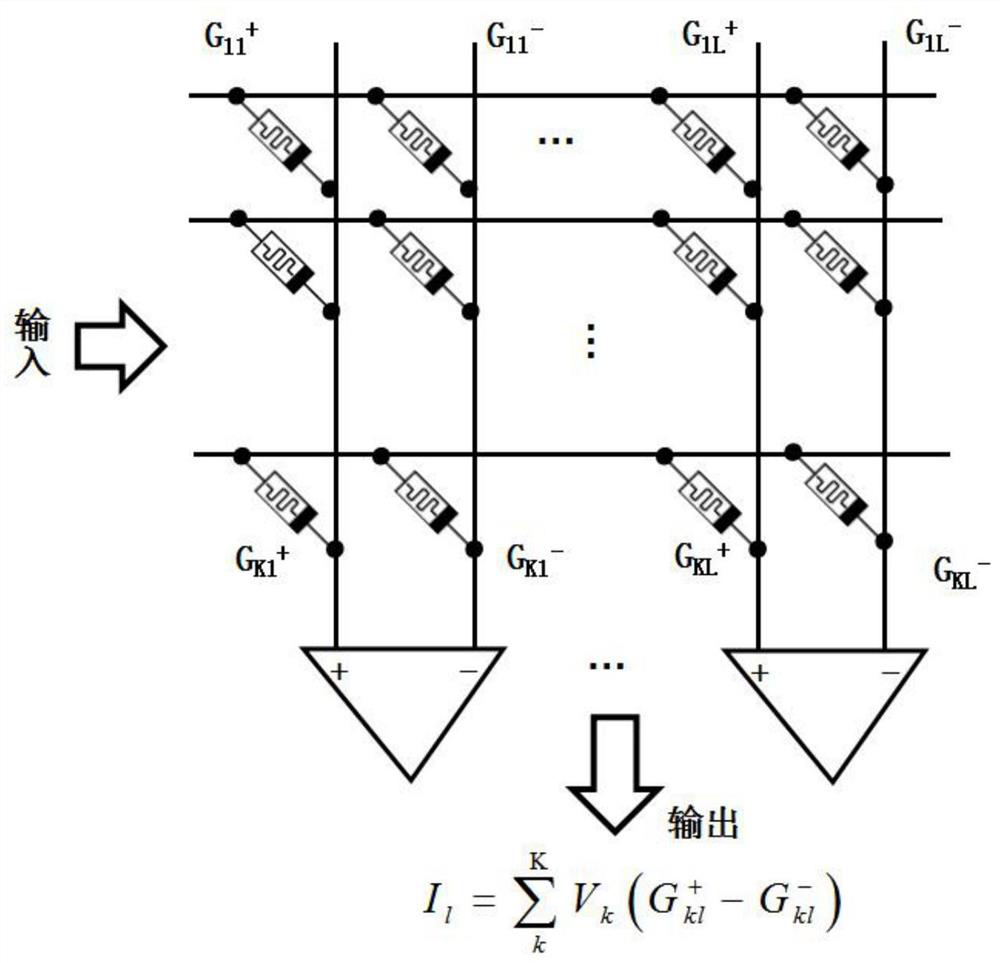

[0041] A vector-matrix operator in a memristive memory, such as figure 1 As shown, it includes: an input split unit, a decimal multiplication unit and an external accumulation unit; wherein, there are M decimal multiplication units, and all of them include a memristor array; each decimal multiplication unit is connected in parallel, and the output terminals of the input split unit are respectively It is connected with the input end of each decimal multiplication unit, and the output end of each decimal multiplication unit is connected with the input end of the external accumulation unit;

[0042] The input splitting unit is used to unify the floating-point digits in the input floating-point number vector and the floating-point number matrix respectively and split them bit by bit to obtain N decimal vectors and M decimal matrices; the M decimal matrices are respectively After being written into the memristor arrays of M decimal multiplication units, each decimal vector is seque...

Embodiment 2

[0046] A kind of memristive memory vector matrix operation method based on the memristive memory vector matrix operator provided in embodiment 1, such as Figure 5 shown, including the following steps:

[0047] S1. After unifying the digits of each floating-point number in the input floating-point number matrix, split them bit by bit to obtain M decimal matrices, and write them into M memristor arrays respectively;

[0048] Specifically, the memristor array in this embodiment is the same as that in Embodiment 1, and will not be repeated here. According to the corresponding method in Embodiment 1, the digits of each floating-point number in the floating-point number matrix are unified into M bits, and then divided bit by bit. Take the number of digits before the decimal point as 1 (that is, the highest digit is the ones digit) as an example, such as Image 6 As shown, the floating-point number matrix after unifying the number of digits Each floating-point number in is split...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More