Storage device and data processing method for real-time processing-oriented multi-core processor

A storage device and data processing technology, applied in the direction of electrical digital data processing, memory systems, instruments, etc., can solve problems such as large access delays, differences, and lower system efficiency, so as to improve efficiency, improve real-time performance, and ensure time determination sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

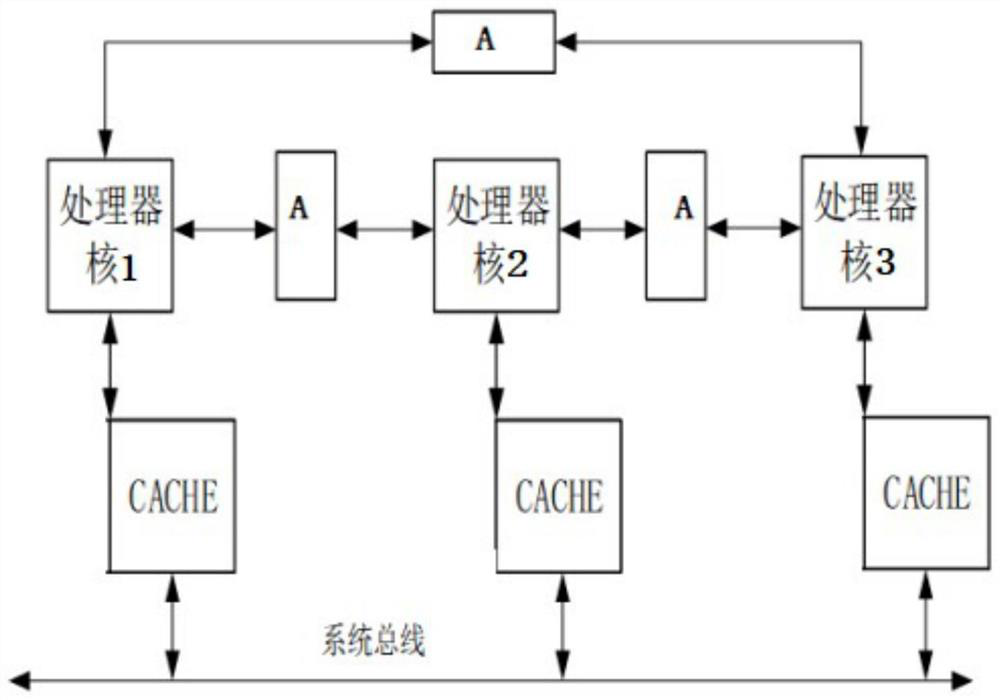

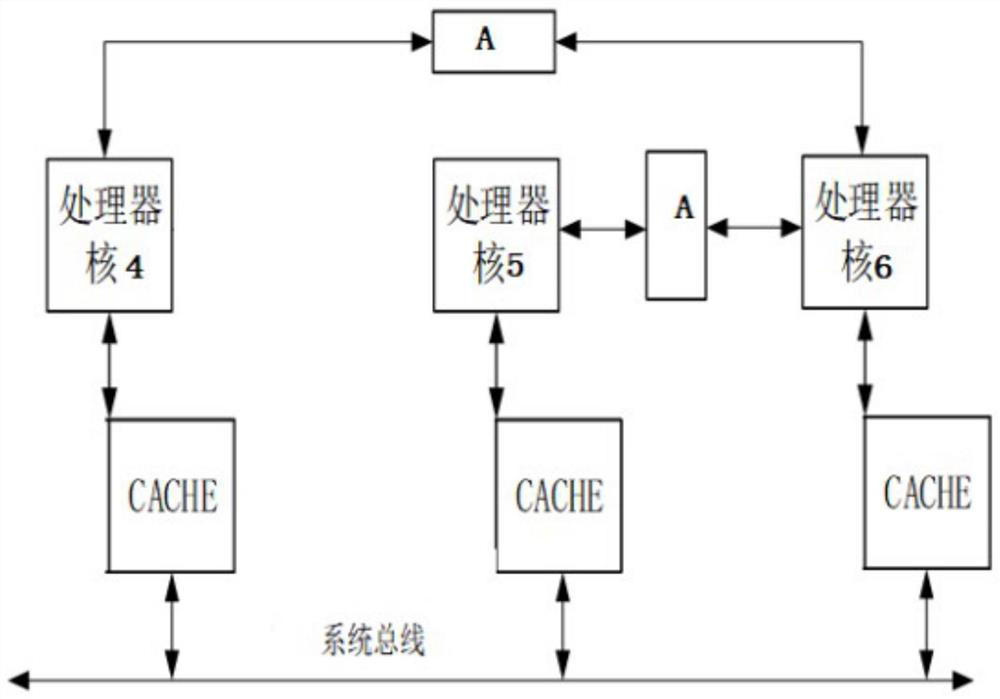

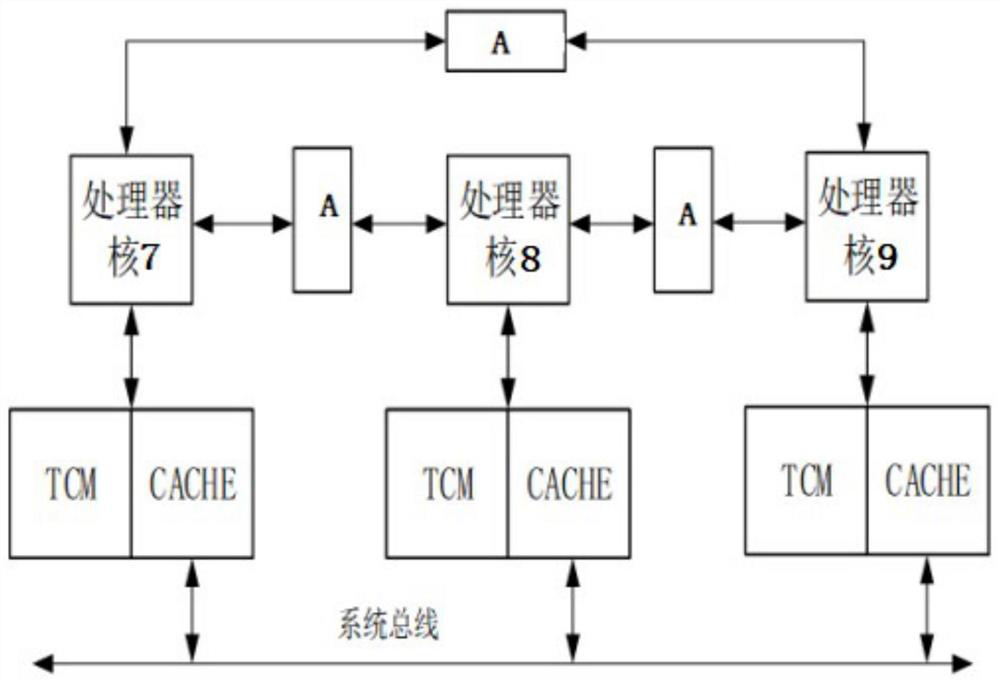

[0073] The storage device for multi-core processors oriented to real-time processing in this embodiment includes: at least one pipeline memory, N first processing units, and a system bus. Wherein, N is greater than or equal to 2; the N first processing units are respectively connected to the system bus. The first processing unit includes: a first processor core and CACHEs respectively connected to the first processor cores. The first processing unit is connected to the system bus through a CACHE; the first processor core is connected to a port of at least one pipeline memory; the pipeline memory is a dual-port memory. The two ports of the pipeline memory are respectively connected to the data ports of the two first processor cores.

[0074] The pipeline memory in this embodiment is a dual-port memory, which provides a data exchange channel and buffer storage between two processor cores connected to it. The two processor cores connected to the pipeline memory access the pipel...

Embodiment 2

[0102] A data processing method in this embodiment is a data processing method executed by any one of the above storage devices for real-time processing-oriented multi-core processors.

[0103] This embodiment provides a data processing method, including:

[0104] When the first processor core needs to transmit data to the destination processor core, the data is written into the pipeline memory between the first processor core and the destination processor core, and the destination processor transfers the data from the Reading the data from the pipeline memory between the first processor core and the destination processor core;

[0105] The target processor core is any first processor core connected to the first processor core.

[0106] For an example, see Figure 7 In the shown storage device for multi-core processors facing real-time processing, when the processor core 21 needs to transmit data to the processor core 22, the processor core 21 directly writes the data into t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More