UVM-based RFID tag chip verification device

An RFID tag and verification device technology, applied in the field of digital system verification of tag chips, can solve a large number of directional excitation, low verification efficiency and other problems, and achieve the effect of convenient injection error frame mechanism, solving verification sufficiency, and flexible platform construction.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

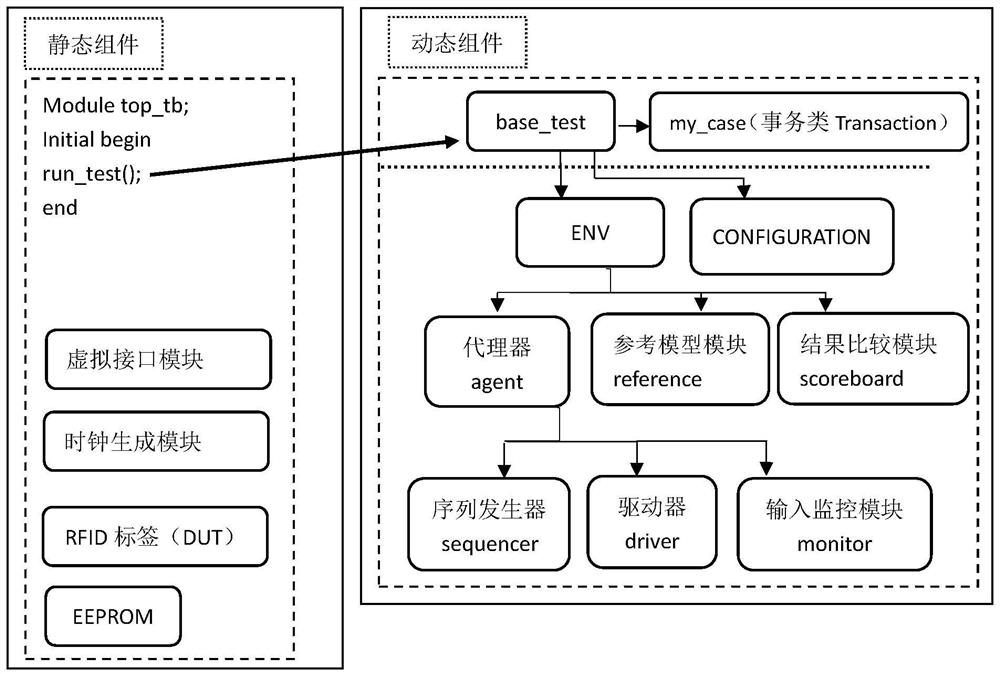

[0039] In order to make the purpose, technical solution and advantages of the present invention clearer, based on the ISO / IEC 15693 protocol, the present invention will be further described in detail in combination with the accompanying drawings and examples. The specific examples described here are only used to explain the present invention, not to limit the present invention.

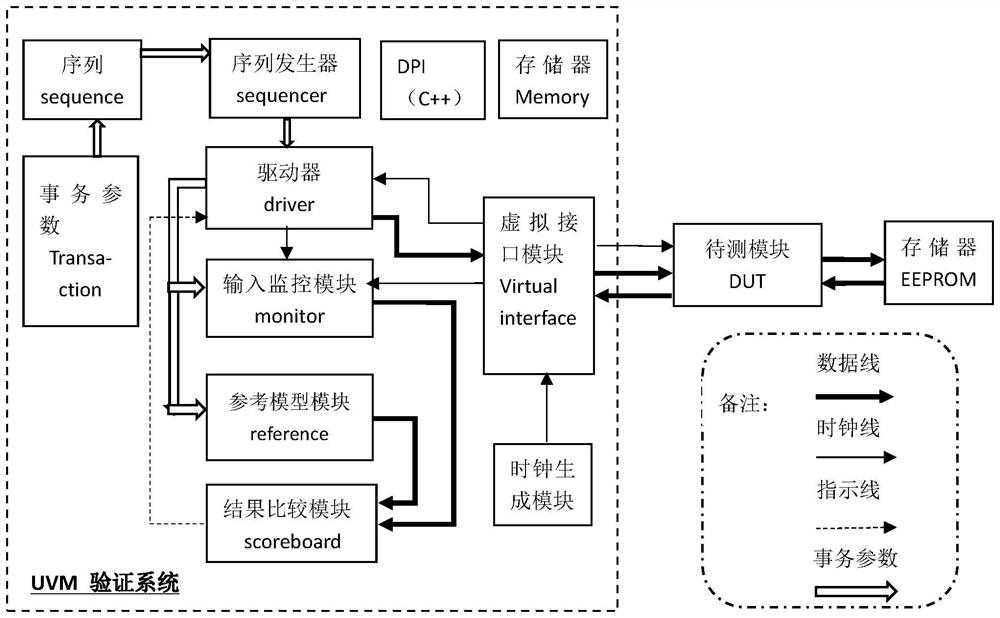

[0040] Such as figure 2 As shown, the clock generating module generates a clock (13.56Mhz) and sends it to the virtual interface module (virtualinterface). In verifying the top-level module (top_tb.sv), the clock in the virtual interface module is connected to the clock input terminal of the DUT top-level. The driver (driver) and the input monitoring module (monitor) can call the clock signal in the virtual interface module.

[0041] Such as figure 2 As shown, the test case generates the required transaction class (Transaction), which includes parameters required for framing such as vcd2vicc_data_c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More