Method for dynamically modifying PCH PCIE root port where onboard VGA is located

A root port, onboard technology, applied in the computer field, can solve the problem that the onboard VGAPCHPCIE root port cannot be dynamically modified

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

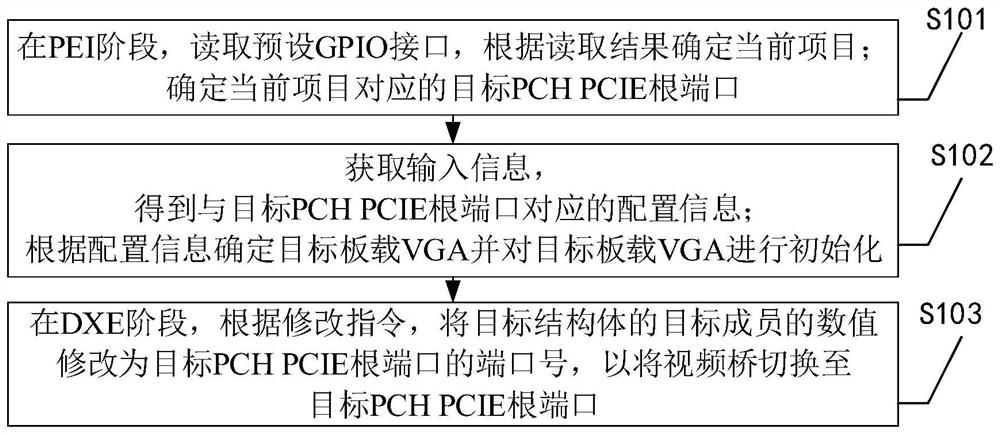

[0044] The following introduces a method embodiment one of a method for dynamically modifying the PCH PCIE root port where the onboard VGA is provided by the application, see figure 1 , embodiment one includes:

[0045] S101. In the PEI stage, read the preset GPIO interface, and determine the current project according to the reading result; determine the target PCH PCIE root port corresponding to the current project;

[0046] When designing the motherboard, reserve several GPIO interfaces. When the motherboard is powered on, it enters the PEI stage (Pre-EFINitialization, EFI pre-initialization stage), and determines the currently started project by reading these GPIO interfaces, and then determines the PCH PCIE root port used by the project.

[0047] Specifically, a project ID is set for each project of the current platform; at the PEI stage, the preset GPIO interface is read to obtain the reading result; the project whose project ID is the reading result is determined as the...

Embodiment 2

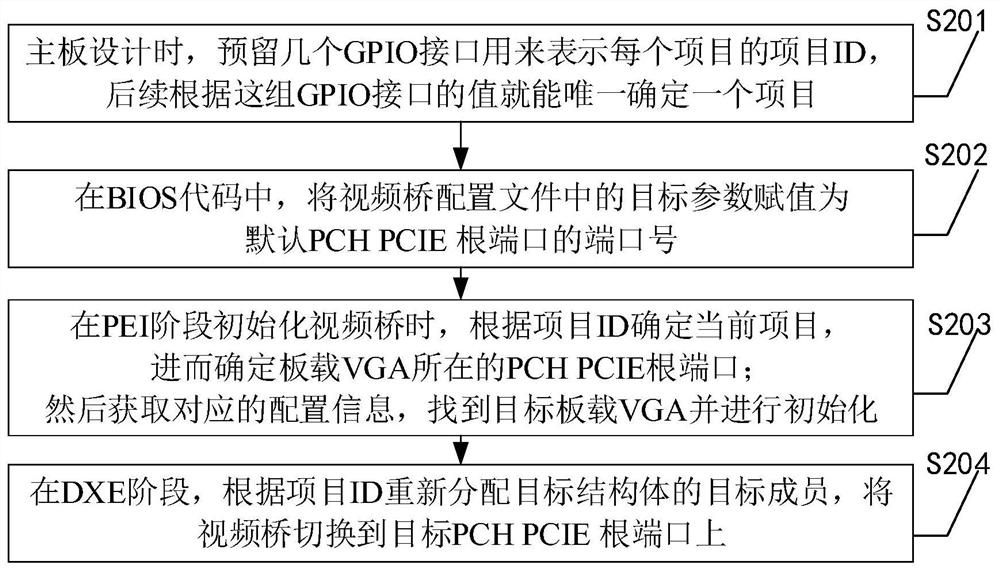

[0055] The following begins to introduce in detail the second embodiment of a method for dynamically modifying the PCH PCIE root port where the onboard VGA is located, see figure 2 , embodiment two specifically includes:

[0056] S201. When designing the motherboard, several GPIO interfaces are reserved to represent the project ID of each project, and a project can be uniquely determined later based on the values of this group of GPIO interfaces.

[0057] Assuming that 8 GPIOs are reserved, when the value of this group of GPIO interfaces is 00000001, it indicates that the currently started project is project 1, and when the value of this group of GPIO interfaces is 00000010, it indicates that the currently started project is project 2.

[0058] S202. In the BIOS code, assign the target parameter in the video bridge configuration file to the port number of the default PCH PCIE root port.

[0059] There are many parameters in the video bridge configuration file, and the targ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More