IO PAD automatic layout method with self-checking function

A self-inspection and layout technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of heavy workload, error-prone, redundant, etc., and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, so that those skilled in the art can better understand the present invention and implement it, but the examples given are not intended to limit the present invention.

[0034] refer to Figure 5 , the present invention a kind of method for the automatic layout of IO PAD with self-inspection function, comprising:

[0035] Step 1: Read and write the filled configuration file.

[0036] Specifically, generating a filled configuration file requires the following steps:

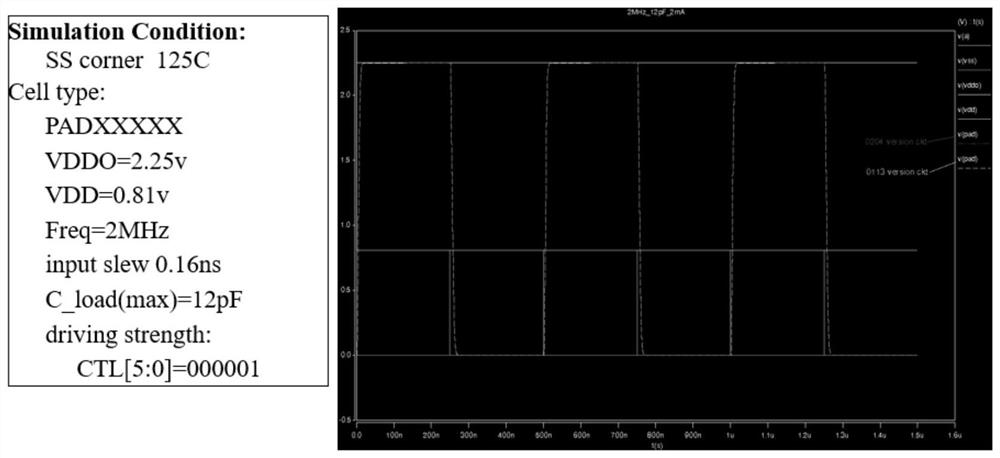

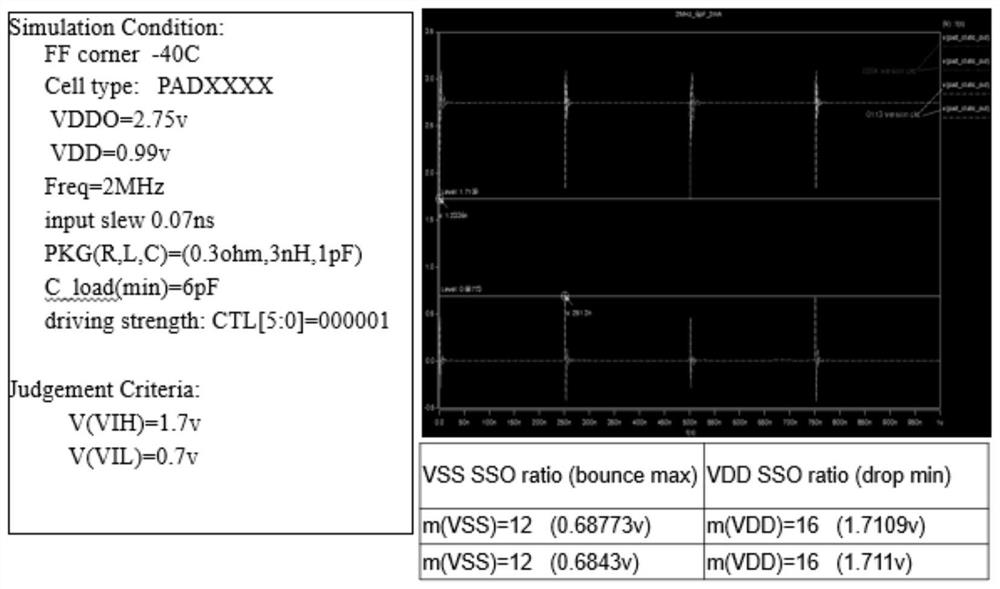

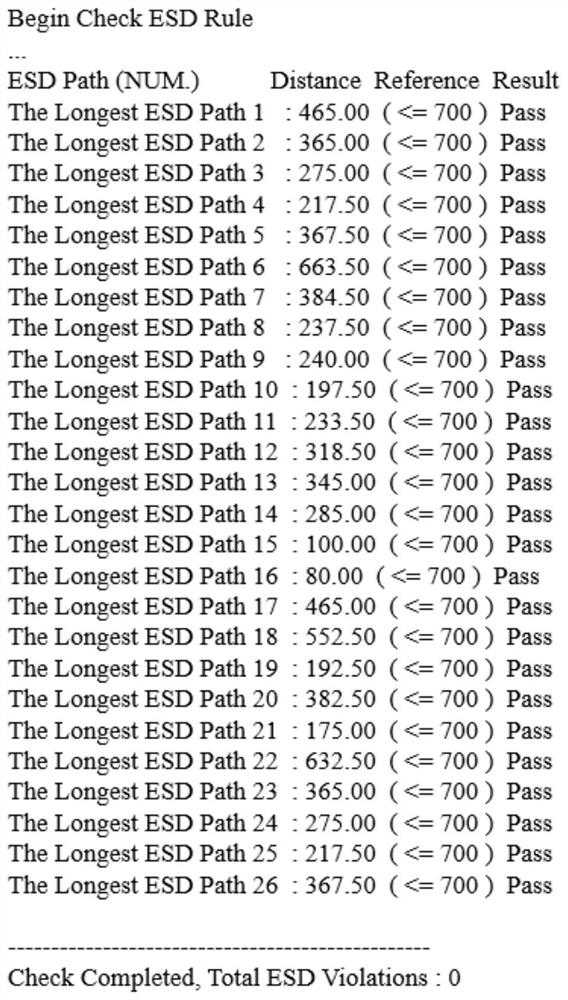

[0037] Before starting the IO PAD layout, you first need to carefully read the relevant documents of the IO PAD used to understand the structure, electrical performance and application rules of the IO PAD. The application rules include ESD and Latch-up; quantify ESD and Latch-up and fill in in the configuration file.

[0038] According to the IO list provided by the front-end desig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More