Military FPGA universal reconstruction circuit based on JTAG interface

A technology for reconstructing circuits and interfaces, applied in the design program of CPLD and FPGA field, can solve problems such as unfavorable on-site debugging, affecting the miniaturization of board-level products, and large interface area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

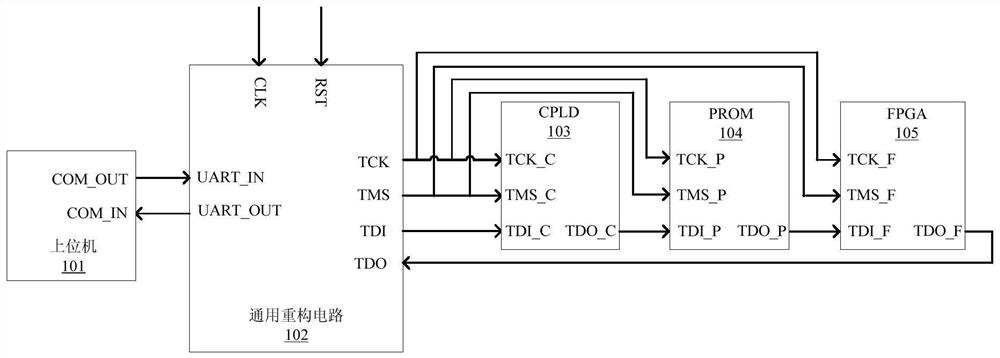

Embodiment 1

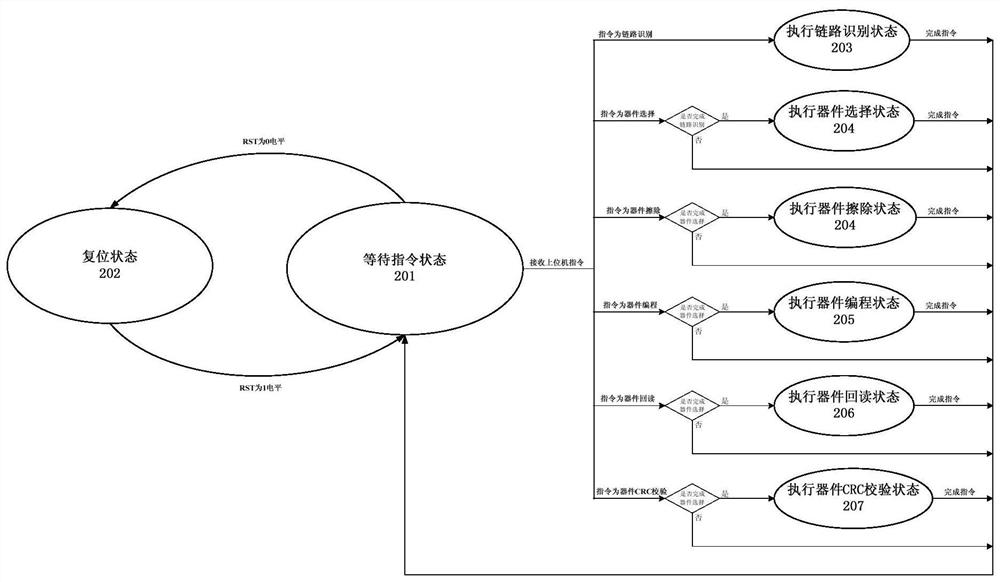

[0124] like image 3 and Figure 4Shown is the implementation flow chart of the reconfiguration circuit of the present invention. The reconfiguration circuit 102 of the present invention includes five working states, including the waiting instruction state 201, the reset state 202, the execution "link identification" state 203, and the execution "device selection" state 204. 1. Execute the "device erasing" state 205, execute the "device programming" state 206, execute the "device readback" state 207, execute the "device CRC check" state 208, the implementation method of the reconfiguration circuit 102 of the present invention is realized by a state machine , the specific implementation process is as follows:

[0125] Step (1), the initial state of the reconfiguration circuit 102 after power-on is a state of waiting for an instruction. In the state of waiting for an instruction, if the RST signal input from the outside through the RST pin is "0" level, it will enter the reset ...

Embodiment 2

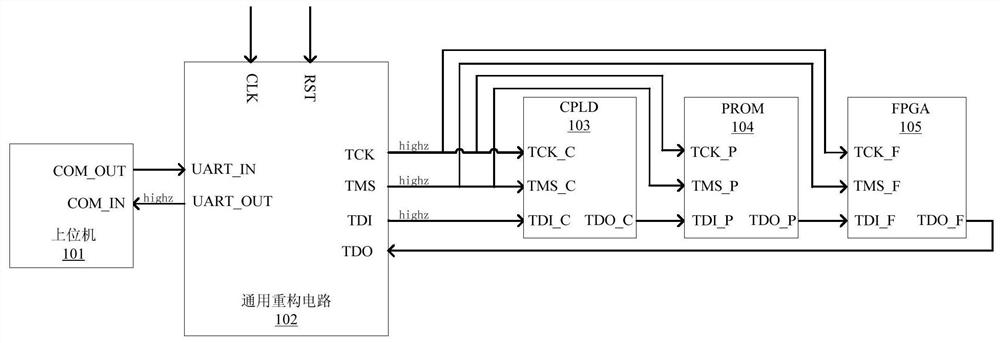

[0134] After power-on, connect the RST pin of the reconfiguration circuit 102 to “0” level, then the reconfiguration circuit 102 suspends its work and enters the reset state 202 . In the reset state, the reconfiguration circuit clears all internal registers, and at the same time outputs the TCK pin, TMS pin, TDI pin, and UART_OUT pin to a high-impedance state. At this time, the reconstruction circuit 102 does not respond to the instructions of the host computer 101 .

Embodiment 3

[0136] After power-on, connect the CLK pin of the reconfiguration circuit 102 to a clock signal with a fixed frequency of 40 MHz, and connect the RST pin to "0" level, and the reconfiguration circuit 102 enters the reset state 202, clears all internal registers, and outputs the Pin high impedance, RST pin is connected to "1" level, the reconstruction circuit enters the waiting command state 201, and starts to receive the command information of the host computer 101 through the UART_IN pin. There are 6 commands of the host computer, which are link identification, Device selection, device erasing, device programming, device readback, device CRC check, the reconfiguration circuit enters the specified state according to the instruction information.

[0137] The instruction received by the reconfiguration circuit for the first time only responds to the "link identification" instruction, and enters the execution link identification state 203. The reconfiguration circuit 102 sends a r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More