A phase-based on-chip bus scheduling device and scheduling method

A scheduling device and phase technology, applied in the direction of comprehensive factory control, instrumentation, calculation, etc., can solve the problems of large bus network area, high power consumption, long bus network delay, etc., to achieve reduced area and power consumption, small response delay, Responsive and timely effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The technical solutions of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

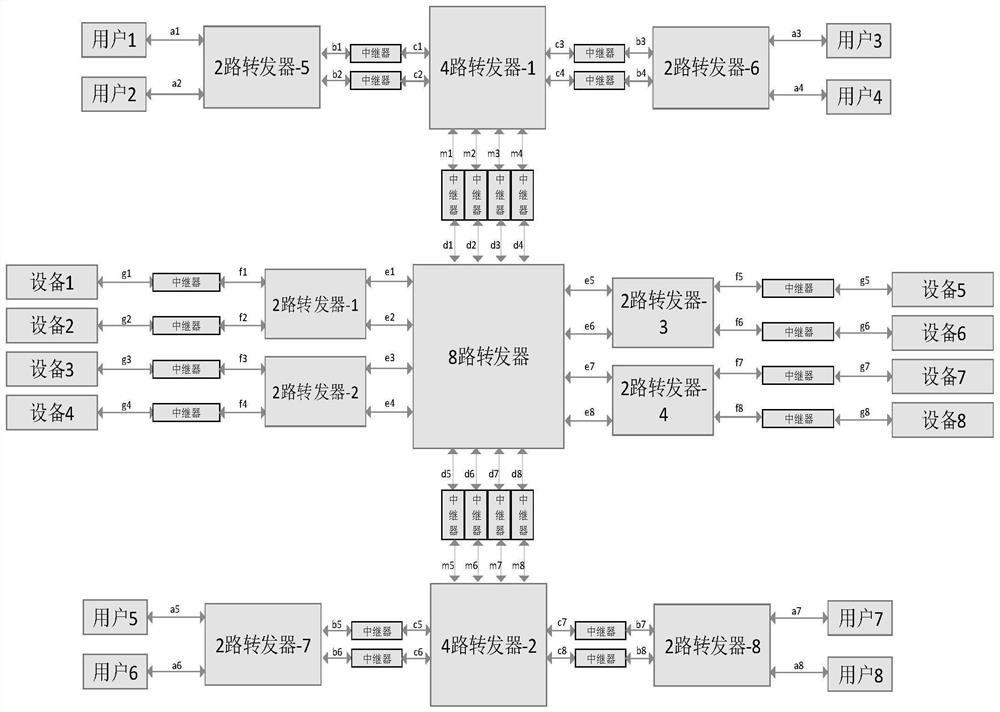

[0020] Such as figure 1 As shown, a phase-based on-chip bus scheduling device includes a phase generator and 1 to N-level transponders, wherein the second-level transponder is connected with two first-level transponders for connecting users, and the second A level 3 transponder has two level 2 transponders connected to it, and so on. A number of first-level repeaters for connecting devices are also connected to the Nth-level repeater, and the number of users or devices connected to each first-level repeater is equal, and the total number of users and devices is equal. The phase generator is used to generate phases and authorize access rights between users and devices.

[0021] In this embodiment, the adjacent level repeaters, the first level repeater and users, and the first level repeater and equipment ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More