Packaging design method and device of semiconductor chip

A design method and semiconductor technology, applied in computer-aided design, calculation, special data processing applications, etc., can solve the problem of large error in chip products and achieve the effect of reducing the error of chip products

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] Exemplary embodiments of the present application are described below in conjunction with the accompanying drawings, which include various details of the embodiments of the present application to facilitate understanding, and they should be regarded as exemplary only. Accordingly, those of ordinary skill in the art will recognize that various changes and modifications of the embodiments described herein can be made without departing from the scope and spirit of the application. Also, descriptions of well-known functions and constructions are omitted in the following description for clarity and conciseness.

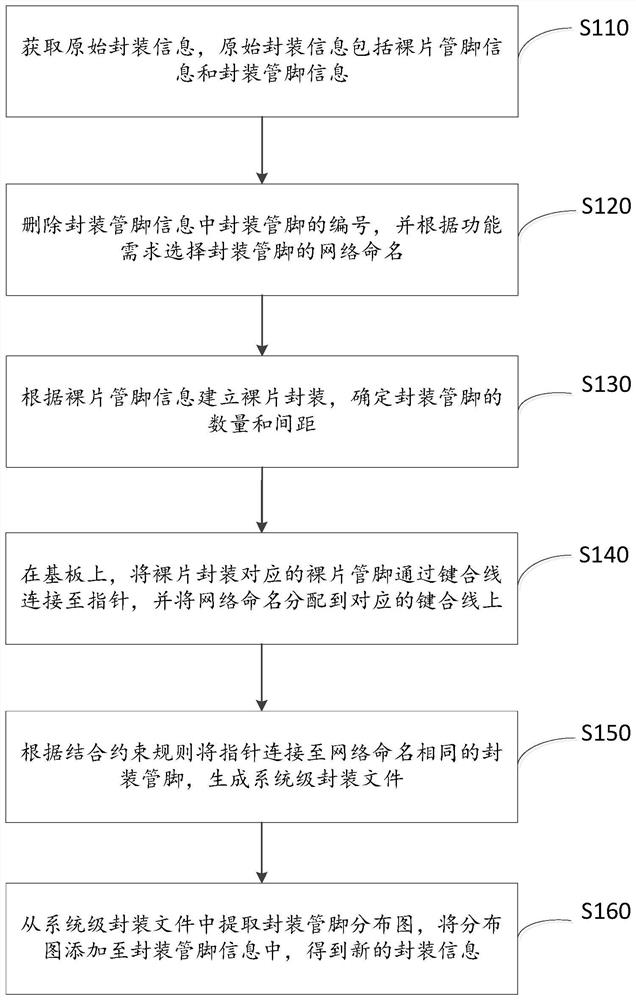

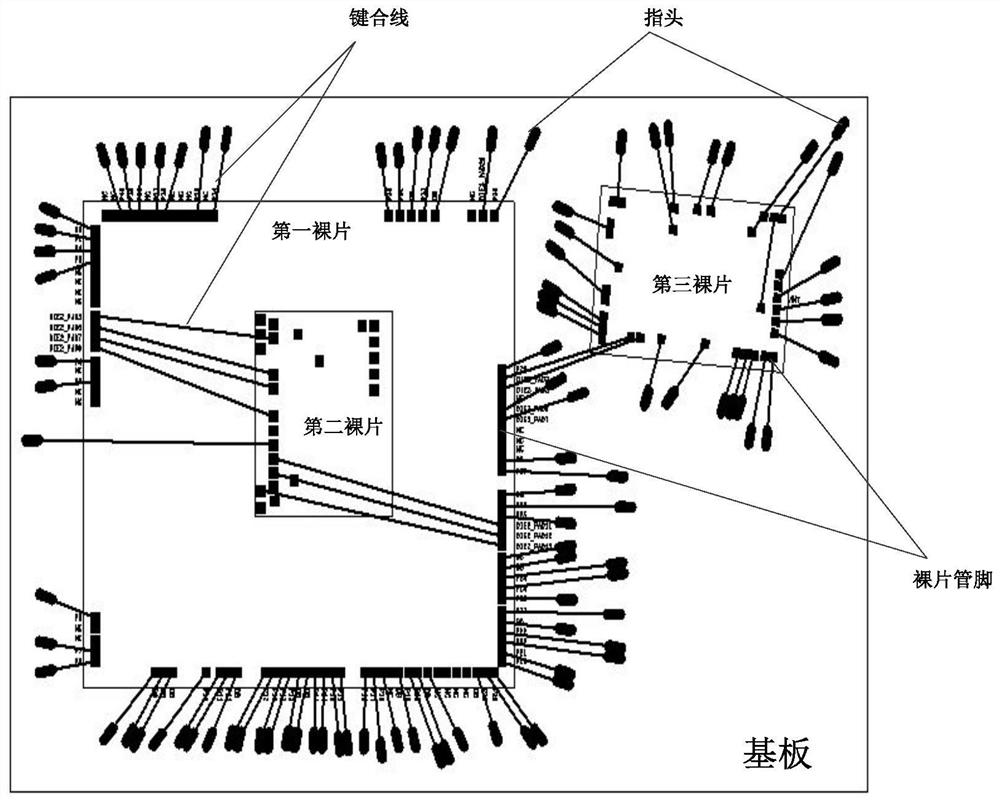

[0058] In a specific embodiment, such as figure 1 As shown, a packaging design method for a semiconductor chip is provided, comprising the steps of:

[0059] Step S110: Acquiring original packaging information, the original packaging information includes bare chip pin information and package pin information;

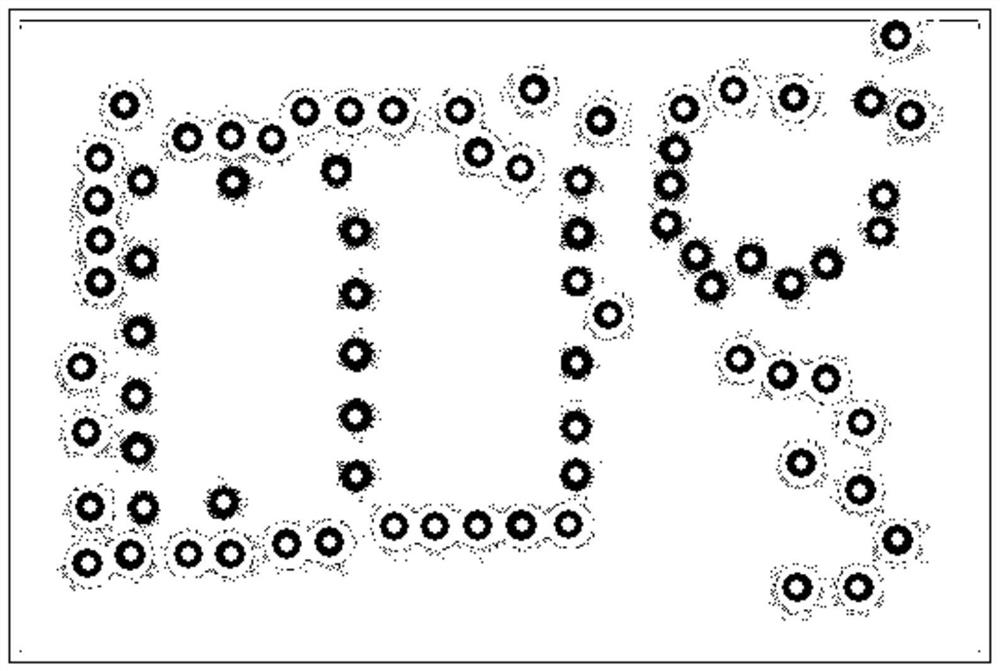

[0060] Step S120: Delete the number of the package pin ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More