Dual-port PCIe SSD link fault tolerance device and method

A dual-port and link technology, which is applied in the field of computer communication, can solve the problems of time-lag data insecurity caused by the error processing of the upper-level business end, and achieve the effect of ensuring safety and realizing switching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

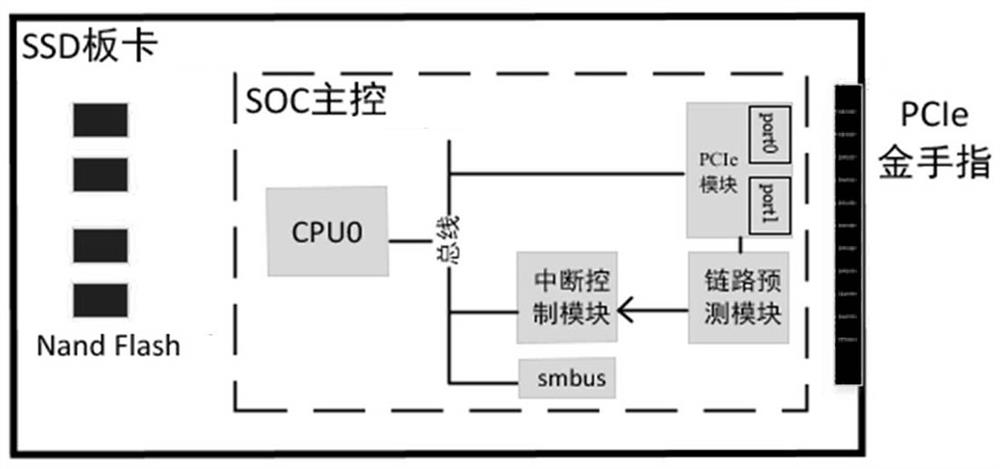

[0025] This embodiment discloses a dual-port PCIe SSD link fault-tolerant device. The device is implemented inside the SSD main control chip to realize active prediction of the SSD link state. Such as figure 1 As shown, the SSD board includes a SOC main control chip, nand flash, and PCIe golden finger interface. The SSD main control chip integrates the dual-port PCIe SSD fault-tolerant device described in this embodiment.

[0026] The dual-port PCIe SSD link fault-tolerant device in this embodiment includes a dual-port enabling unit, a link prediction logic unit, an interrupt control unit, and an smbus master-slave device.

[0027] The dual-port enable unit enables the dual-port mode of PCIe through the configuration register. All data channels are divided into two groups on average, each group is a port, and each group transmits data independently without being affected by the other channel. The effect of multiple hosts accessing the SSD can be realized through the PCIe swi...

Embodiment 2

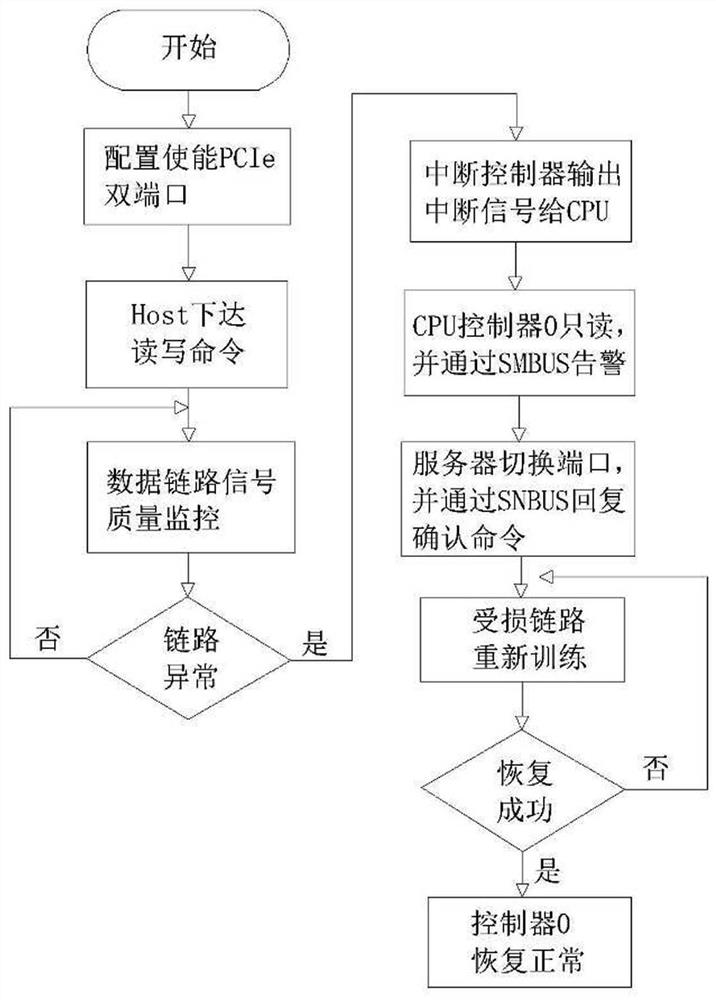

[0034] This embodiment discloses a dual-port PCIe SSD link fault-tolerant method. This method is implemented inside the SSD main control chip to realize active prediction of the SSD link state, such as figure 2 shown, including the following steps:

[0035]S01), the SSD firmware enables the current working mode to be the dual-port mode by configuring the register of the dual-port enabling unit. After the server is inserted, link training and negotiation are performed at both ends of the link to make the SSD work in the dual-port mode;

[0036] S02), during the normal reading and writing process of SSD, the link prediction logic unit is automatically in the running state. When the data packet received by the SSD has an ECRC or LCRC error, the bit error rate error statistics are started. When the bit error rate exceeds the threshold, it is identified as The link is abnormal, and the judgment result is output to the interrupt control unit;

[0037] S03), the interrupt control u...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap