Integrated manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problem of affecting the threshold voltage of P-type semiconductor devices, the thickness limit of P-type metal work function layers, and the influence of thickness on P-type metal Work function layer and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

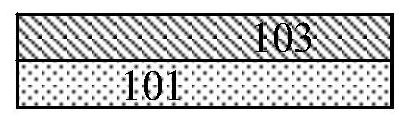

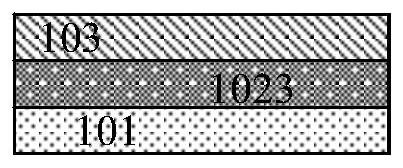

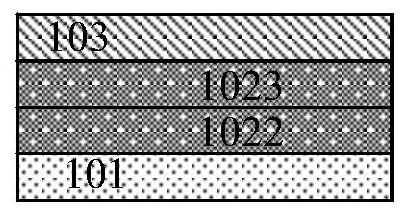

[0066] like Image 6 As shown, it is a flow chart of the integrated manufacturing method of the semiconductor device according to the embodiment of the present invention; in the integrated manufacturing method of the semiconductor device according to the embodiment of the present invention, m kinds of metal work function layers that need to be formed on the semiconductor substrate 301 are integrated. For semiconductor devices, the thickness of the work function layer of the first type of metal decreases gradually from the first type to the mth type of semiconductor device. The steps of forming the first type of metal work function layer with m thicknesses include:

[0067] Step 1. According to the thickness differences of the first-type metal work function layers of various thicknesses, divide the thickest first-type metal work-function layer from bottom to top into the first, second and up to the first m first-type metal work function sublayers.

[0068] Step 2: Perform m c...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap