On-chip cache device and read-write method

An on-chip cache and high-speed cache technology, applied in the field of communication chips, can solve the problems of large chip storage area, waste of storage space, and high power consumption, and achieve the effects of improving utilization, reducing power consumption, and reducing storage area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

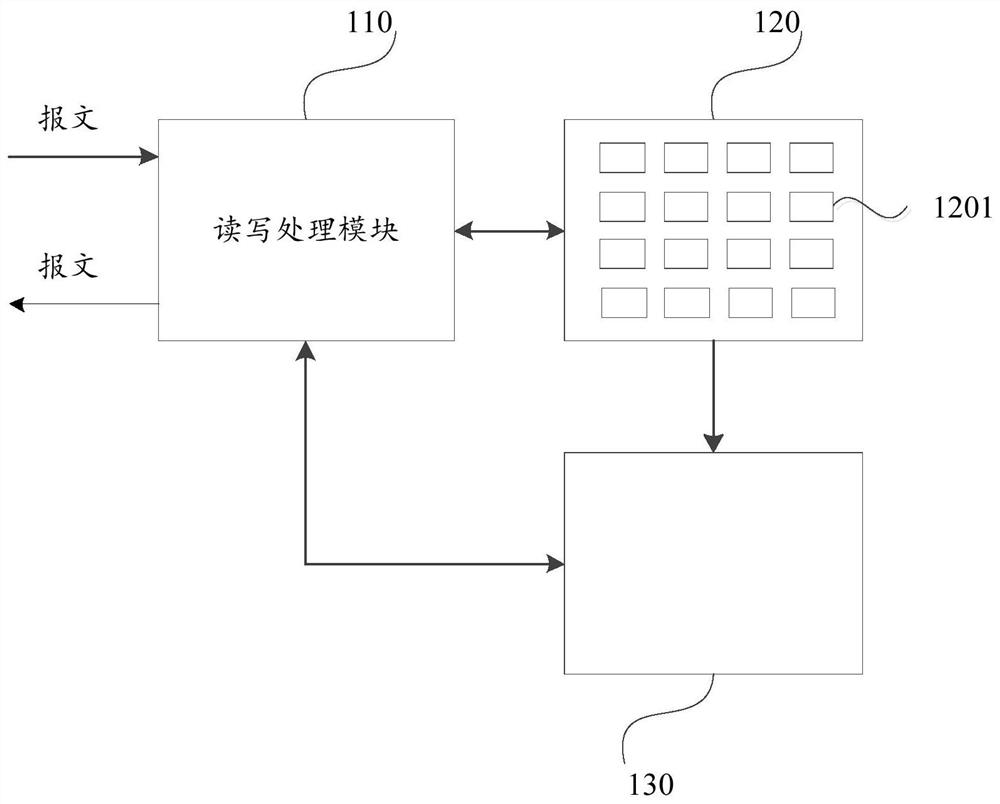

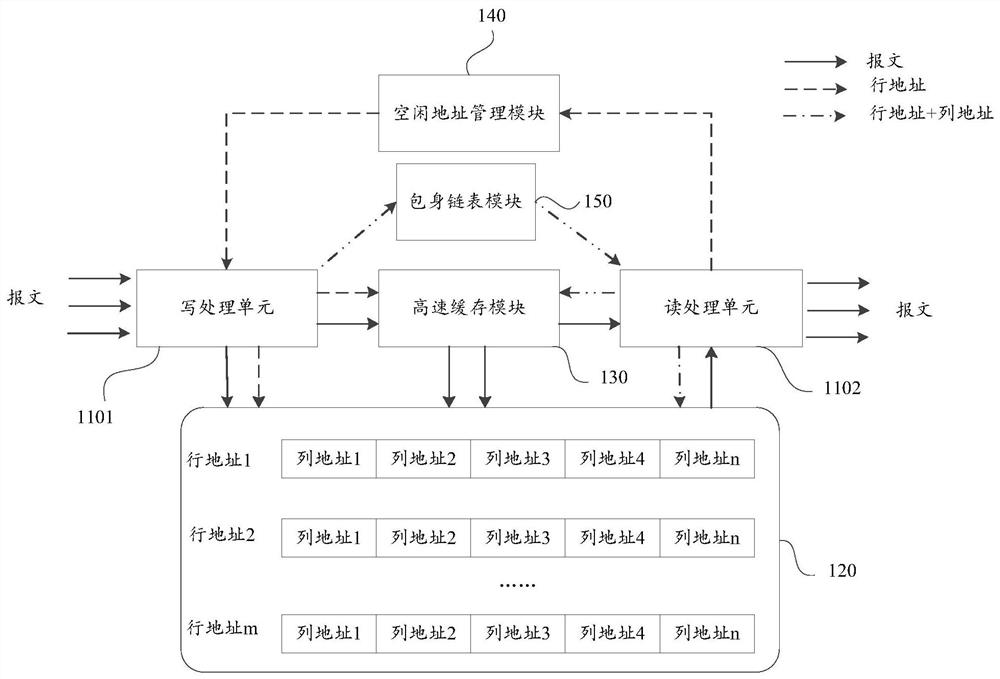

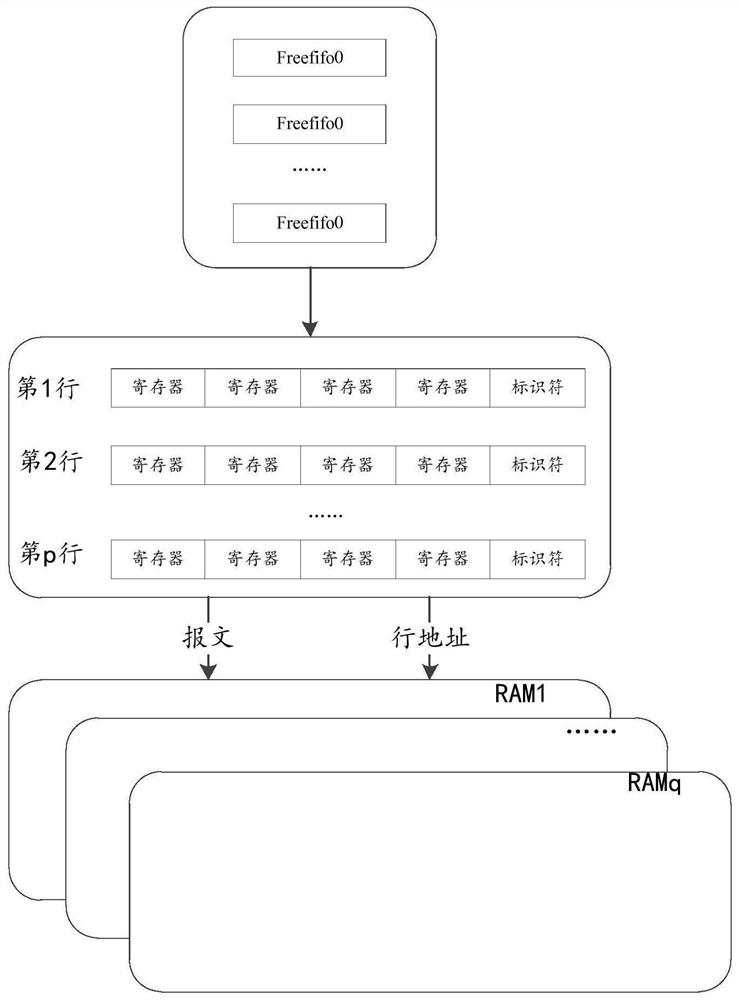

[0017] In order to make the purpose, technical solution and advantages of the application clearer, the embodiments of the application will be described in detail below in conjunction with the accompanying drawings. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined arbitrarily with each other.

[0018] Since the memory in the chip stores messages according to the row address, each row in the memory stores only one message. When the chip is used for processing large amounts of data, the length of the message is less than For ordinary messages, when the chip writes and reads small packets and long messages, a large amount of storage space is wasted on the chip memory. Correspondingly, a larger memory needs to be installed on the chip, and the chip area is larger and the power consumption is too high. In this embodiment of the present application, multiple small packets and long messa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More