Reading calibration method of memory controller, computer device and readable storage medium

A technology of memory controller and computer device, applied in the direction of instruments, electrical digital data processing, etc., can solve the problems of DQS/DQSB duty cycle error, affecting data sampling accuracy, and judgment result duty cycle error, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

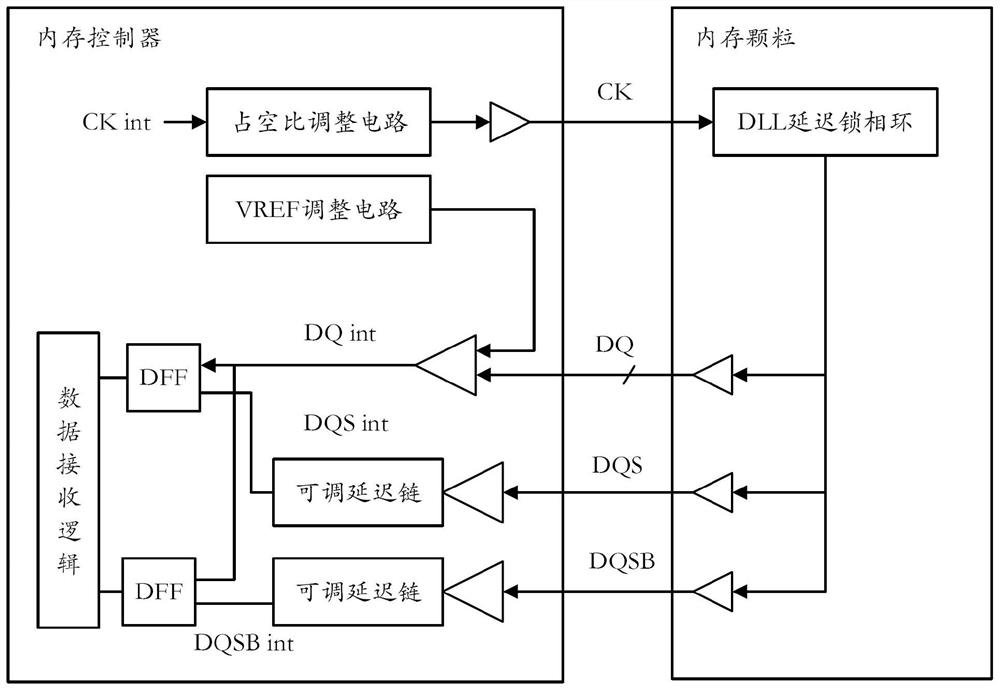

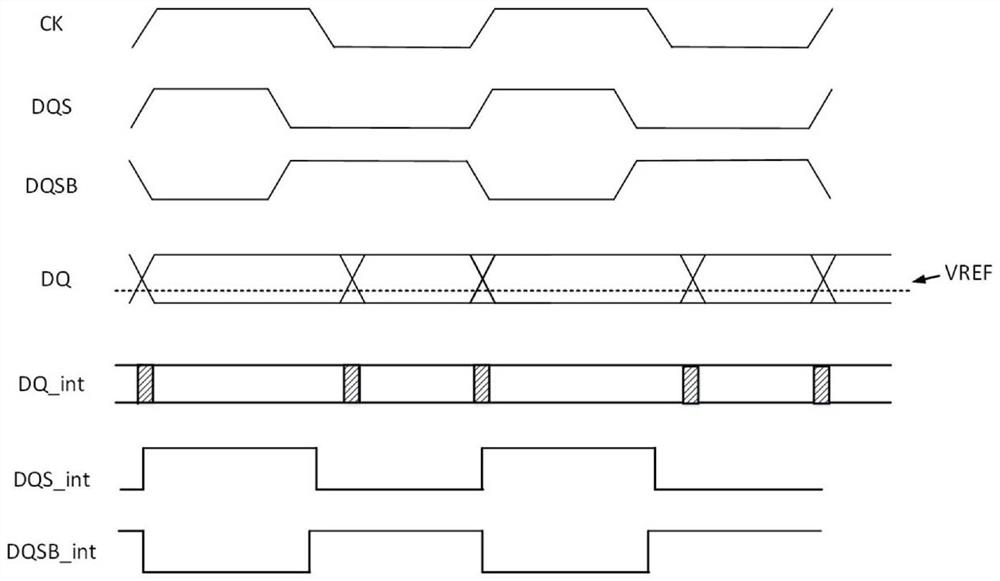

[0033] The block diagram of the DDR memory data reading system is as follows: figure 1 As shown, the memory particle is a general architecture, and the controller adopts the architecture for the present invention. The DDR controller provides CK to the memory particle as a reference clock, and the memory particle uses DLL (delay-locked loop), and uses CK as a reference to output DQ and DQS / DQSB to the memory controller, the memory controller uses VREF to judge the input DQ to get DQ_int When DQ>VREF, then DQ_int=1, when DQ<VREF, then DQ_int=0, and use the adjustable delay chain to input DQS / DQSB Delay to get DQS_int / DQSB_int, and finally DQ_int is sampled by DQS_int / DQSB_int to get input data.

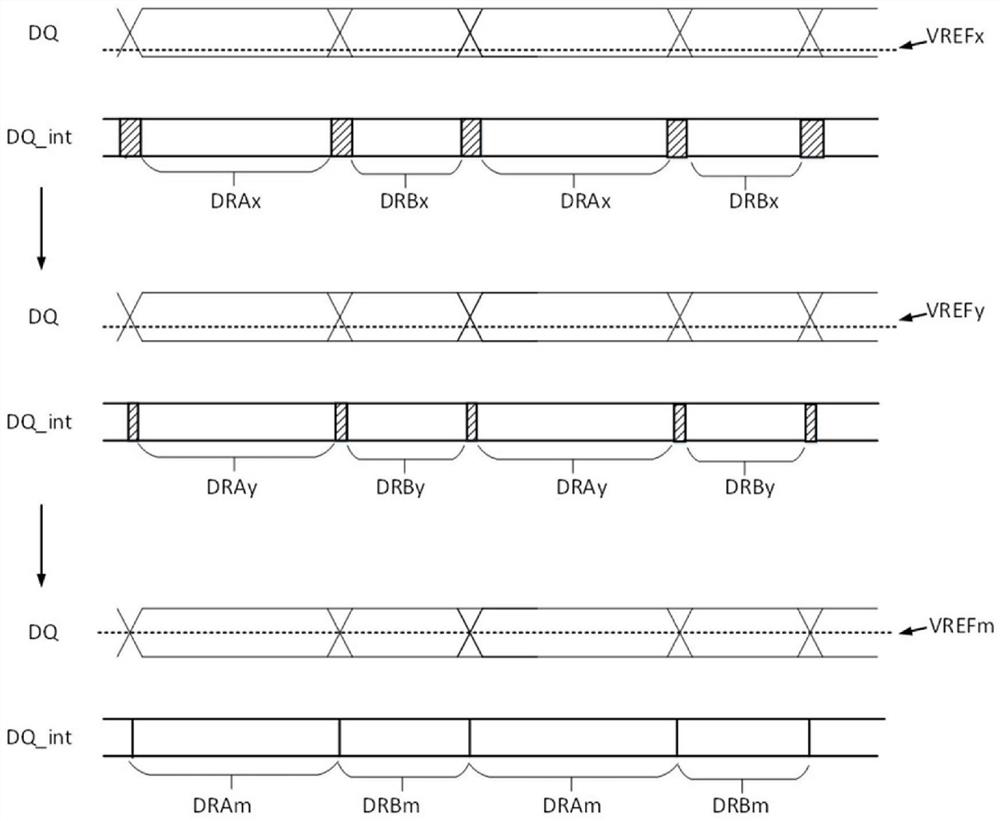

[0034] All links in the above process may produce duty cycle errors, including: 1. Controller output CK duty cycle errors; 2. Particle internal DQ and DQS / DQSB generation circuits have duty cycle errors; 3. Control The VREF selection of the controller is unreasonable, and the duty cyc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More