Verification method and verification system of chip monitor module based on UVM

A verification method and monitor technology, applied in the field of verification system, can solve problems such as the inability to guarantee verification parameterization and the inability to ensure the convenience of project migration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

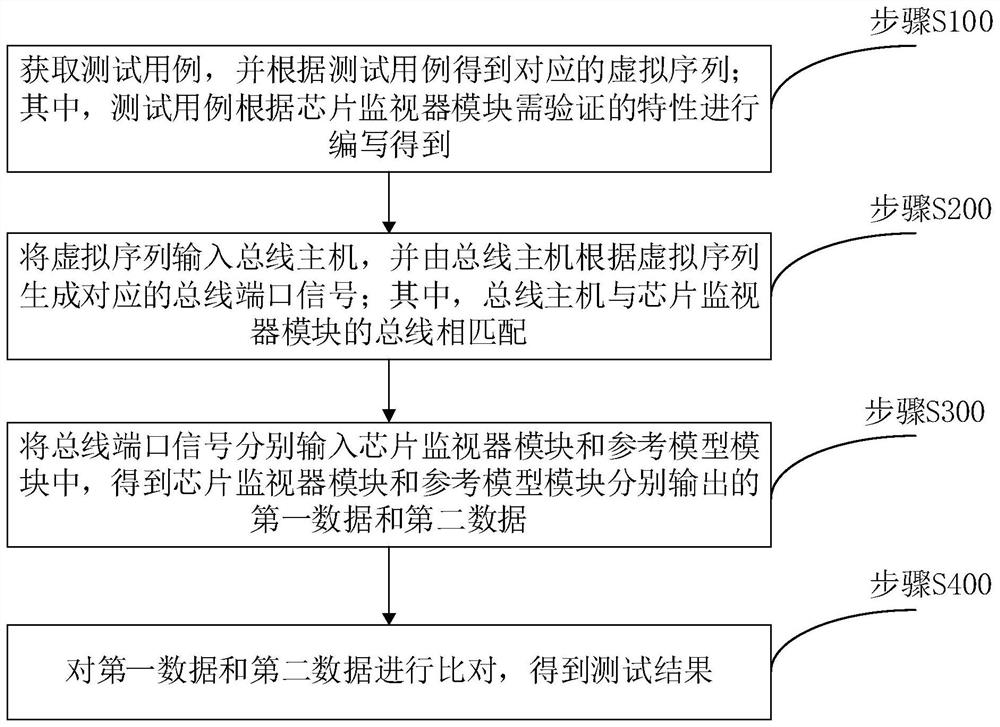

[0052] The technical solutions in the embodiments of the present application will be described below with reference to the drawings in the embodiments of the present application.

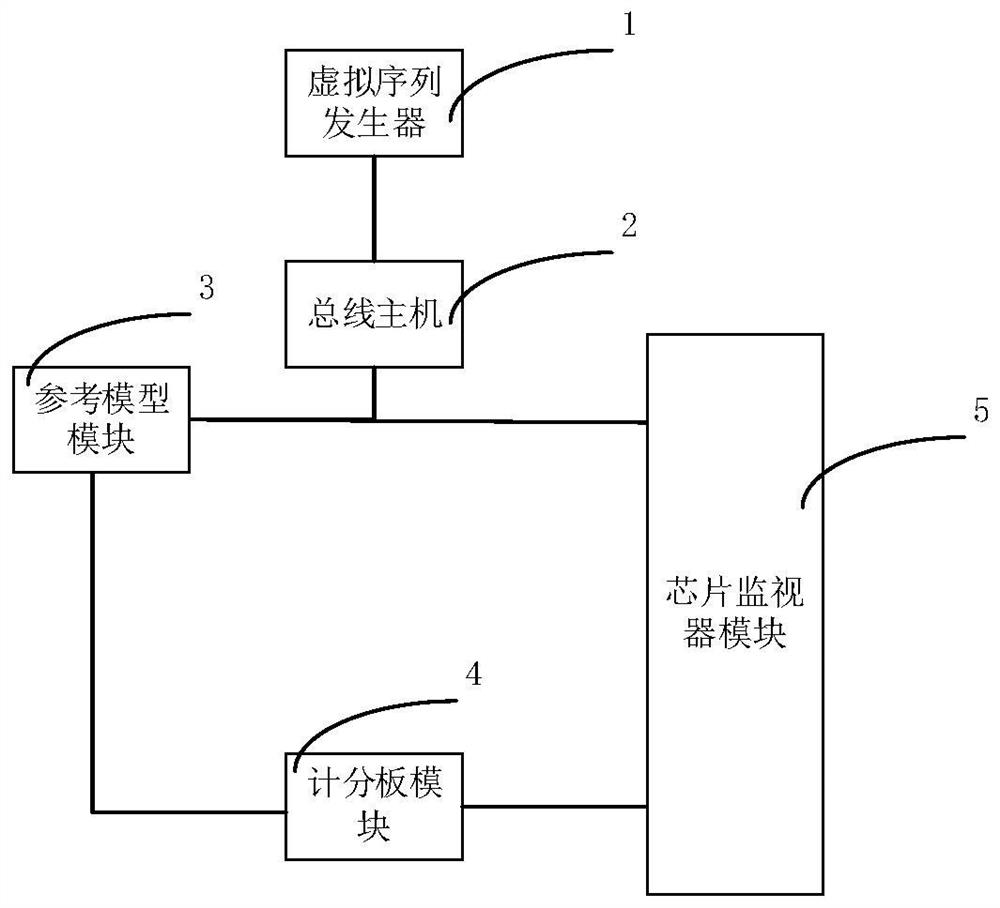

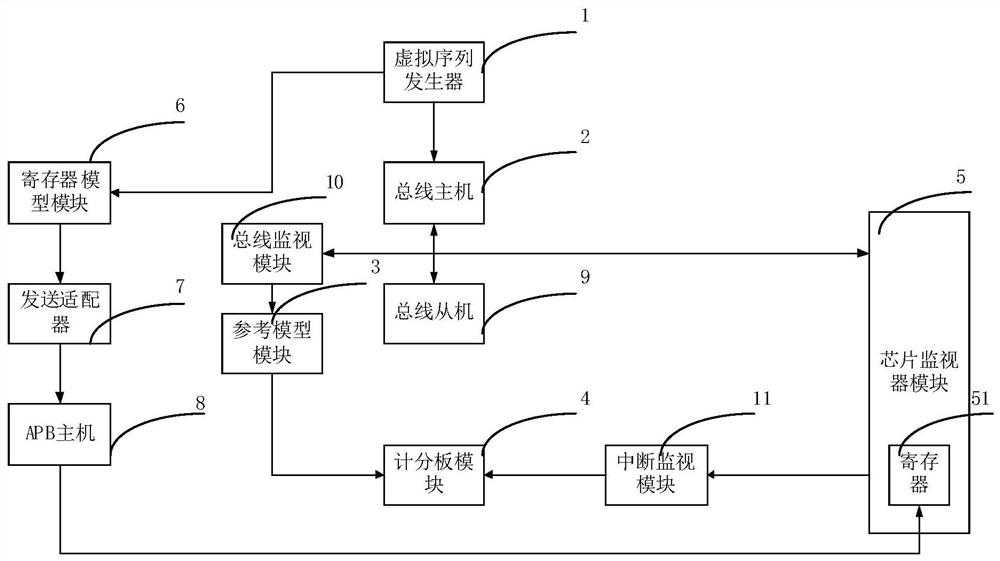

[0053]The core of the present invention is to provide a verification method based on a UVM-based chip monitor module. The UVM (Universal Verification Methodology, Universal Verification Methodology) randomized verification method adopted by the method belongs to module-level verification, which ensures the parameterization of verification and can solve the problem of The problem of project inheritance and module change between different projects can ensure comprehensive verification; another core of the present invention is to provide a UVM-based chip monitor module verification system.

[0054] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More