Fan-out type packaging structure and packaging method

A packaging method and packaging structure technology, which are applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problems that the substrate manufacturing process cannot meet the requirements of chips and the high cost, achieve high industrial utilization value, improve the manufacturing process, and reduce the size The effect of package size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

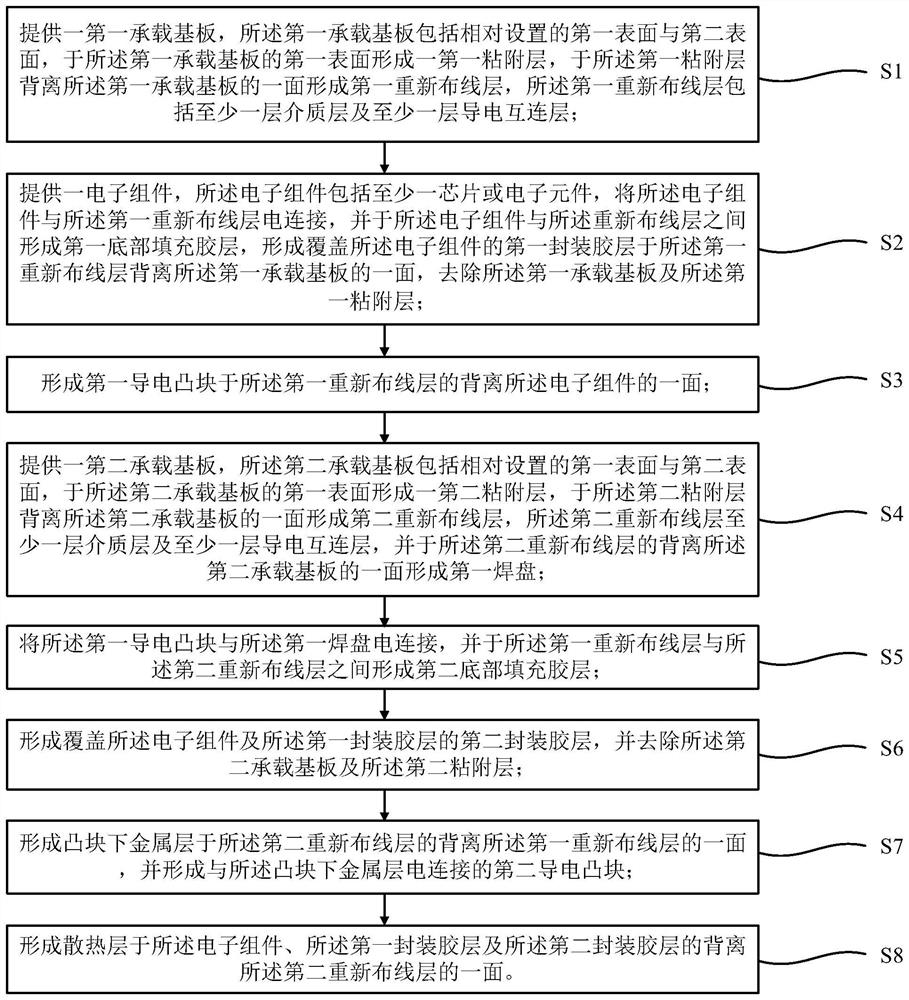

[0089] This embodiment provides a packaging method, such as figure 1 As shown, it is shown as a process flow diagram of the packaging method, including the following steps:

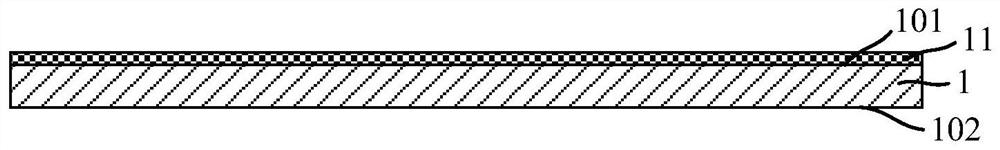

[0090] S1: Provide a first carrier substrate, the first carrier substrate includes a first surface and a second surface oppositely arranged, a first adhesive layer is formed on the first surface of the first carrier substrate, and a first adhesive layer is formed on the first carrier substrate A first rewiring layer is formed on a side of an adhesive layer away from the first carrier substrate, and the first rewiring layer has at least one dielectric layer and at least one conductive interconnection layer;

[0091] S2: Provide an electronic component, the electronic component includes at least one chip or electronic component, electrically connect the electronic component to the first rewiring layer, and form an electronic component and the rewiring layer The first underfill adhesive layer is used to for...

Embodiment 2

[0160] This embodiment provides a fan-out packaging structure, such as Figure 22 As shown, it is a schematic diagram of the cross-sectional structure of the fan-out packaging structure, including the first rewiring layer 12, electronic components 13, the first underfill layer 14, the first packaging adhesive layer 15, the heat dissipation layer 25, the second rewiring layer The wiring layer 22, the second underfill adhesive layer 23 and the second encapsulation adhesive layer 24, wherein the first rewiring layer 12 includes at least one dielectric layer 121 and at least one conductive interconnection layer 122, the first One side of the rewiring layer 12 is provided with a first conductive bump 123; the electronic component 13 is located on the side of the first rewiring layer 12 away from the first underfill glue layer 14, and the electronic component 13 includes at least A chip or an electronic component, the electronic component 13 is electrically connected to the first re...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More