Device for improving error of digital controllable attenuation semiconductor chip

A semiconductor and control device technology, which is applied in the direction of impedance network, electrical components, multi-terminal pair network, etc., can solve the problem of increasing attenuation error, achieve the effect of reducing attenuation error, improving isolation, and ensuring accuracy and stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

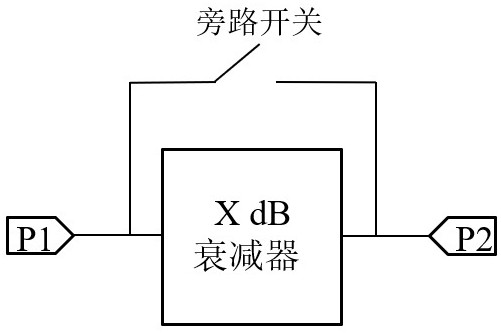

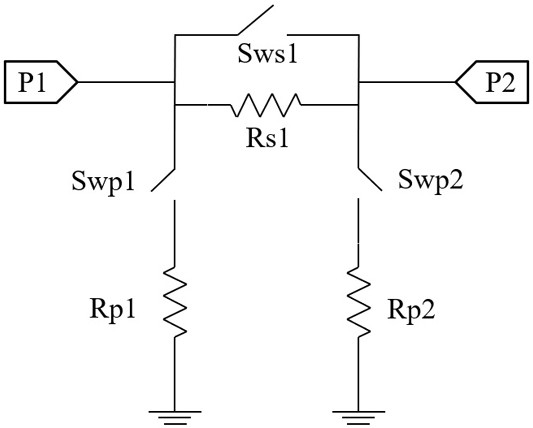

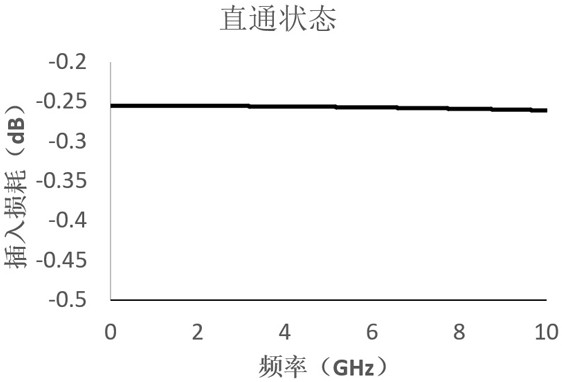

[0035] The present embodiment provides a device for improving digital controllable attenuation of semiconductor chip errors, such as Figure 5 and Figure 11 As shown, it includes a bypass series switch group and a regulating device, the bypass series switch group and the digital controllable attenuator are arranged in parallel at the electrical node between the port P1 and the port P2, and the bypass series switch group has a symmetrical circuit structure, One end of the control device is connected to the electrical node of the symmetrical center of the bypass switch group, and the other end is grounded. The device is connected in parallel with the bypass series switch group on the attenuator, and is grounded through the control device, which can effectively improve the connection between port P1 and port P2. The isolation in the attenuation state reduces the attenuation error and ensures the accuracy and stability of the relative attenuation of the digital controllable atten...

Embodiment 2

[0041] According to the device for improving digitally controllable attenuation semiconductor chip errors described in Embodiment 1, the π-type digitally controllable attenuator is replaced by a T-type digitally controllable attenuator.

[0042] Beneficial effects of the present invention:

[0043] In the present invention, a digitally controllable attenuator is connected in parallel with a bypass series switch group that can be grounded, which can effectively increase the isolation between the port P1 and the port P2, and significantly reduce the attenuation value error caused by insufficient isolation, thereby largely Ensure relative attenuation accuracy.

[0044] Those skilled in the art should understand that the embodiments of the present application may be provided as methods, systems, or computer program products. Accordingly, the present application may take the form of an entirely hardware embodiment, an entirely software embodiment, or an embodiment combining softwa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More