Network-on-chip design method for distributed parallel operation algorithm

An on-chip network and design method technology, applied in the field of computer algorithms, can solve the problems of network consumption, low network communication efficiency, low clock frequency, etc., and achieve the effect of reducing total delay, reducing the use of on-chip resources, and improving real-time performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] A kind of network-on-a-chip design method for distributed parallel computing algorithms of the present invention will be further described with reference to the accompanying drawings, and the present invention will be further described in detail below with reference to the embodiments:

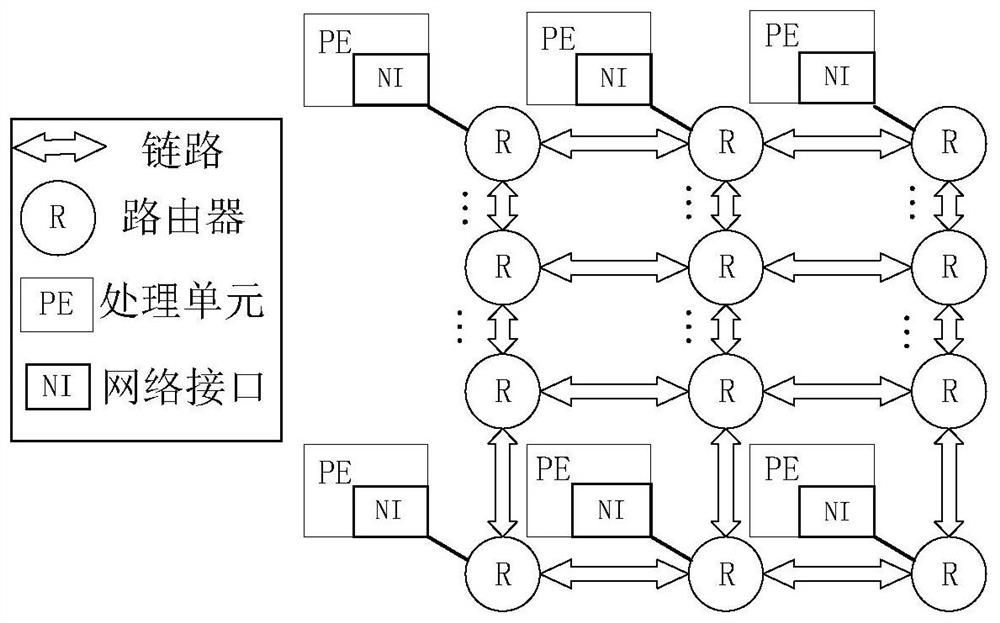

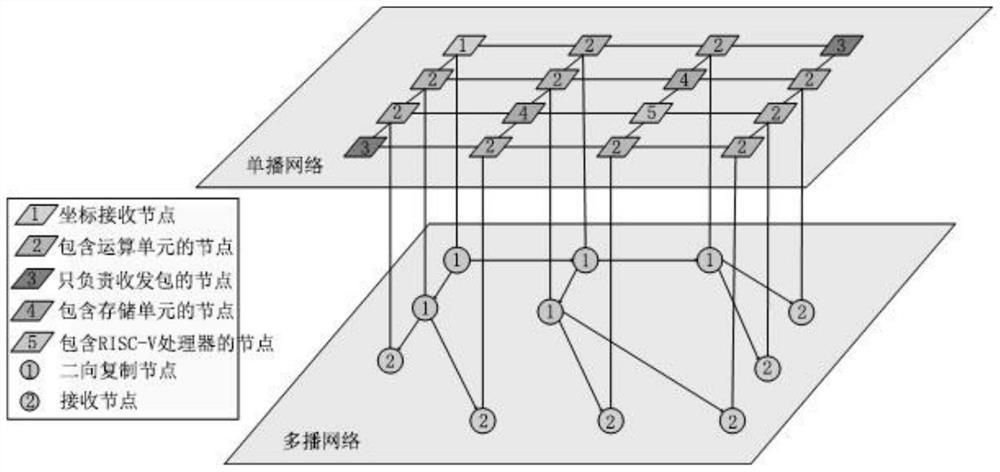

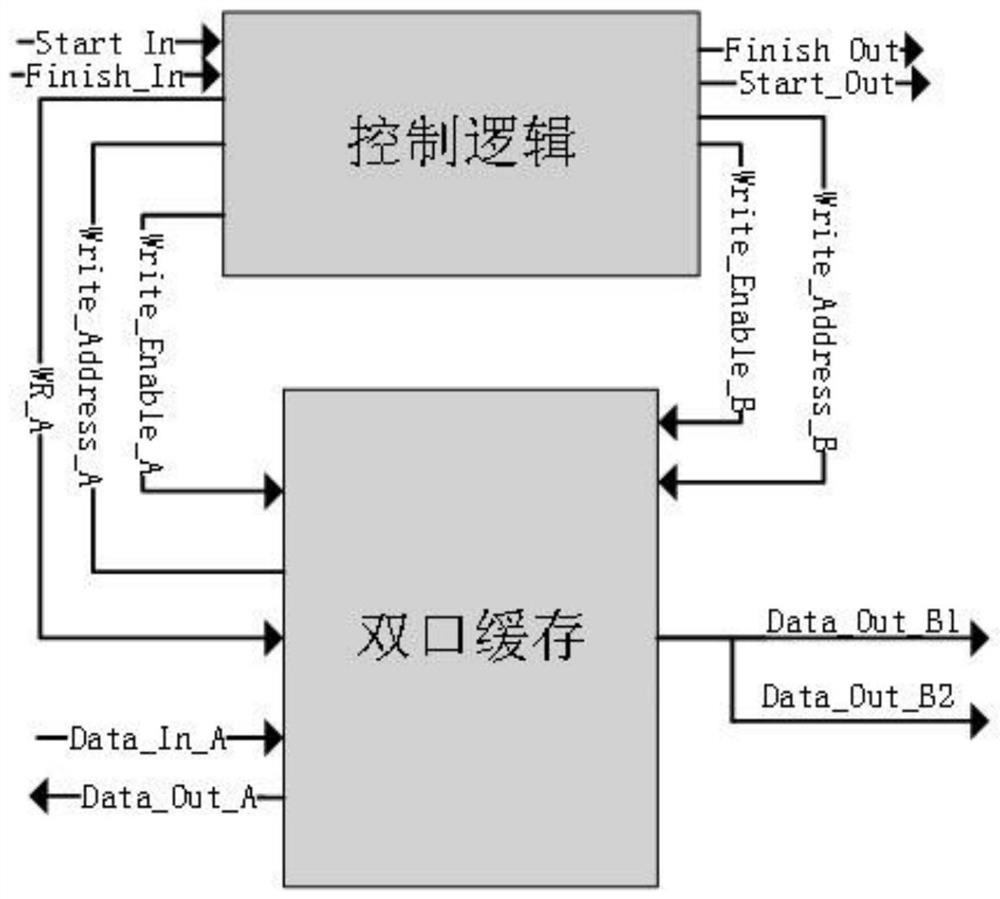

[0031] An on-chip network design method oriented to distributed parallel computing algorithms. According to the distributed parallel computing algorithm of the on-chip network, the on-chip network is divided into two layers, including a unicast network and a multicast network. The unicast network realizes the The point-to-point propagation of the computing node transmits the independent computing data required by each computing node to each computing node in the form of unicast; the multicast network is a customized multicast network for distributed parallel computing algorithms, which is used to transmit to all computing nodes. There is a shared operation data, and the efficient transmi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More