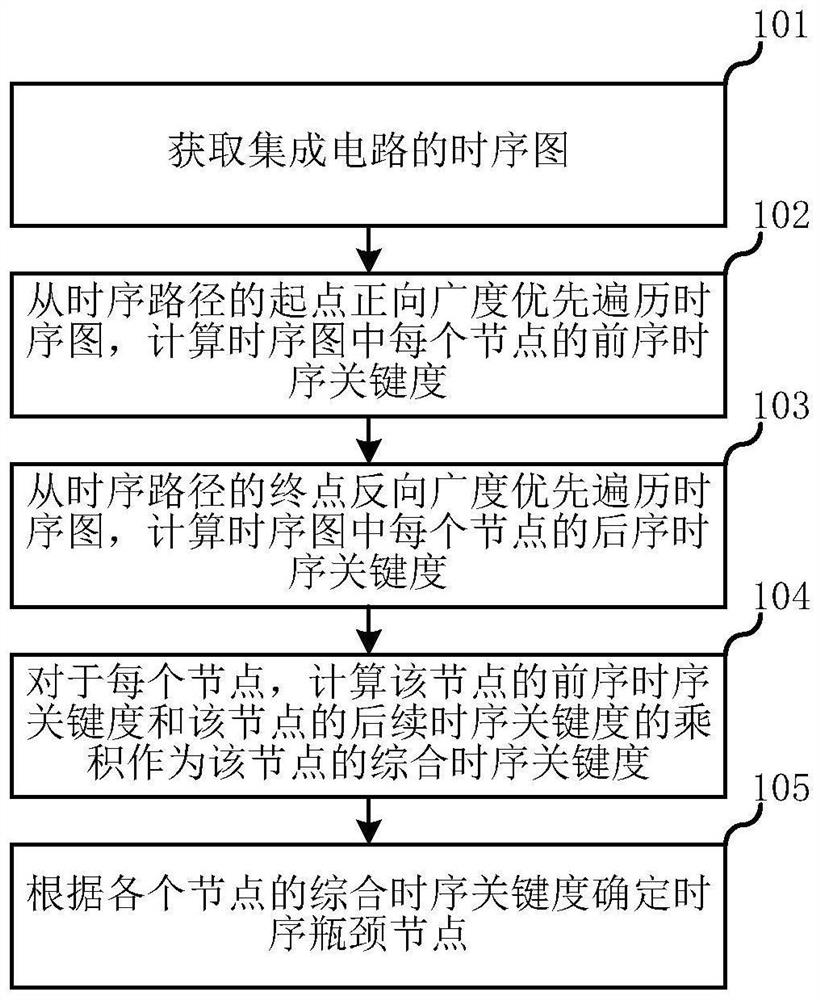

Time sequence bottleneck node analysis and time sequence optimization method and system in integrated circuit

An integrated circuit and node analysis technology, which is applied in the fields of electrical digital data processing, instruments, calculations, etc., can solve problems such as increased running time, excessive calculation, and low efficiency of critical timing paths, and achieve the goal of ensuring accuracy and improving efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

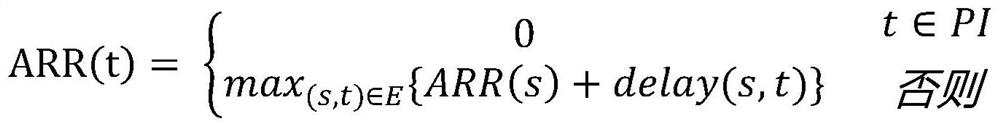

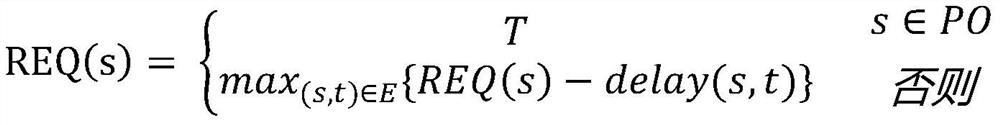

Method used

Image

Examples

Embodiment Construction

[0043] In the following description, numerous technical details are set forth in order to provide the reader with a better understanding of the present application. However, those of ordinary skill in the art can understand that even without these technical details and various changes and modifications based on the following embodiments, the technical solutions claimed in the present application can be realized.

[0044] Explanation of some concepts:

[0045] The source and drain ends of the wire net: the wire net connects the input and output ports of the logic device in the integrated circuit, representing the transmission of a digital signal; the source and drain ends of the wire net are the input and output ports of the digital signal .

[0046] Timing constraints: In order to meet the design goals, put forward timing requirements for the integrated circuit, try to meet this requirement in the design process, and check whether the circuit meets the requirements. Generall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More