Static discharge protecting element and realated circuit

A technology for electrostatic discharge protection and electrostatic discharge detection, which is applied in electrical components, circuits, and electrical solid devices, etc., and can solve problems such as long current paths and difficulty in quickly discharging ESD currents.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

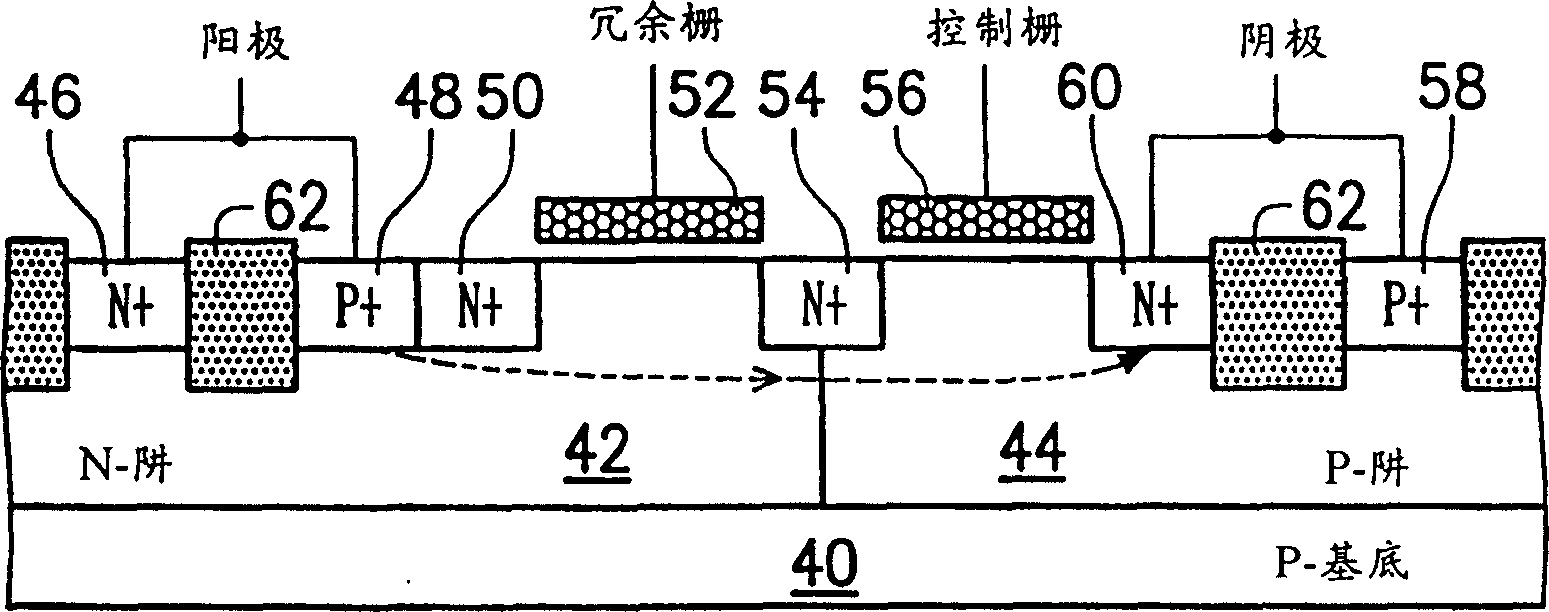

[0024] The spirit of the present invention is to use a redundant gate structure to replace the STI layer through which the ESD current in the known LVTSCR must bypass. In this way, the redundant gate structure can provide the isolation effect of the doped region on the one hand, and on the other hand, does not It will hinder the discharge path of the ESD current when an ESD event occurs. Therefore, the turn-on speed and ESD tolerance of the LVTSCR are improved.

[0025] refer to Figure 3a as well as Figure 3b , Figure 3a For an NMOS-triggered LVTSCR according to the present invention, Figure 3b for Figure 3a The circuit represents the symbol. Figure 3a The LVTSCR in LVTSCR is triggered by an NMOS, referred to as nSCR. The nSCR is fabricated on a P-type substrate 40 and includes an N-type well 42 and a P-type well 44 .

[0026] A P+ doped region 58 is disposed in the P-type well 44 as an electrical contact point of the P-type well 44 . The NMOS for triggering is a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More