Improvement for shallow slot separated structure height homogeneity

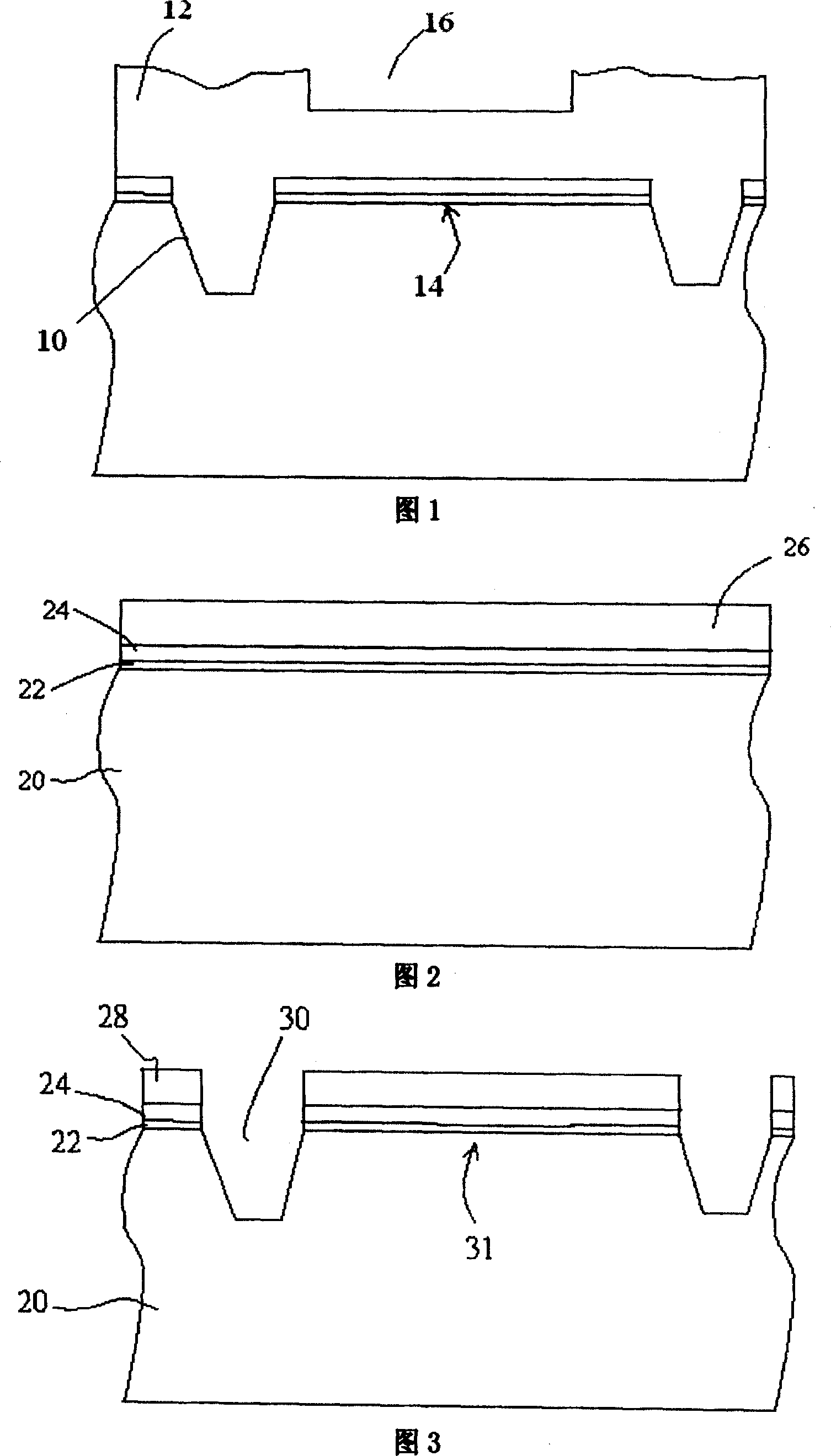

A technology of shallow trench isolation and uniformity, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to solve the problems of reduced oxide layer 12 density, poor polishing rate, and difficulty in meeting the needs of integrated circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

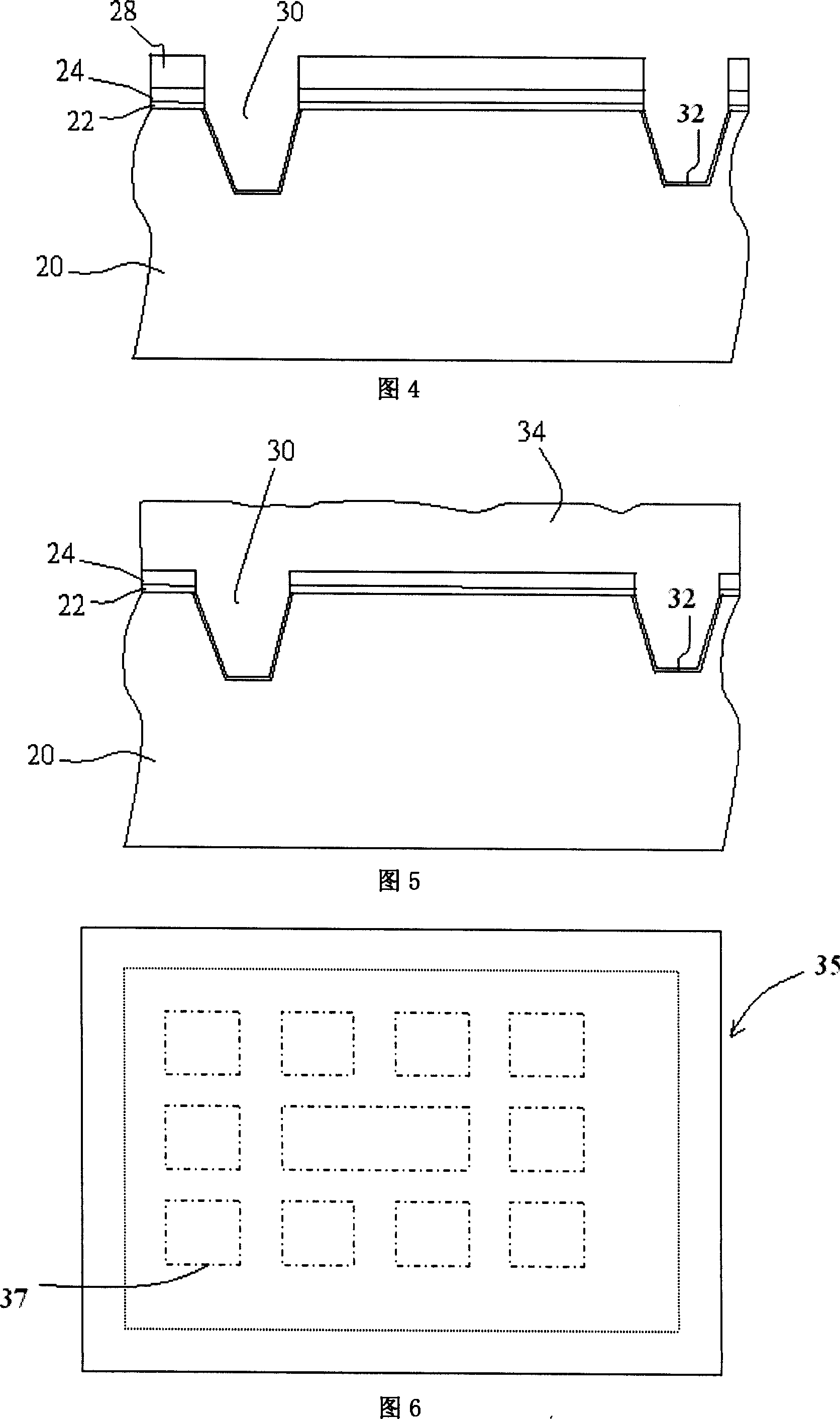

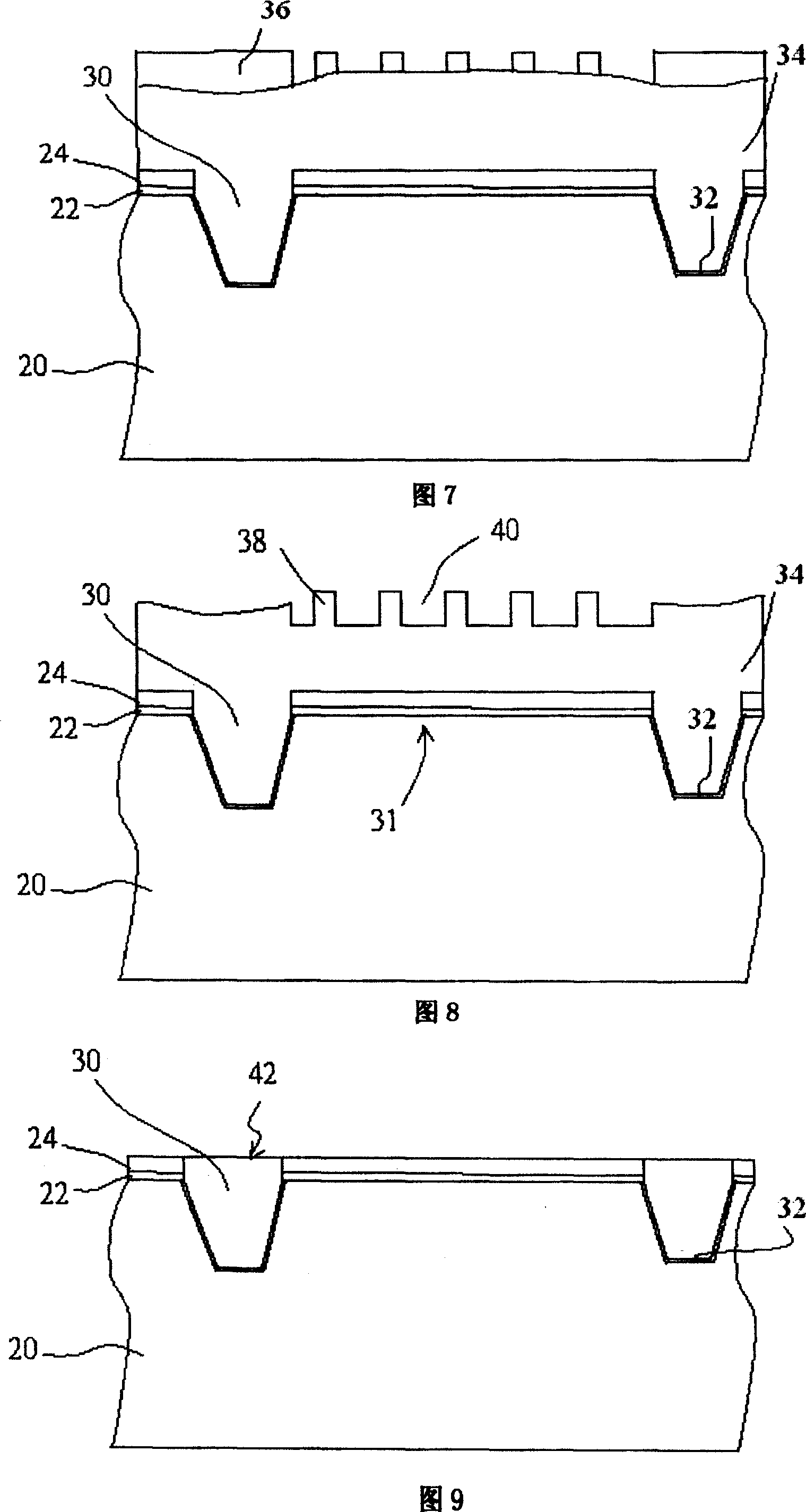

[0017] The invention relates to a method for improving the height uniformity of the shallow trench isolation structure, which can be widely applied to the isolation process in the deep submicron semiconductor process to obtain the best isolation effect between elements. Referring to Fig. 2, at first a semiconductor substrate 20 is provided, then the semiconductor substrate 20 is cleaned, then the semiconductor substrate 20 after cleaning is sent into a vertical or horizontal furnace tube, in an oxygen-containing environment, On the semiconductor substrate 20, a material is formed as a pad oxide layer 22 of silicon dioxide (SiO2), a material is a nitride layer 24 of silicon nitride (Si3N4) made by a low pressure chemical vapor deposition method, and a photo The resist layer 26 is then transferred to the photoresist with an active area (Active Area) mask (not shown in the figure) to form a first patterned photoresist. Layer 28, as shown in FIG. 3, is then anisotropic etched (Ani...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More