Correction circuit, delay circuit and annular oscillator circuit

A technology for calibrating circuits and circuits, applied in electrical pulse generator circuits, pulse manipulation delays, and logic circuits to generate pulses, etc., can solve problems such as inability to use, and achieve the effects of reducing power consumption and stabilizing delay time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0101] The present invention will be described below by way of example with reference to the accompanying drawings.

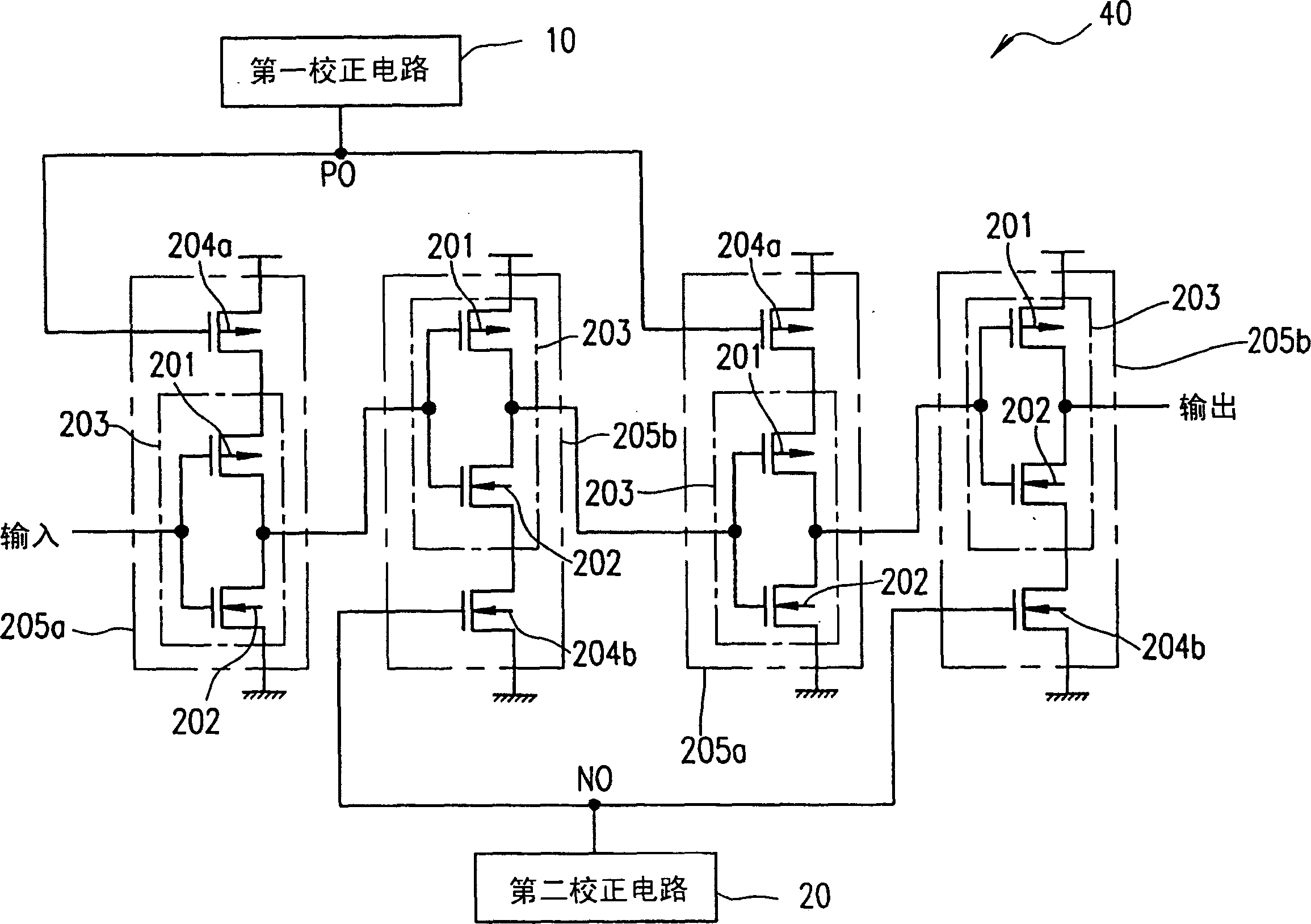

[0102] figure 1 An example delay circuit 40 according to the invention is shown. previously discussed about Figure 8 and 16 The same elements have the same reference numerals, and their detailed descriptions will be omitted below.

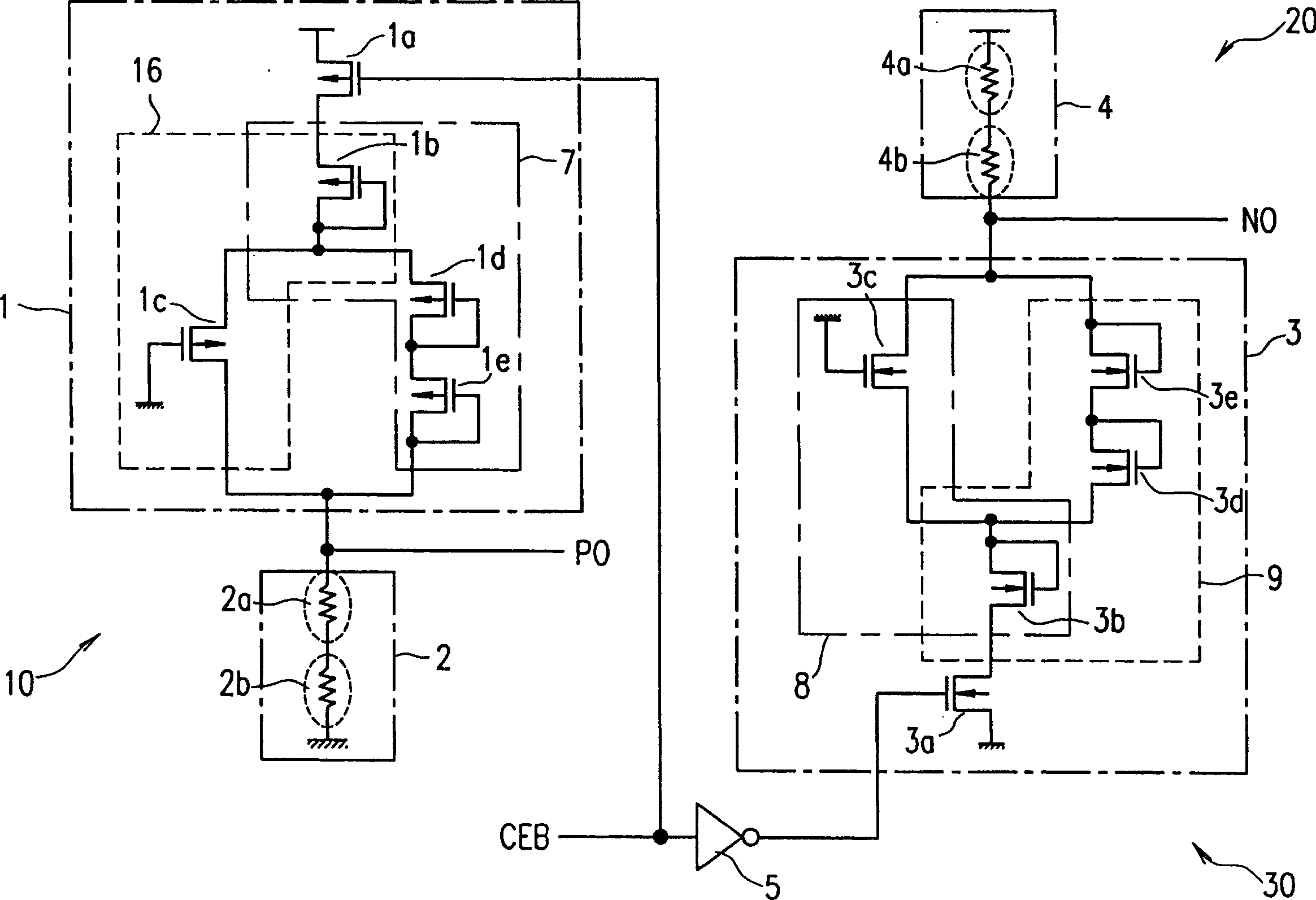

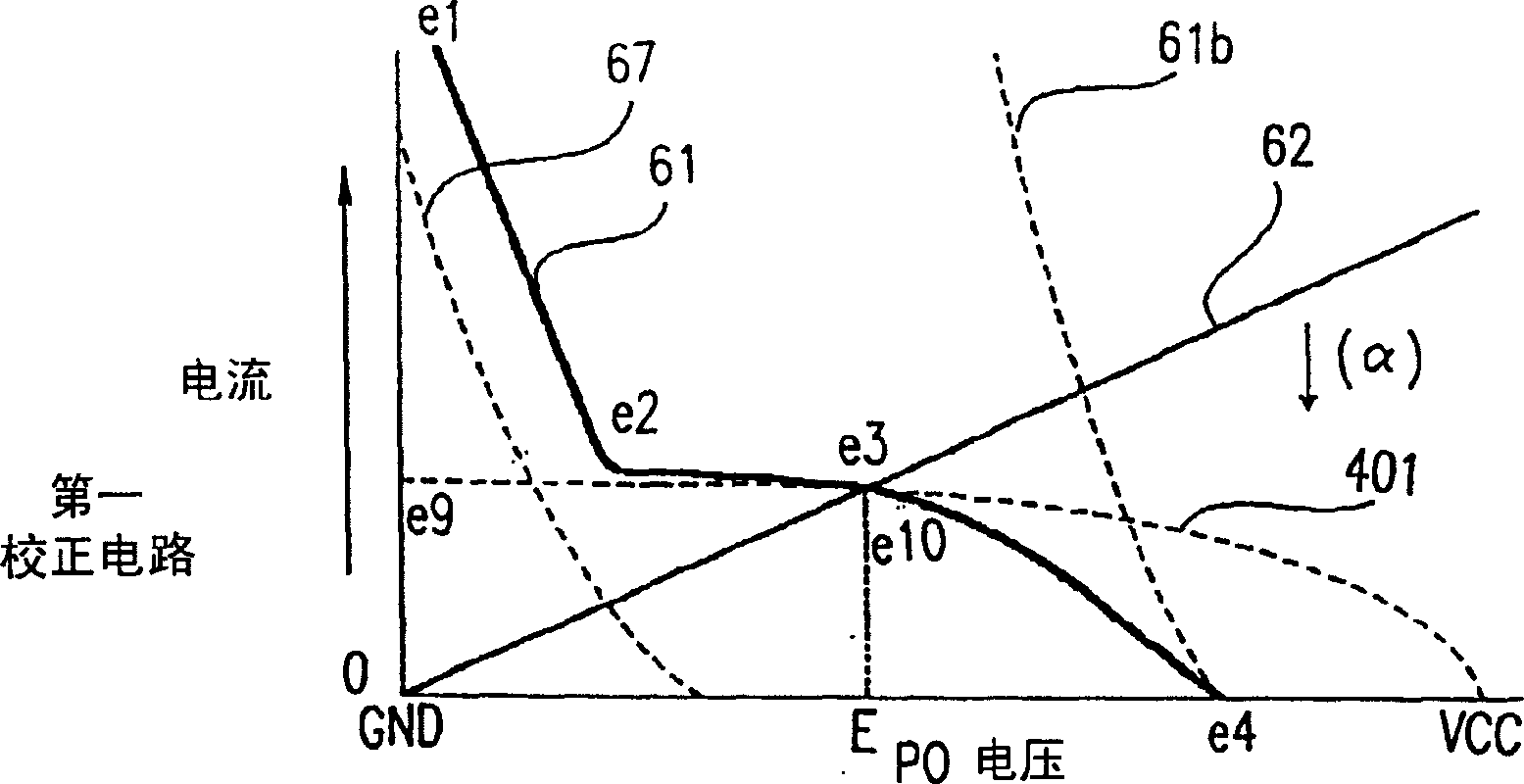

[0103] The delay circuit 40 includes a first correction circuit 10 and a second correction circuit 20, instead of Figure 8 A first correction circuit 210 and a second correction circuit 220 in the delay circuit 200 are shown. The gate of the p-channel transistor 204a included in the inverter circuit 205a receives the voltage (control signal) generated in the first correction circuit 10 . The gate of the n-channel transistor 204b included in the inverter circuit 205b receives the voltage (control signal) generated in the second correction circuit 20 . Except for these points, the delay circuit 40 has the same circuit configu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More