Timing and data recovery circuit

A technology for recovering circuits and data, applied in electrical digital data processing, instruments, etc., can solve the problem of high power consumption of D-type flip-flops, and achieve the effect of low power and small volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

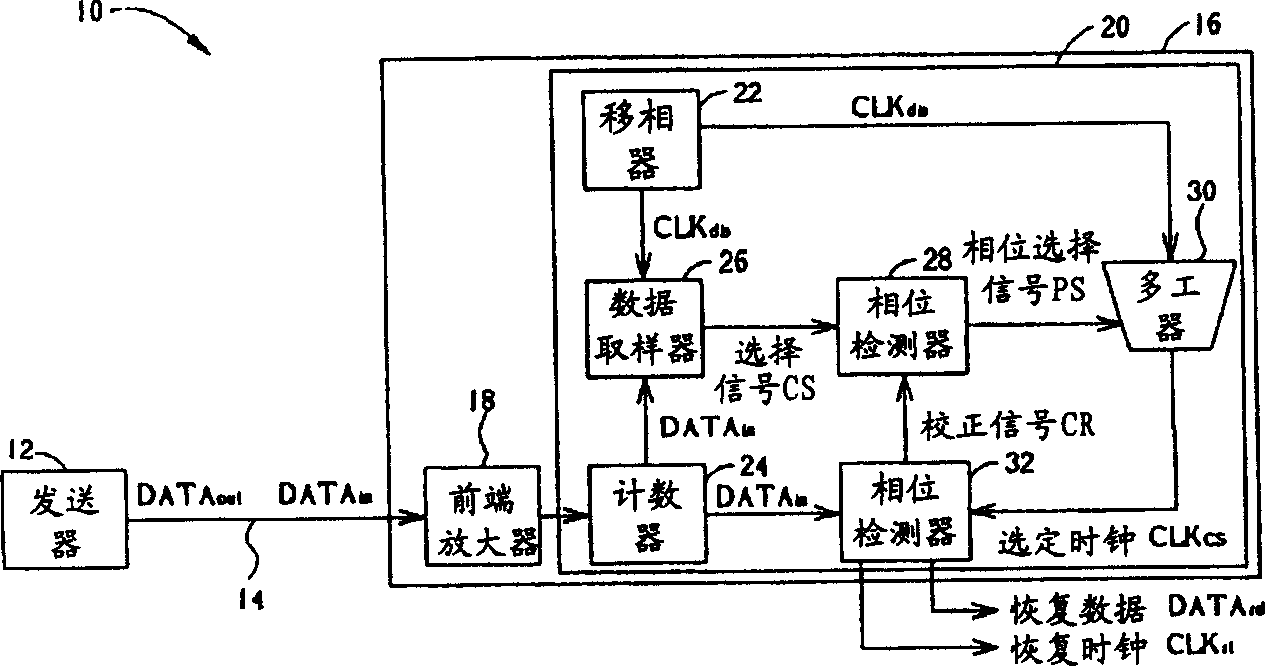

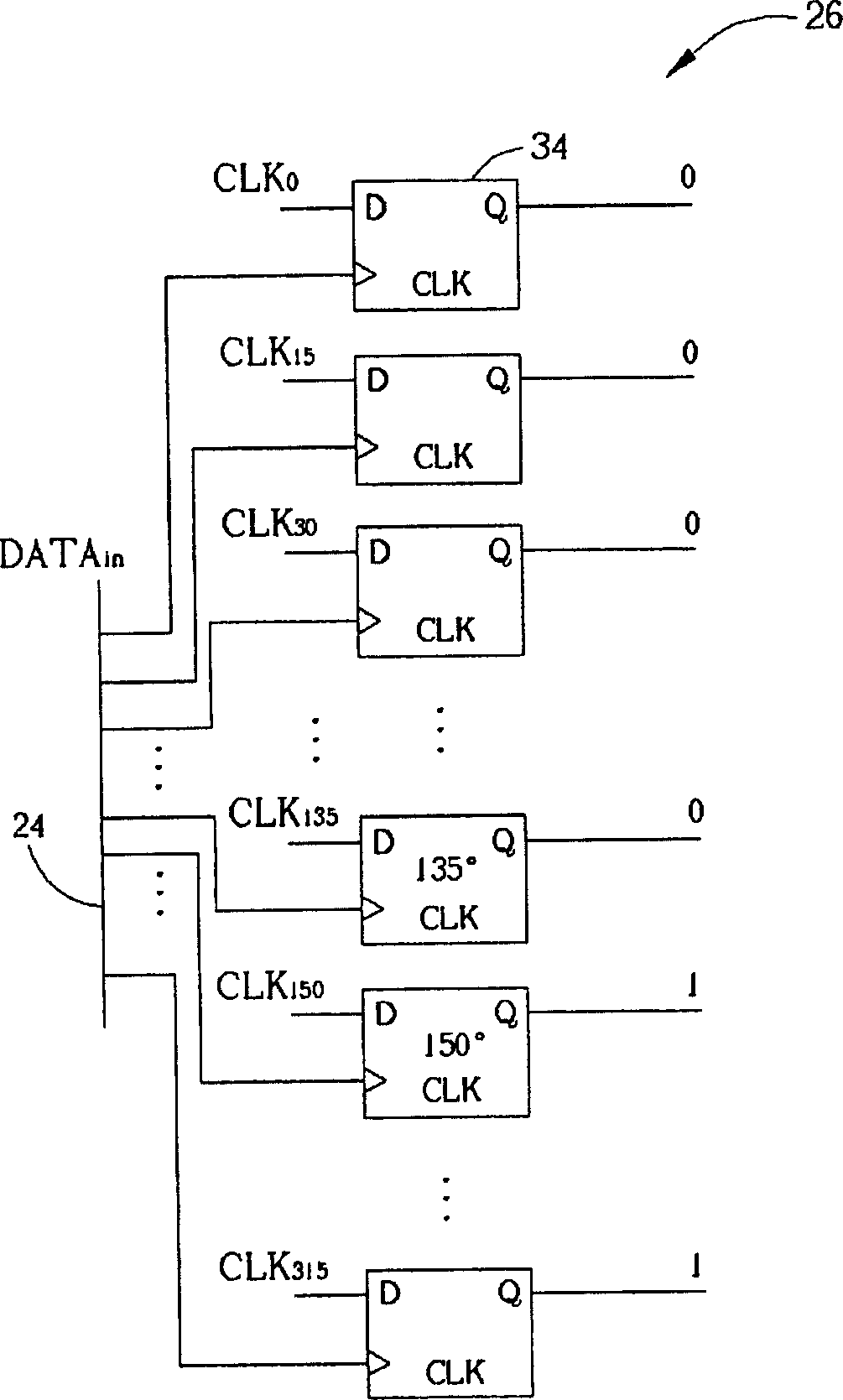

[0027] The phase shifter of the CDR in the preferred embodiment of the present invention generates M separate clock signals CLK less than the conventional number dis , And then separate the clock signal CLK from any two adjacent dis ,Insert at least one inserted clock signal CLK int , Together with the two adjacent separated clock signals CLK dis To form a set of clock signals, and then select one from the set of clock signals that is more synchronized with an input data DATA in Selected clock signal CLK cs . Since at least one plug-in clock signal CLK is guided in the plug-in manner int Only a set of common circuits can be realized, so there is no need to implement a data sampler with a large number of D-type flip-flops as usual, so the number of D-type flip-flops and the volume occupied by them can be greatly reduced, and the manufacturing cost is greatly reduced.

[0028] See Figure 4 It is a functional block diagram of a CDR in a preferred embodiment of the present invention....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com