Method and apparatus for improving PCB design efficiency

A design efficiency and design tool technology, applied in the computer field, can solve the problems of increased PCB design error rate, large workload, long layout design time, etc., to reduce workload, improve efficiency, and reduce complexity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

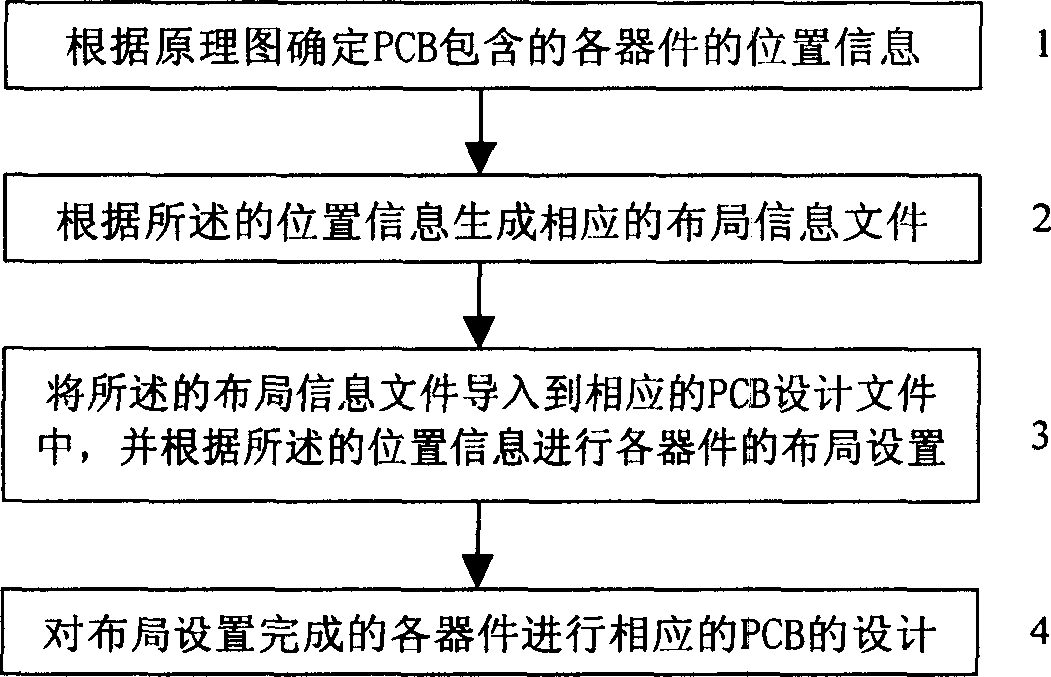

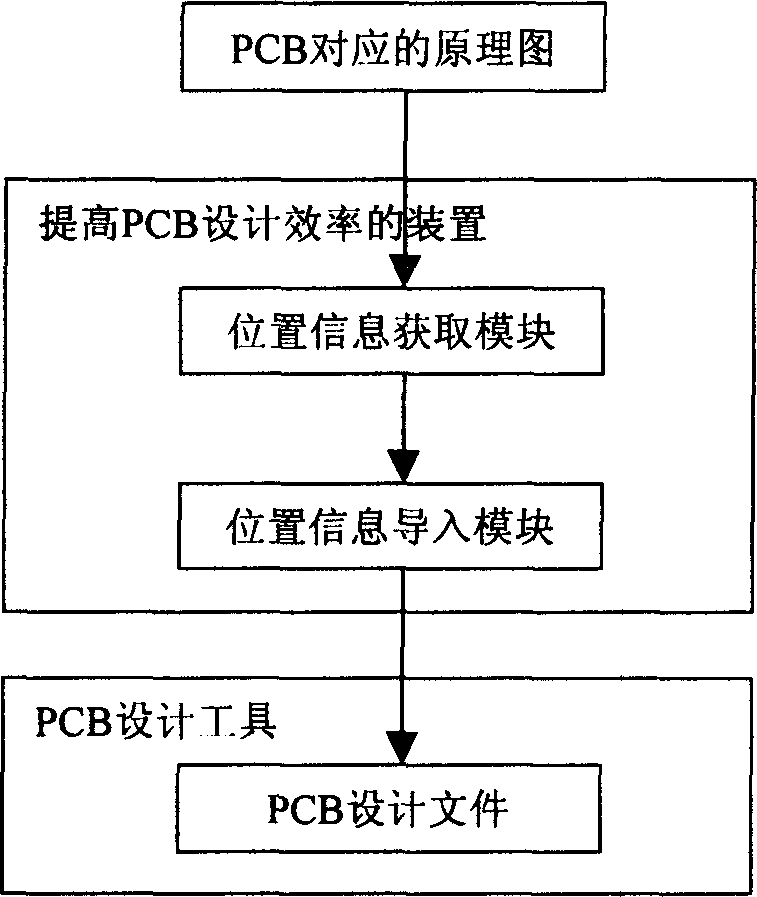

[0035] The invention mainly brings the position information of devices in the PCB schematic diagram into PCB design, so that the PCB design is realized based on the position information of each device in the PCB schematic diagram, thereby doubling the efficiency of PCB layout design.

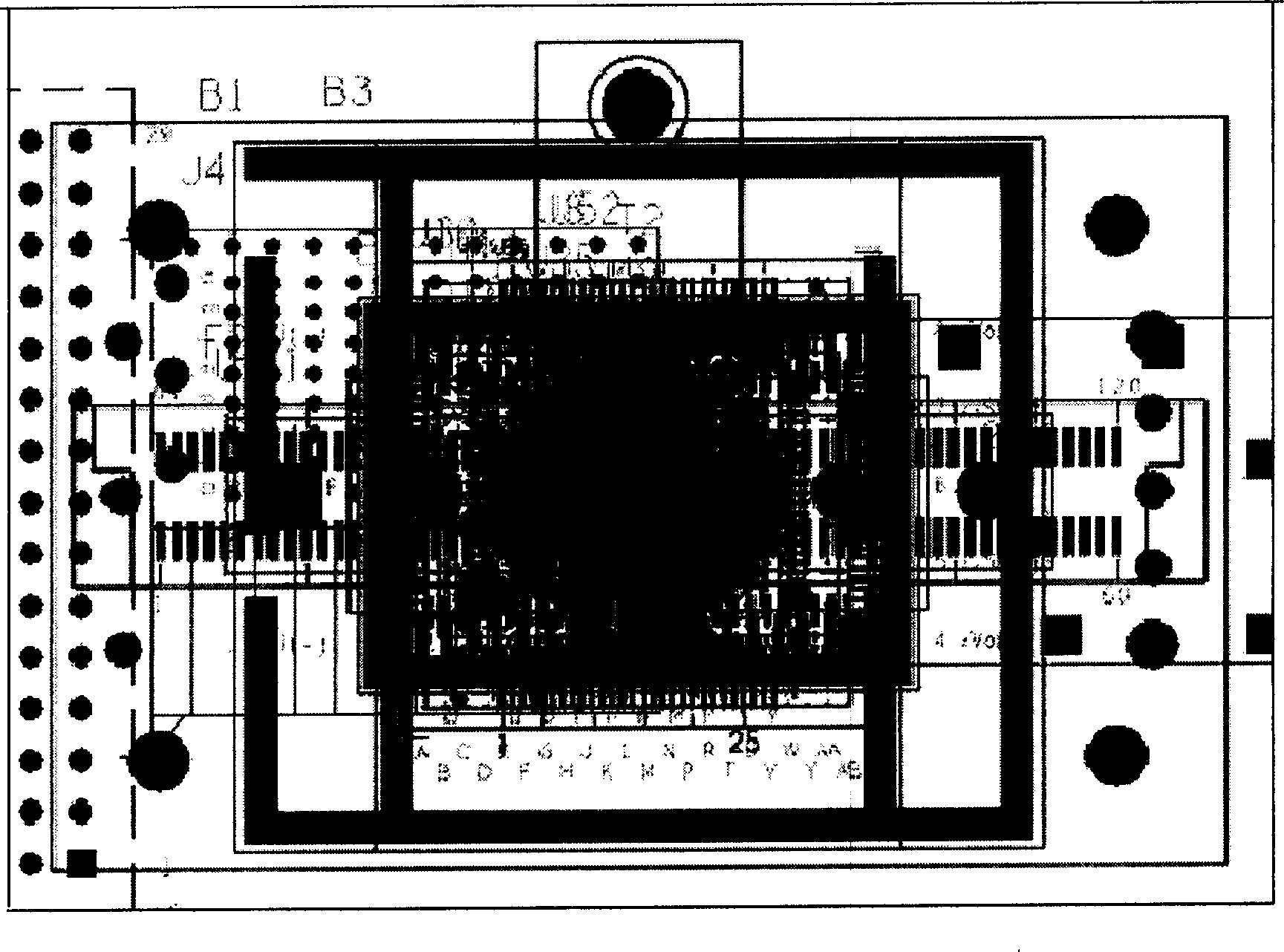

[0036] In the PCB, if the relative position of each device is the same as that of the device in the schematic diagram. As an ordinary PCB design engineer, it is easy to understand the relationship between them and the required layout position only by looking at the relative positions of the devices in the PCB diagram. In this way, the layout of more than 95% of the devices can be completed almost without using the schematic diagram when the PCB is laid out, which greatly improves the design efficiency. Although the PCB package size of a device may be quite different from the size of the mark in the schematic diagram, the inconsistency of the device size will not affect the PCB design engineer's ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More