Scan test design method, scan test circuit, scan test circuit insertion cad program, large-scale integrated circuit, and mobile digital device

A technology of scanning test and design method, which is applied in the direction of detecting faulty computer hardware, circuits, calculations, etc., can solve problems such as increased power consumption, increased circuit area, and increased number of delay elements, and achieves improved pass rate and good design guarantee Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

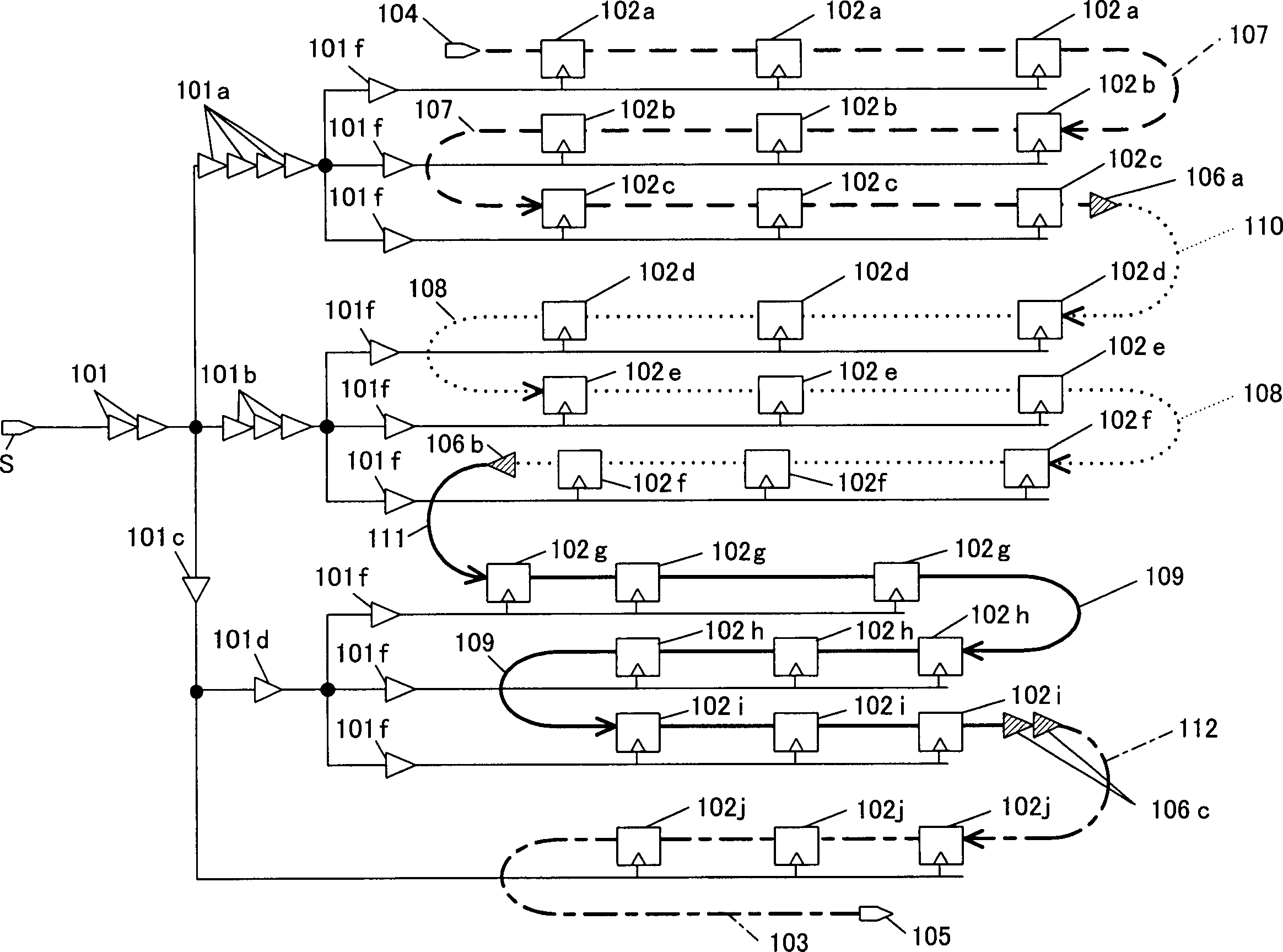

[0054] figure 1 It shows the structure of the scan shift register of the scan shift circuit realized by the test simplification design method in the first embodiment of the present invention, and especially shows the structure of the CTS buffer and the connection relation of the scan shift register. Below, use the figure 1 Be explained.

[0055] exist figure 1 Among them, 101 is a clock delay adjustment buffer, 101a to 101f are CTS buffers, and a clock tree T is formed. The clock tree T is divided into buffers 101a, 10b and 101c, each branch is further divided into three buffers 101f. A clock signal is supplied to the clock terminals of the FF circuits 102a to 102j which are many flip-flop circuits (hereinafter referred to as FF circuits) through this clock tree T.

[0056] In the design method of this embodiment, firstly, a scanning shift register is formed by taking a plurality of FF circuits driven by the last-stage element 101f of the CTS as the minimum unit. So, u...

no. 2 example

[0060] Next, a second embodiment of the present invention will be described.

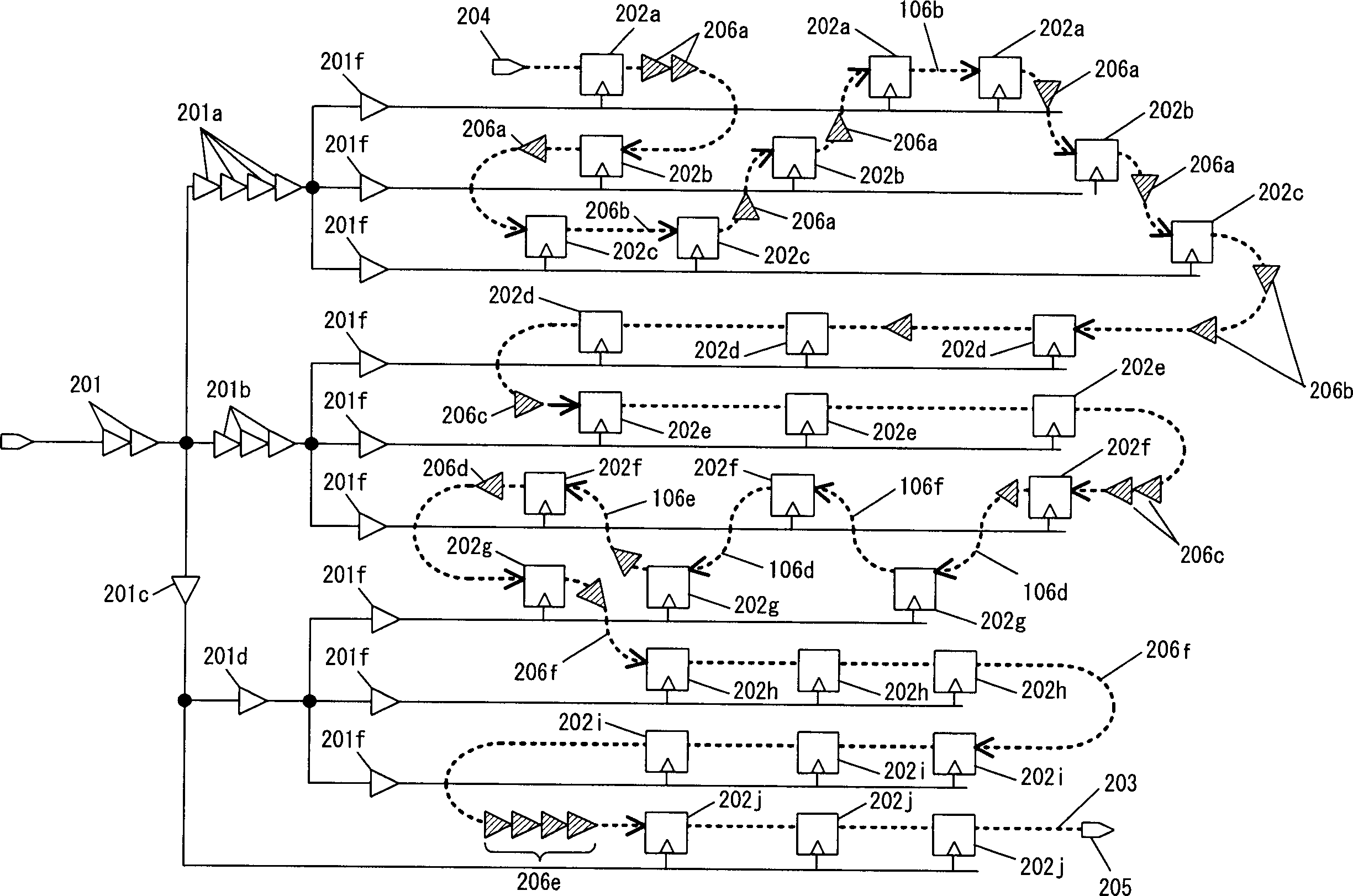

[0061] In the representation of the first embodiment figure 1 In this case, three FF circuits 102a are used to constitute a sub-scanning chain, and three FF circuits 102b, 102c, 102d, 102e, 102f, 102g, 102h, 102i, and 102j are used in the same manner as the three FF circuits 102a. Each scanning shift register is constituted. Therefore, in the first embodiment, the scan test circuit can be constituted by connecting the respective input and output of the shift register to the scan input or the scan output of the LSI. However, in this case, in a large-scale circuit, the following situation will be caused, that is, the number of test terminals is huge, and due to the increase of test cost and the constraints of external terminals of large-scale integrated circuits, the terminals are not enough, and it is difficult to realize the test. Simplistic design.

[0062] Therefore, by connecting the sub-scan...

no. 3 example

[0066] Next, a third embodiment of the present invention will be described.

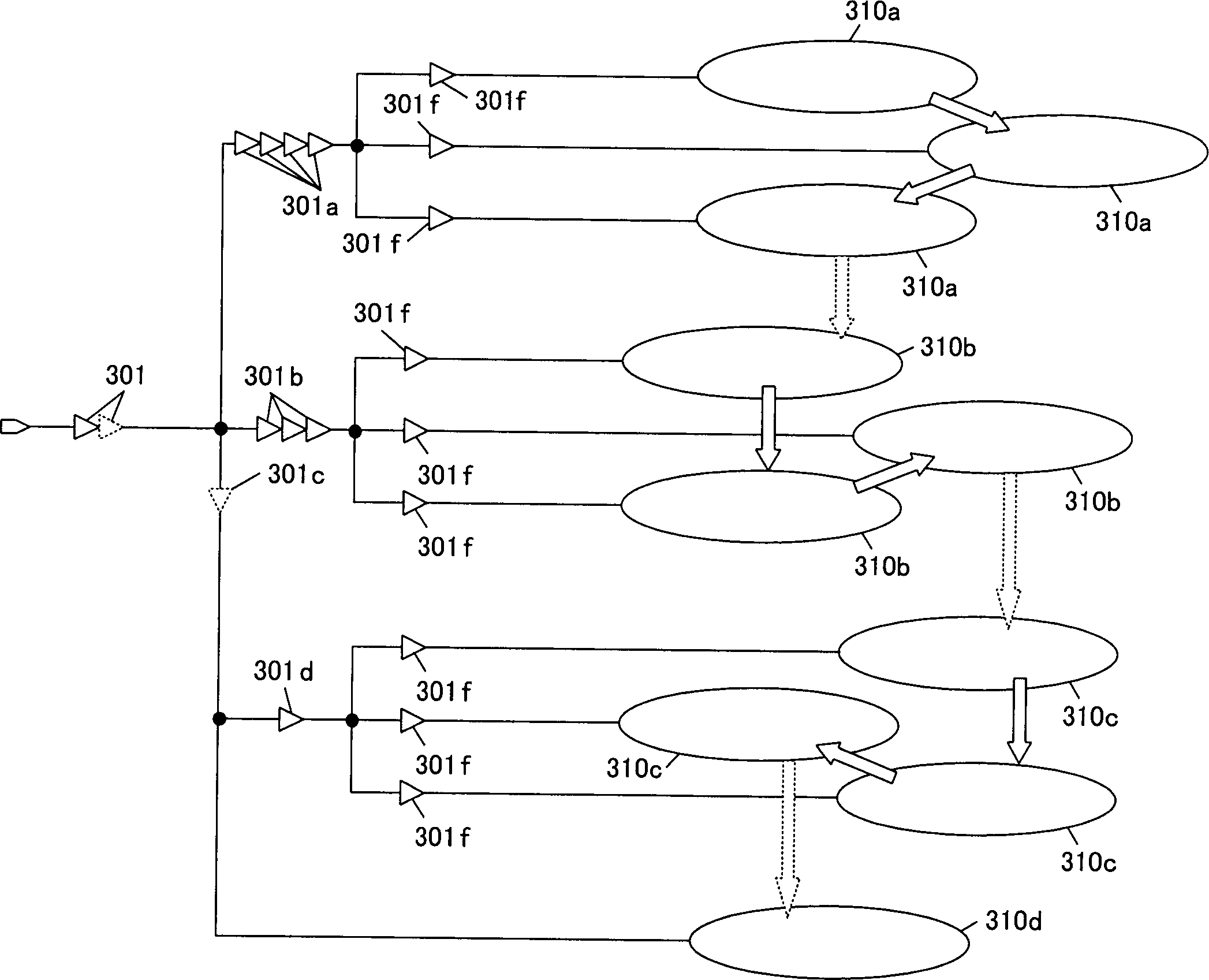

[0067] The third embodiment shows a design method adopted when the number of scan test terminals (scan input terminals and scan output terminals) cannot exceed the restricted number of terminals in the second embodiment.

[0068] If the restriction on the number of scan test terminals cannot be met in the second embodiment, or if the number of scan chains needs to be further reduced for other reasons, it is necessary to interconnect scan shift registers with different stages of CTS buffers. In this case, firstly, as in the second embodiment, the shift registers having the same number of CTS buffer stages are preferentially connected in series through the sub-scan chain inter-connecting networks 107 , 108 and 109 .

[0069] Next, at figure 1 Among them, as the second priority order of connection, the shift registers with the smallest relative buffer stage difference from the clock supply point S to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More