Fault positioning method

A fault location and fault technology, applied in the direction of fault location, electronic circuit testing, measuring devices, etc., can solve the problems of high cost, high density and replacement of replacement parts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

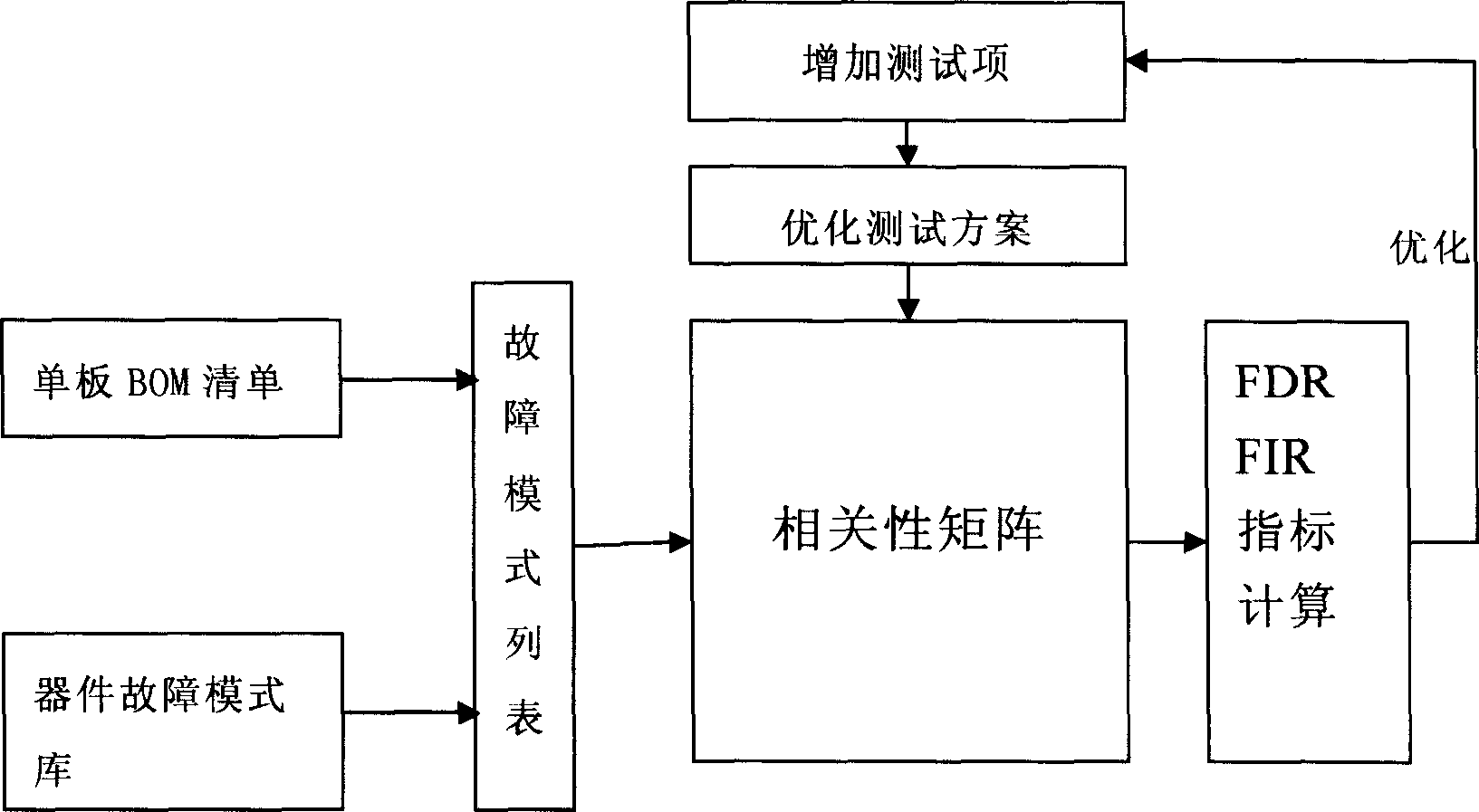

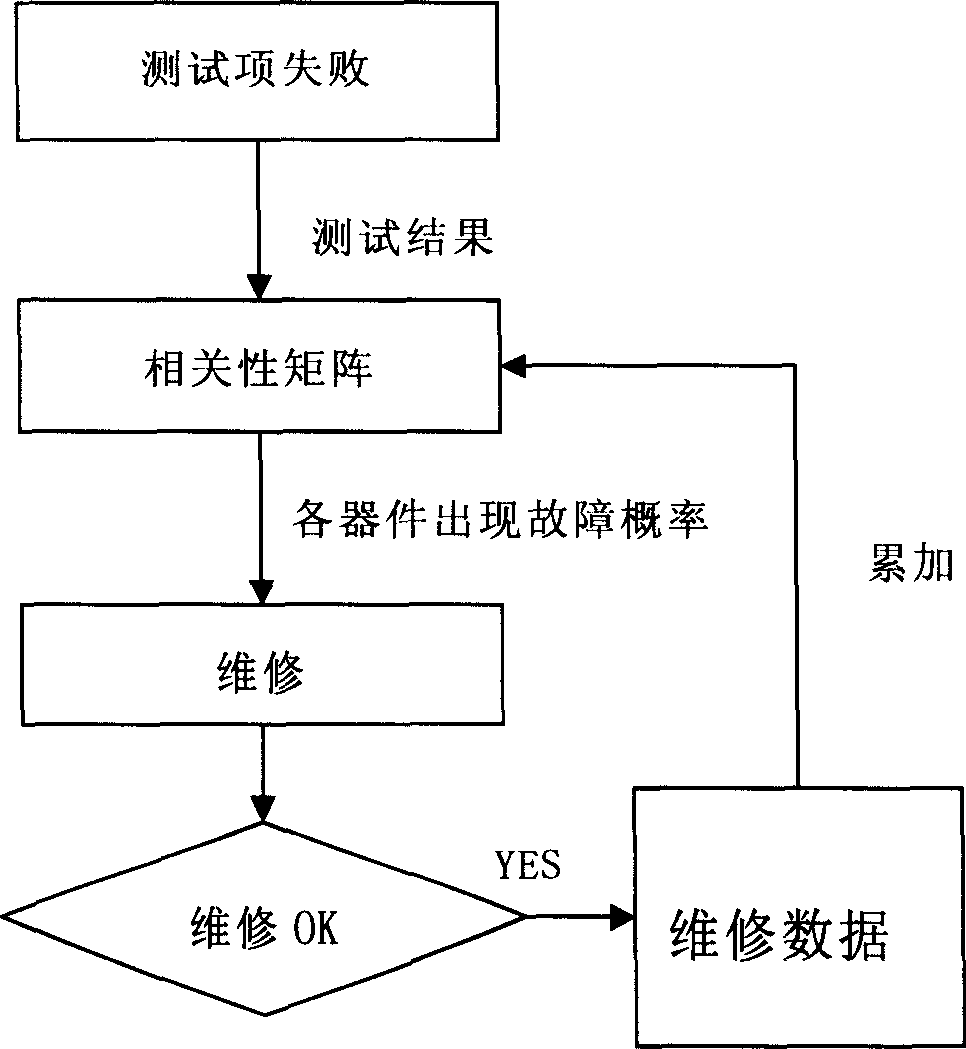

[0047] The present invention provides a fault location method, which can locate a specific device when a single board fails, and the method has the function of continuously correcting the location capability, such as Figure 4 As shown, the implementation of this method is as follows:

[0048] Step 1. For single board modeling, establish the corresponding relationship between failure modes and test items. The so-called failure mode refers to the possible failure of each device on the board, using the following correlation matrix form:

[0049]

[0050] Among them, the i-th row matrix Fi is:

[0051] [di1 di2… dij]

[0052] Indicates the correlation between the failure mode Fi and each test item, which indicates which test items fail when the device fails;

[0053] The failure mode Fi is established as follows:

[0054] (1.1) Obtain the device failure mode library, which contains all devices and all failure modes of the device;

[0055] (1.2) Obtain the device l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More