Package substrate

A technology for packaging substrates and substrates, which is used in the manufacture of multilayer circuits, electrical connection of printed components, printed circuit components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

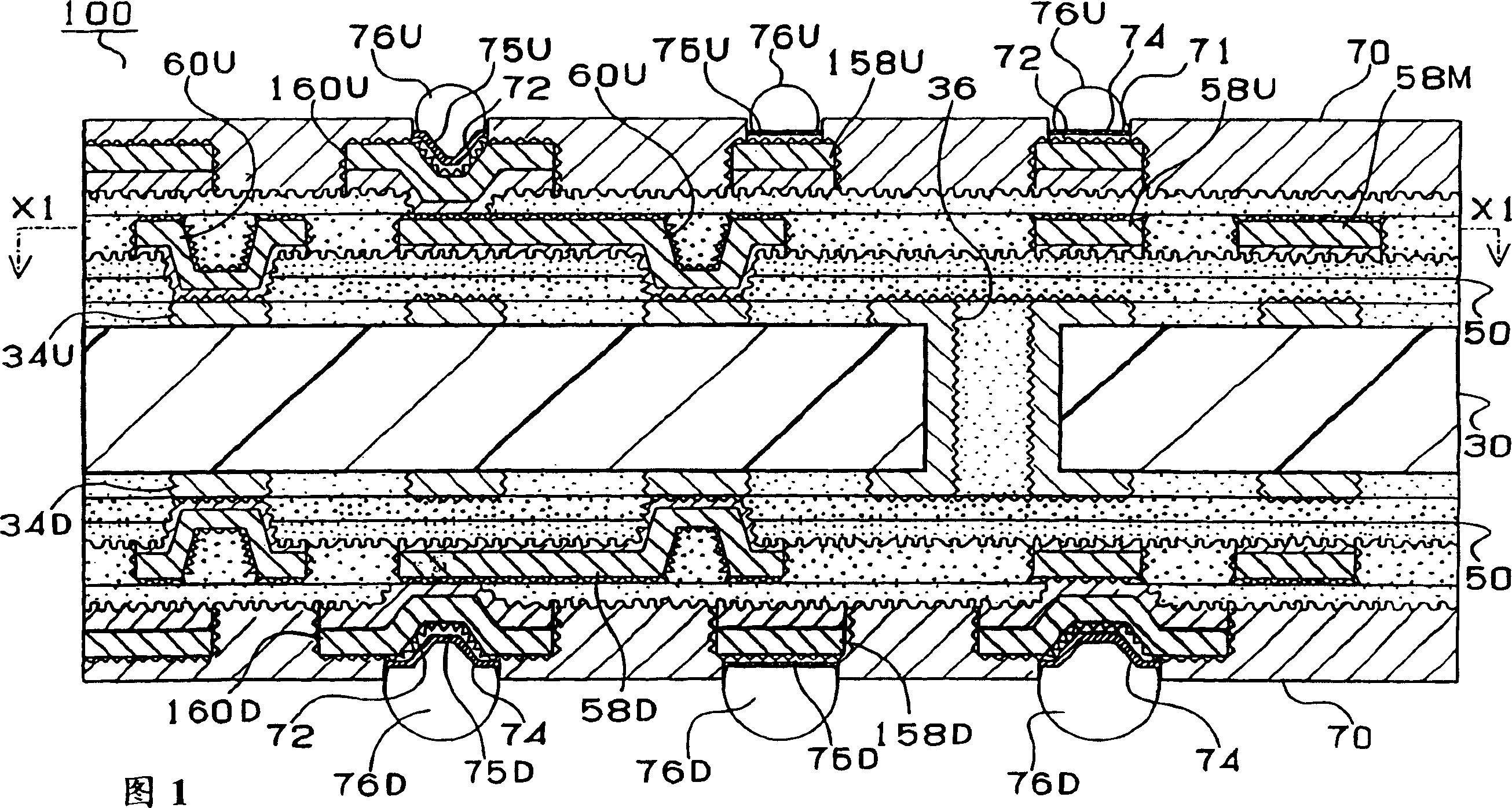

[0046] (first embodiment)

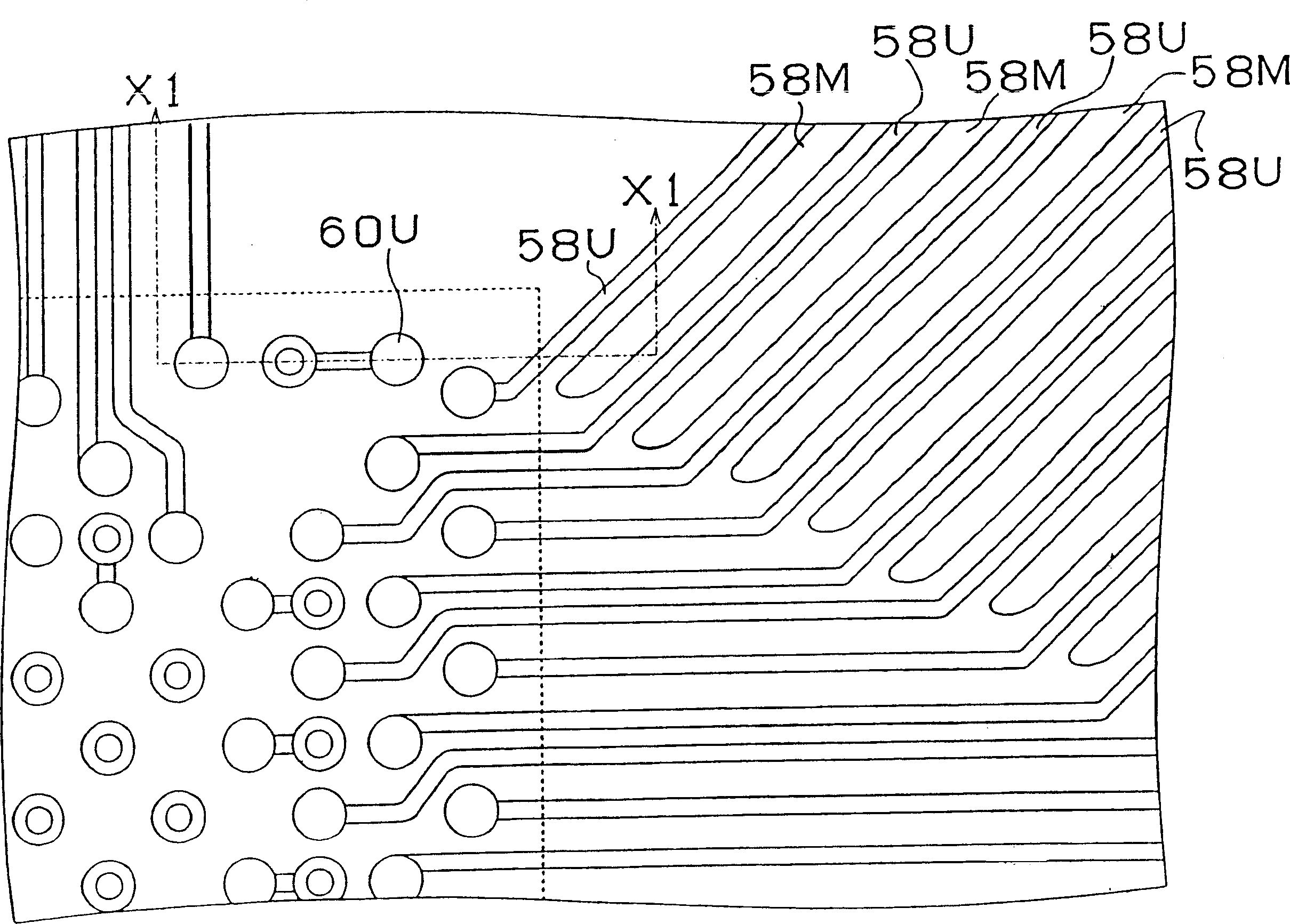

[0047] The configuration of a package substrate according to a first embodiment of the present invention will be described with reference to FIG. 1 . 1 shows a cross-sectional shape of a package substrate according to a first embodiment. This package substrate constitutes a so-called integrated circuit package and is used to mount an integrated circuit (not shown) on a motherboard (not shown) in a state where it is placed thereon. )superior. The package substrate is provided with soldering bumps 76U for connecting to the soldering bump side of the integrated circuit on the upper side, and soldering bumps 76D for connecting with the soldering bumps of the motherboard on the lower side. The boards play the role of transmitting signals, etc. and relaying the power supply from the motherboard.

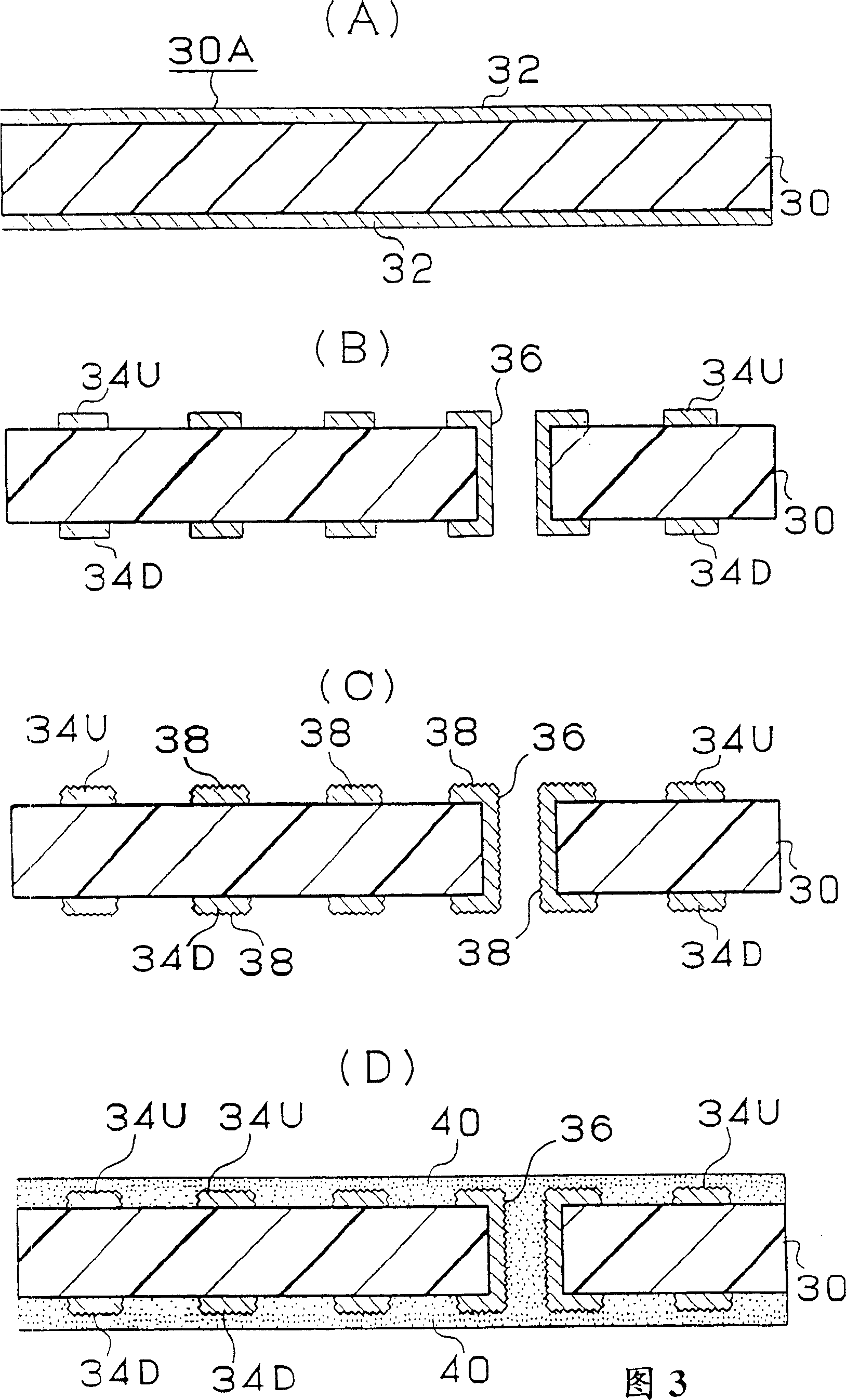

[0048] Inner layer copper patterns 34U, 34D as ground layers are formed on the upper and lower surfaces of the chip substrate 30 of the package substrate. In...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com