Device and method for transmitting data in asynchronous clock domain

An asynchronous clock and domain transmission technology, applied in the field of data transmission, can solve the problems of impossible adjustment of data transmission delay in FIFO, FIFO can not meet transmission delay error, FIFO can not detect and other problems, to achieve simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the purpose, technical solution and advantages of the present invention clearer, the following examples are given to further describe the present invention in detail.

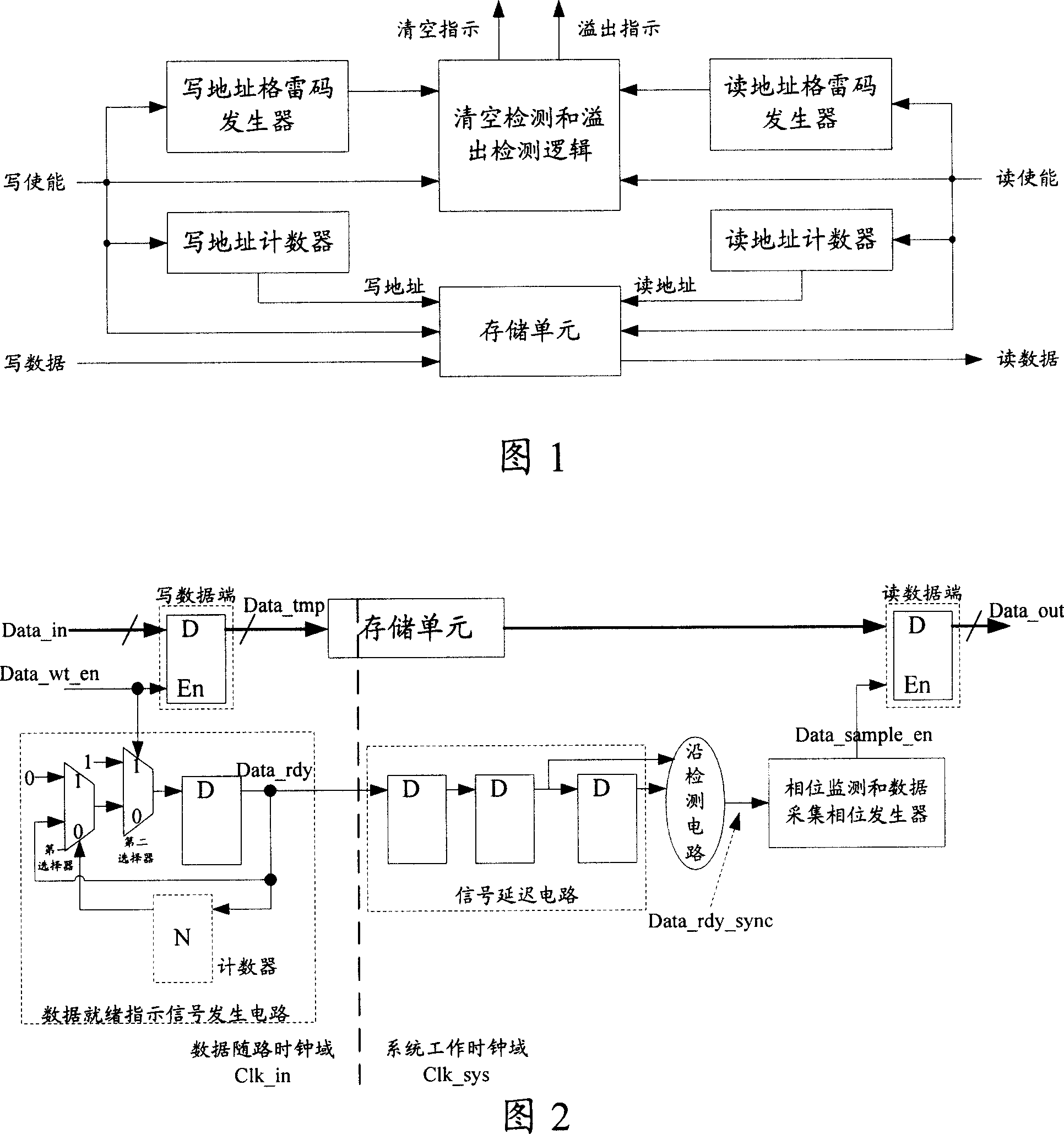

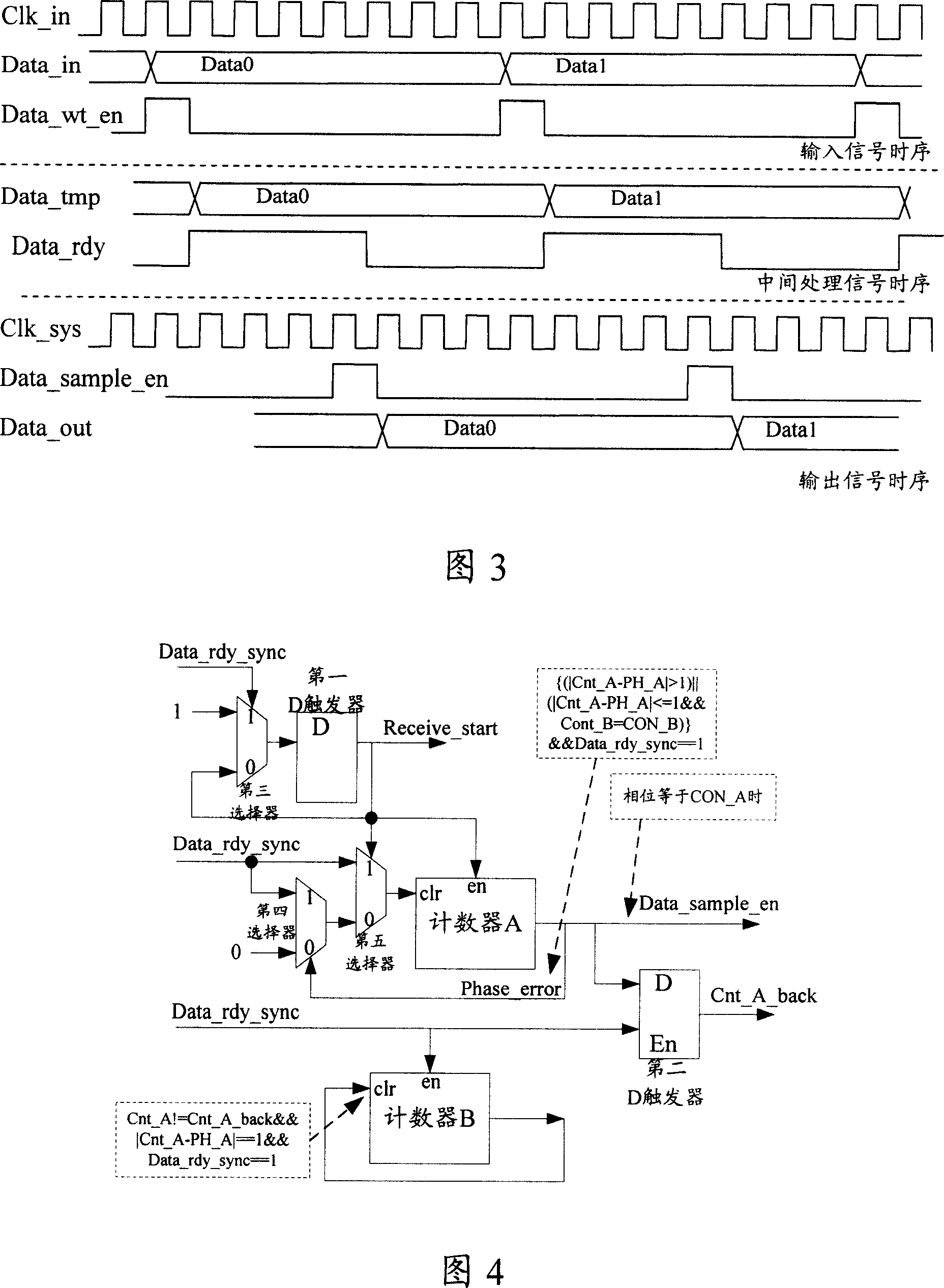

[0023] With reference to Fig. 2, the device that the present invention adopts comprises writing data end, storage unit, data ready indication signal generation circuit, signal delay circuit, edge detection circuit, phase monitoring and data acquisition phase generator, and read data end. Among them, the sender's write data terminal and data ready indication signal generation circuit work in the data follower clock domain Clk_in, and the receiver's signal delay circuit, edge detection circuit, phase monitoring and data acquisition phase generator, and read data terminal all work Work in the system clock domain Clk_sys. The structure and function of each part are introduced respectively below.

[0024] The write data terminal includes a D flip-flop, and when the write enable signal Data_w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More