Machine instruction for enhanced control of multiple virtual processor systems

a virtual processor and machine instruction technology, applied in the field of electronic systems, can solve the problems of reducing the overall processor efficiency, wasting otherwise usable cycles of the physical processor, and limiting the thread switching process in these experimental mvp systems, so as to facilitate the improvement of the processor efficiency and clean and efficient

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

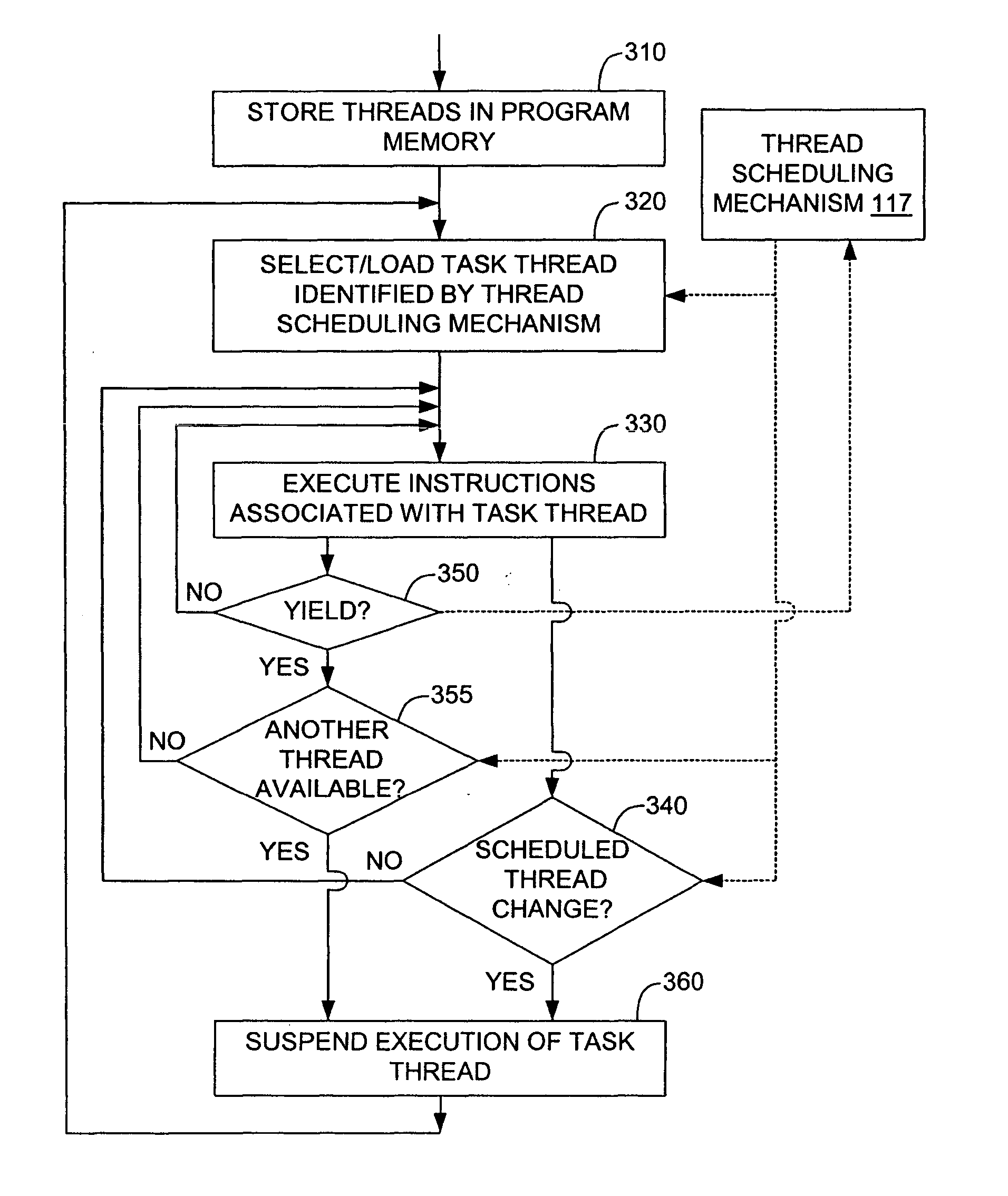

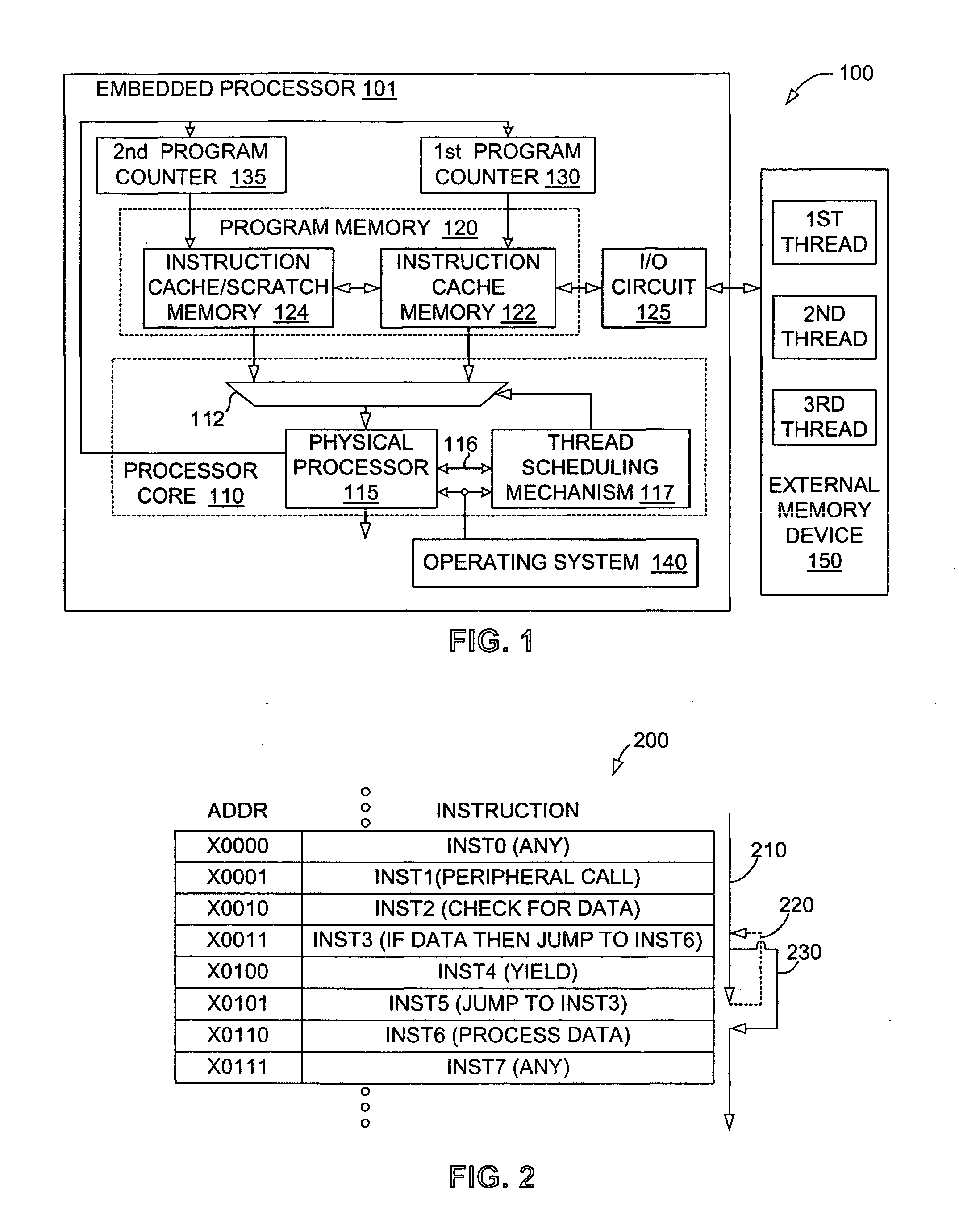

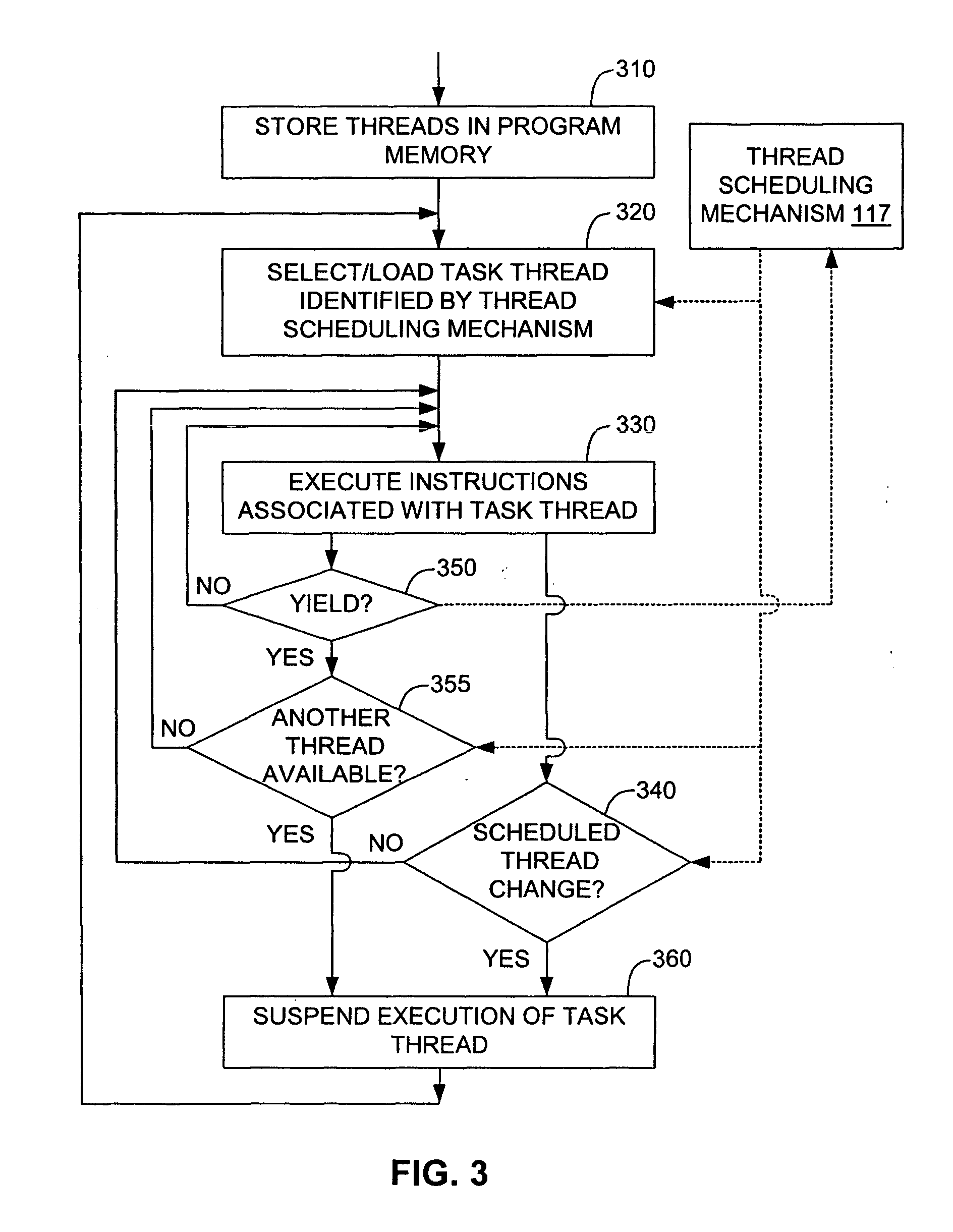

[0017] The concepts of multi-threading and multiple virtual processing are known in the processor art, and generally refer to processor architectures that utilize a single physical processor to serially execute two or more “virtual processors”. The term “virtual processor” refers to a discrete thread and physical processor operating state information associated with the thread. The term “thread” is well known in the processor art, and generally refers to a set of related machine (program) instructions (i.e., a computer or software program) that is executed by the physical processor. The operating state information associated with each virtual processor includes, for example, status flags and register states of the physical processor at a particular point in the thread execution. For example, an MVP system may include two virtual processors (i.e., two threads and two associated sets of operating state information). When a first virtual processor is executed, its associated operating ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More