Memory control apparatus executing prefetch instruction

a memory control apparatus and instruction technology, applied in the direction of memory adressing/allocation/relocation, instruments, computing, etc., can solve the problems of reducing the effective bandwidth of the access buffer, losing the significance of the prefetch buffer, and becoming more and more difficult to solve the problem. , to achieve the effect of function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] A preferred embodiment of the present invention is described below in detail by referring to the attached drawings.

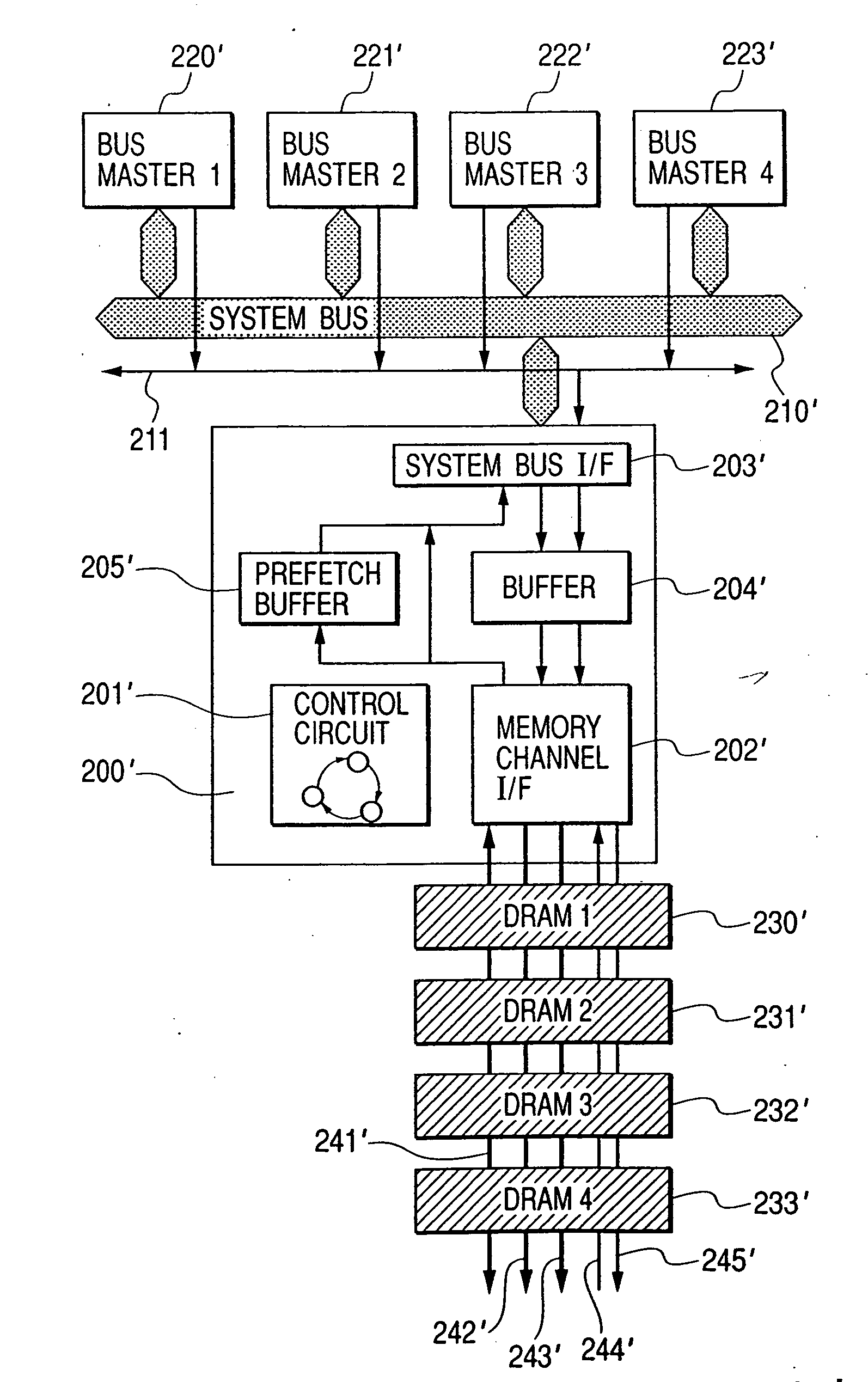

[0041] The first embodiment of the present invention is described below by referring to FIGS. 4 and 5. For comparison, the reference numerals for the same components in FIG. 2 end with ′.

[0042] The difference in FIG. 4 from FIG. 2 is that a system bus 210′ is provided with a signal 211 for identification of a bus master (bus master ID). This is a part of a signal group forming the system bus 210′, but is separately indicated for clear explanation. It can be a signal provided for the system bus 210, or can be newly added. Recently, the integration level of a semiconductor is enhanced, and there is a system LSI in which the entire system is integrated. In a system LSI, a system bus is included in an LSI chip, and causes no problem in system design although a small number of signal lines are added.

[0043] According to the present embodiment, there can be four bus ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com