Method to achieve true fail safe compliance and ultra low pin current during power-up sequencing for mobile interfaces

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

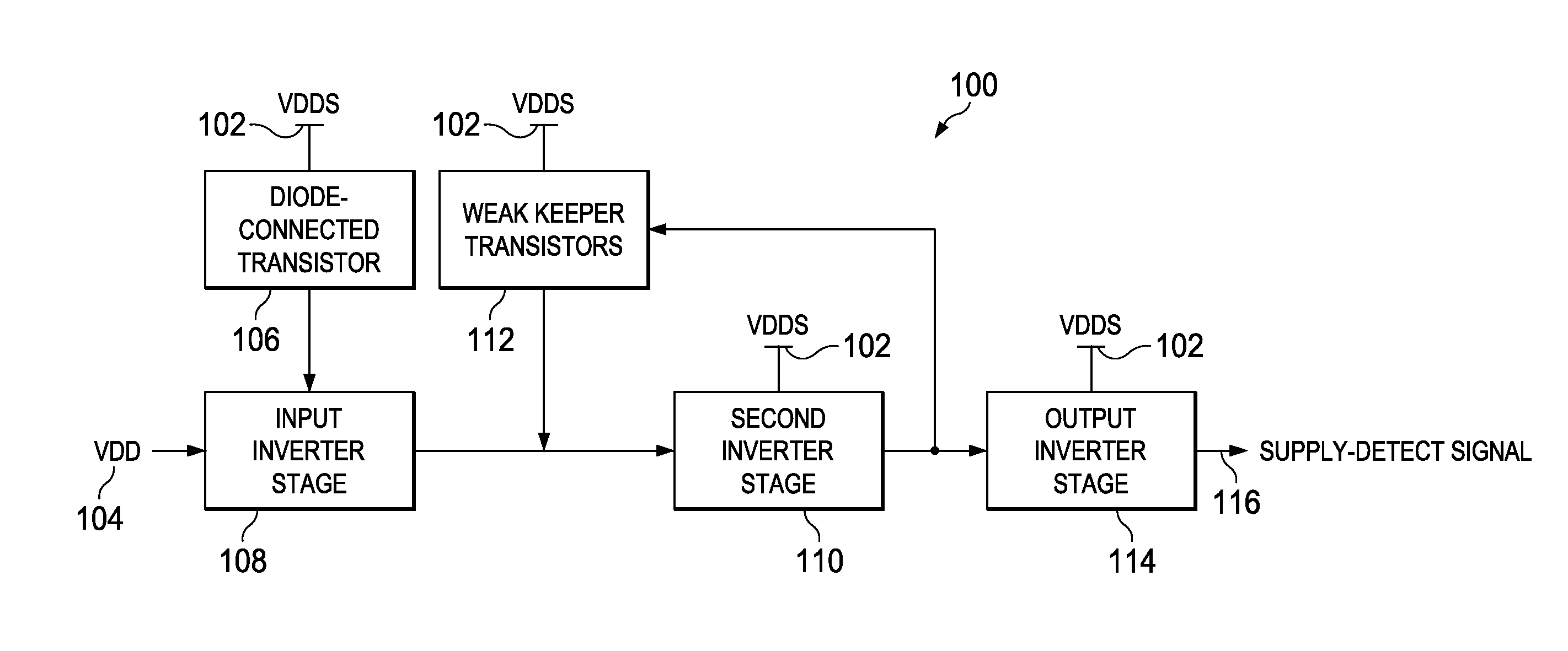

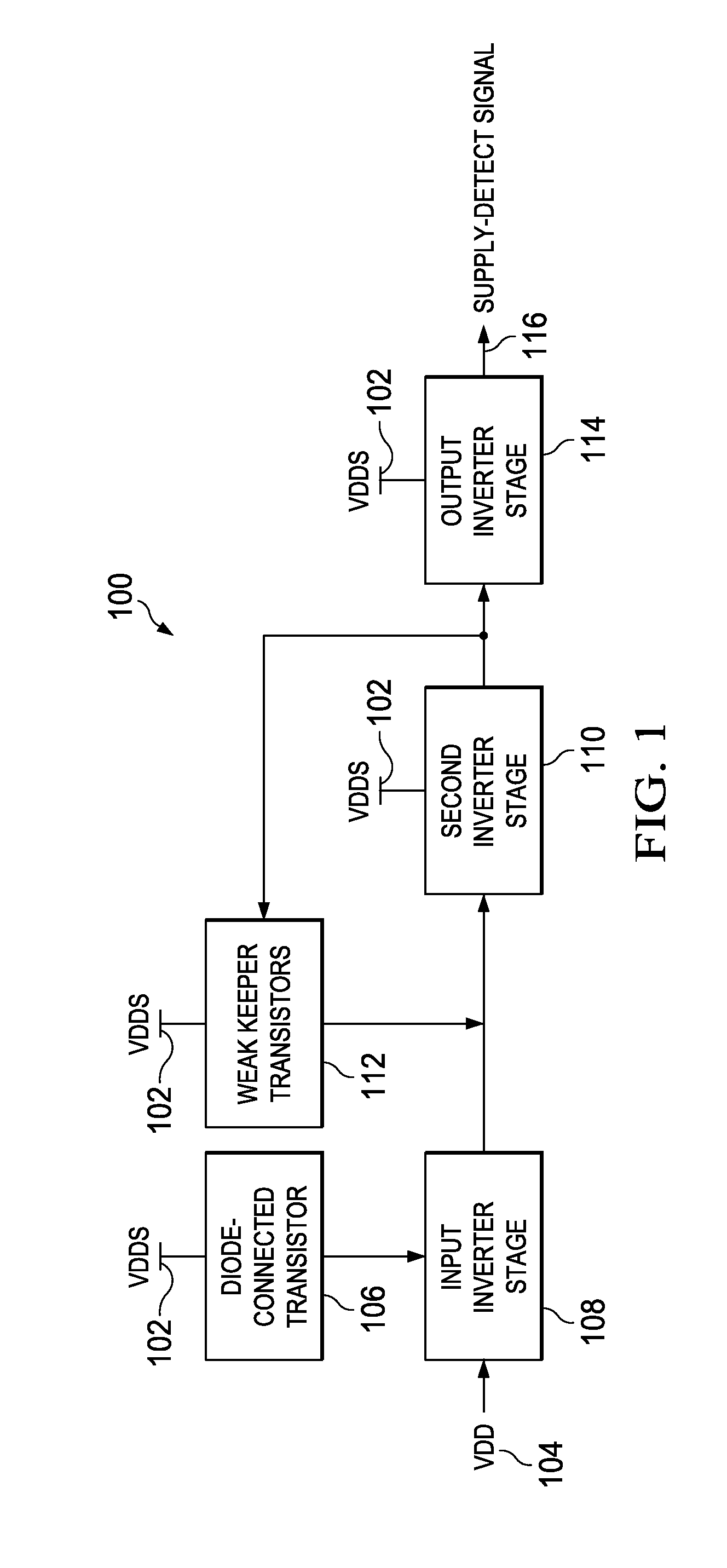

[0021]FIG. 1 illustrates a block diagram of a supply detector cell 100, according to an embodiment. The supply detector cell 100 is powered by an input / output (IO) supply voltage (VDDS) 102 and receives a core supply voltage (VDD) 104 as an input signal. A diode connected transistor 106 is powered by the IO supply voltage (VDDS) 102. The diode connected transistor 106 is one of the following, but not limited to, an NMOS transistor and a PMOS transistor. An input inverter stage 108 is coupled to the diode connected transistor 106. The input inverter stage 108 receives the core supply voltage (VDD) 104. A second inverter stage 110 receives an output of the input inverter stage 108 and is powered by the IO supply voltage (VDDS) 102. A pair of weak keeper transistors 112 is coupled to an output of the second inverter stage 110. The pair of weak keeper transistors 112 are connected in series and powered by the IO supply voltage (VDDS) 102. An output of the pair of weak keeper transistors...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More