Verification complexity reduction via range-preserving input-to-constant conversion

a range-preserving input and constant conversion technology, applied in the field of circuit verification techniques, can solve the problems of complex design, large and complex design complexity, and the complexity of complex verification of such complex systems has grown to be extremely challenging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

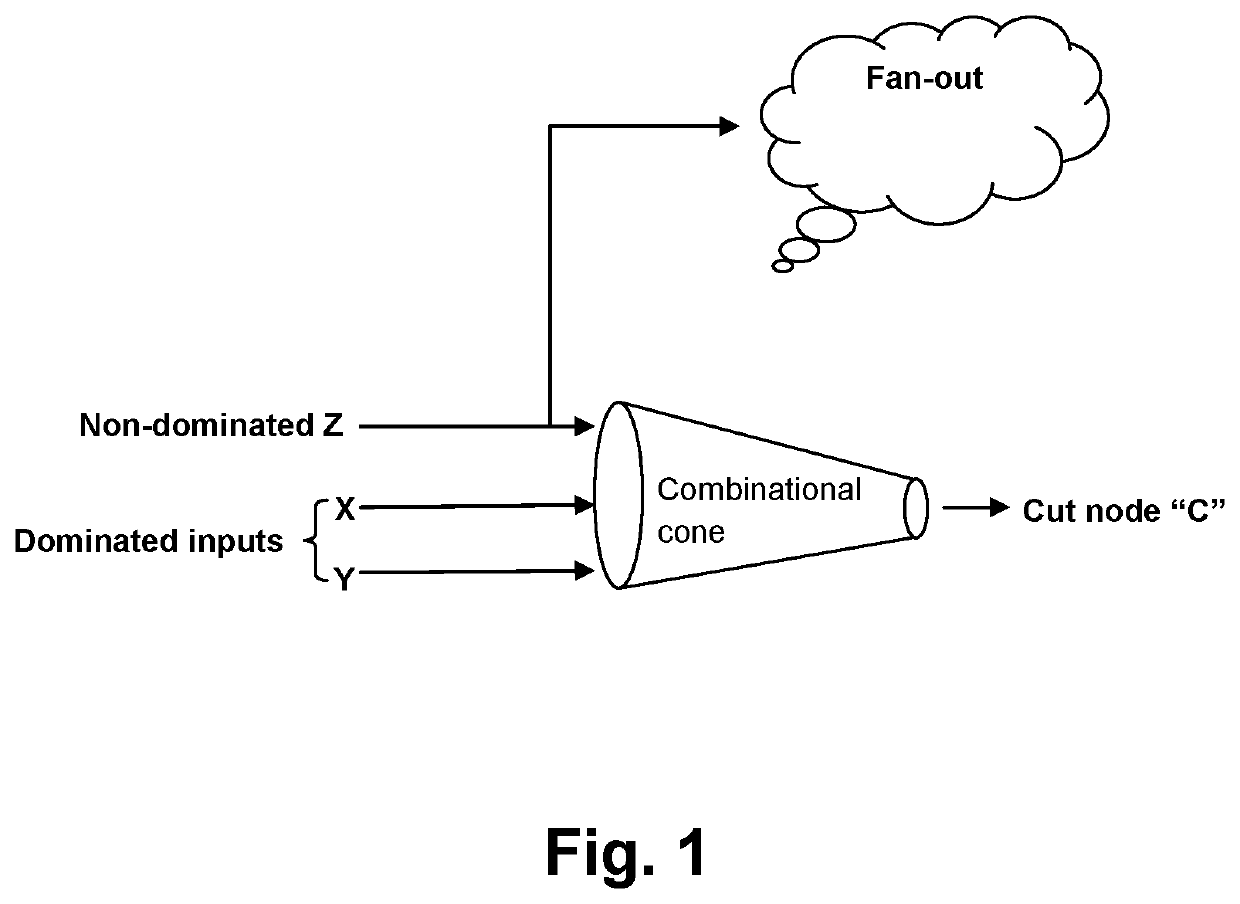

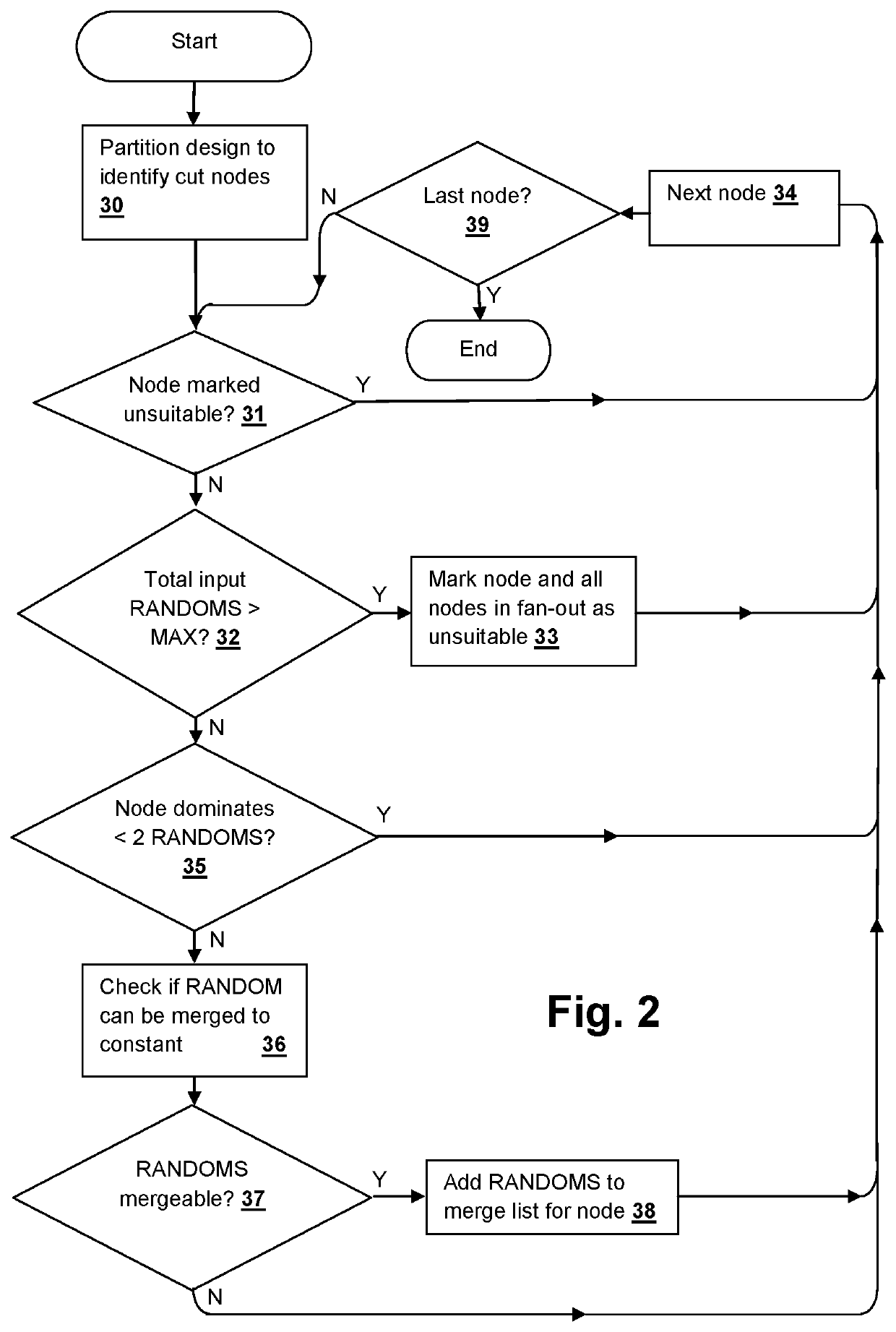

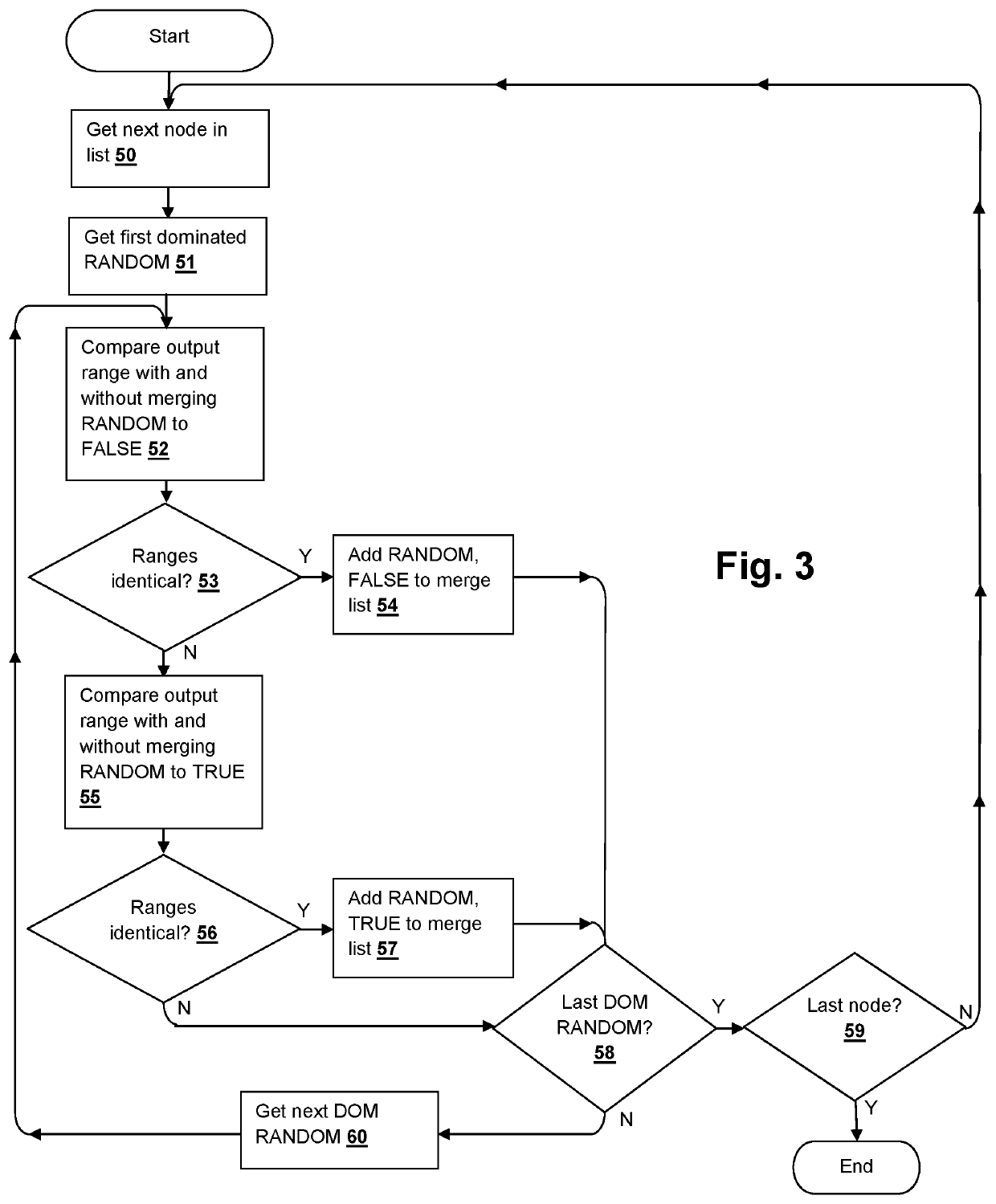

[0017]This disclosure presents novel techniques that reduce the complexity of verification through reducing the size of the testbench. By merging certain primary inputs to constant values, constant propagation and other logic optimization techniques can be applied to further reduce testbench size and verification complexity. Specifically, the disclosed approach identifies the set of primary inputs which are dominated by certain intermediate nodes (dominator set) and determines whether the primary inputs can be merged to 0 / 1, i.e., replaced with a true or false constant value, by comparing range computations on the dominator set (i.e., the set of producible values at the dominator set), with and without candidate reductions. The methods disclosed herein can be considered as computing and comparing two ranges: first leaving the primary inputs intact, then re-computing after merging the primary inputs to either 0 / 1, and if these ranges are equal, the corresponding primary inputs may be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More