Method and apparatus for manipulation of bit fields directly in a memory source

a memory source and bit field technology, applied in the field of computer processors, can solve the problems of processor itself failing, processing an error-prone network data packet, and further reducing the speed and efficiency of the gpc processor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

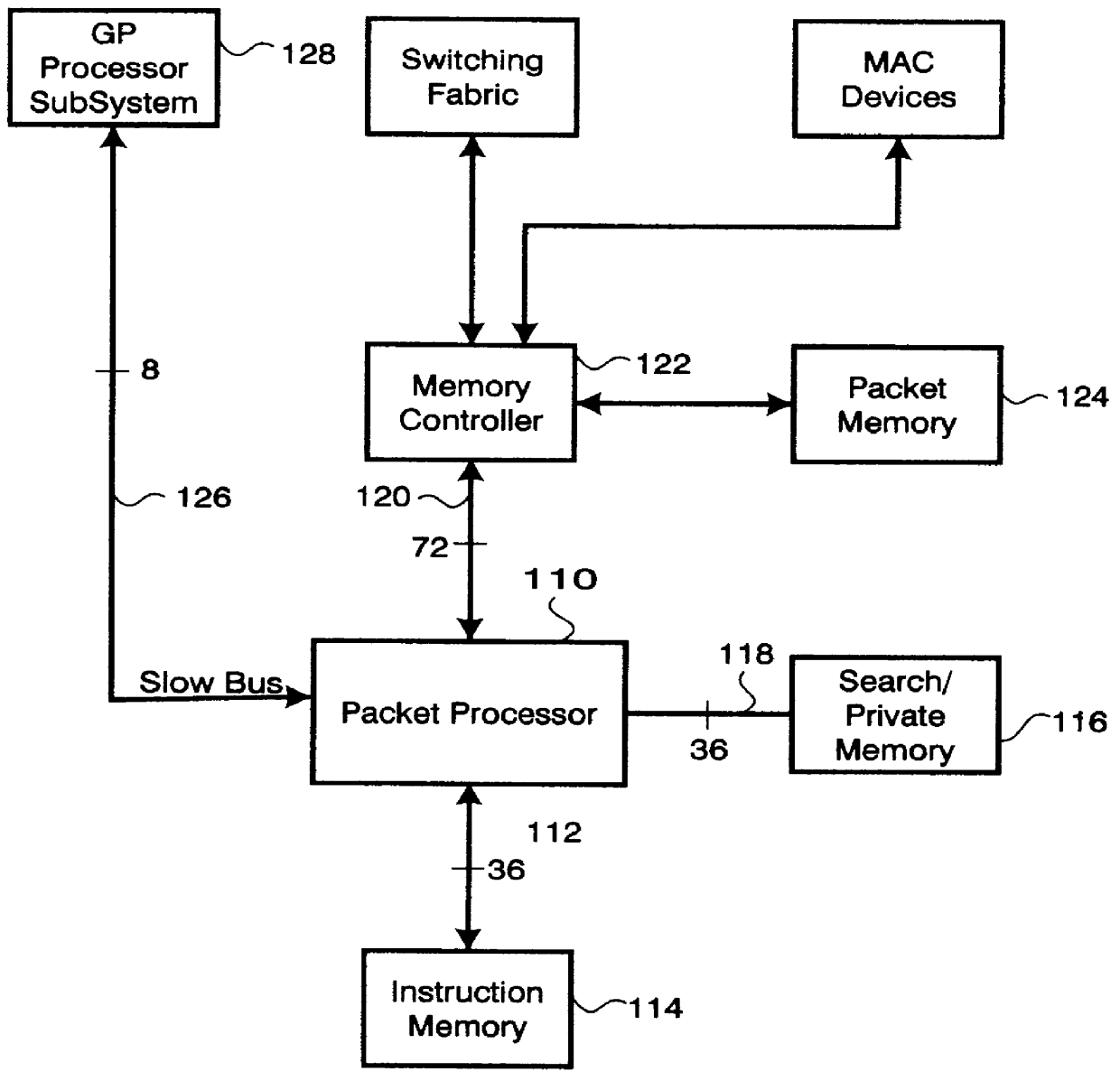

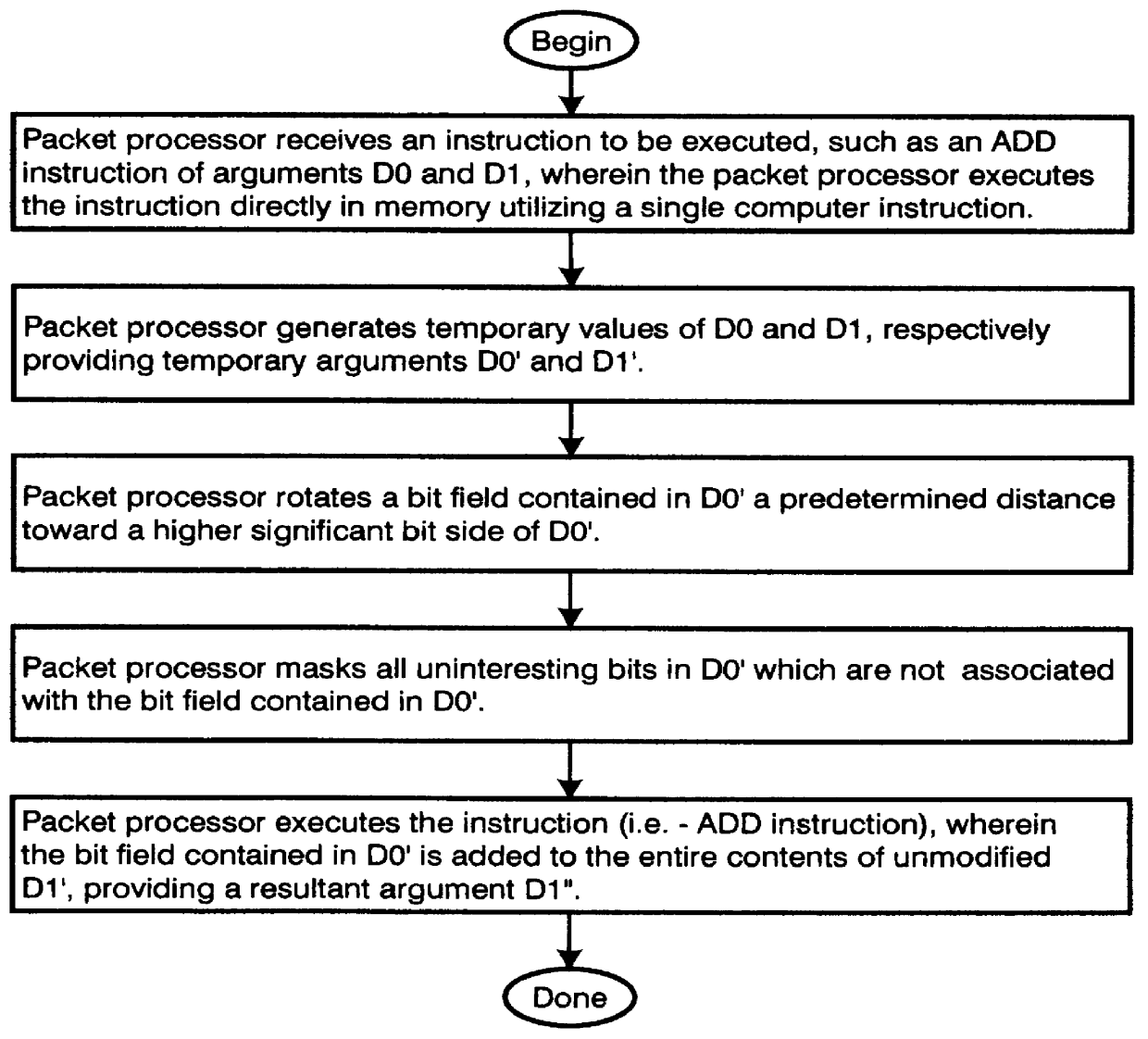

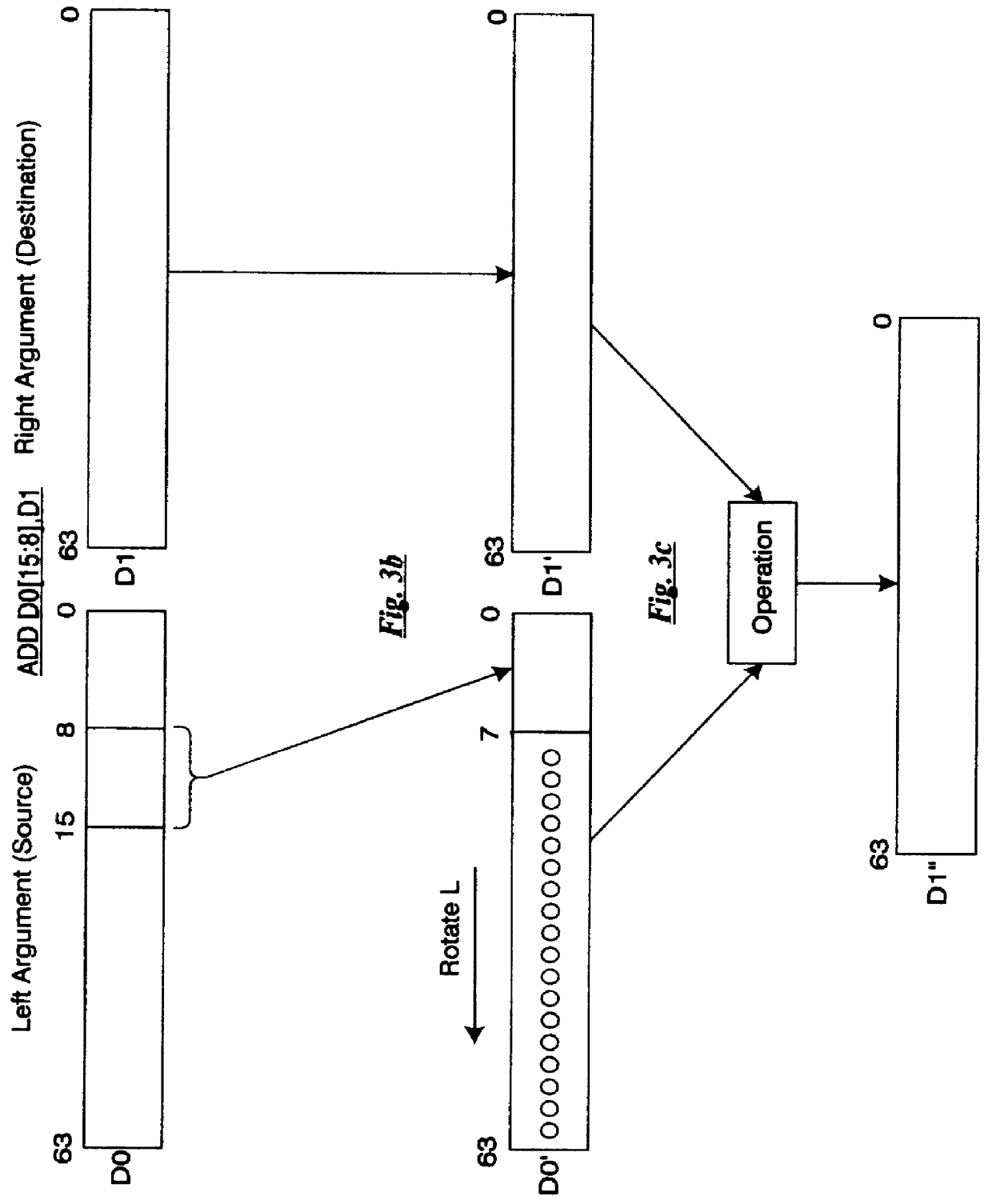

FIG. 3 illustrates a physical representation of the sequence performed on data in field to simple operations, wherein the bit field is aligned and is located on the source argument D0 (left argument). Initially, an instruction is received by the packet processor 110 as to the desired operation that is to be performed with a source argument D0 (left argument) and a destination argument D1 (right argument), for example, "ADD D0[15:8], D1", as illustrated in FIG. 3a. In this instruction, ADD D0[15:8], D1, the bit field is aligned in an individual byte (8 bits) contained between bits 15 and 8 of the source argument DO. As illustrated by the instruction ADD D0[15:8], D1, there are no other required instructions necessary for adding the aligned bit field contained in the source argument D0 to the contents contained in the destination argument D1, rather the packet processor 110 is able to directly manipulate the data in place (memory) without the need to isolate (extract) and reintergrate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More