Two-dimensional redundancy calculation

a two-dimensional redundancy and calculation technology, applied in the field of semiconductor memory devices, can solve the problems of reducing test quality, requiring much more test time, and low yield of insufficient redundancy, and achieve the effect of simplifying the required interaction and less chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023]The present invention is a two-dimensional memory redundancy calculation scheme that provides for a radical reduction in the amount of circuitry required to perform the column redundancy calculation, simplifies the calculation process, and reduces test time.

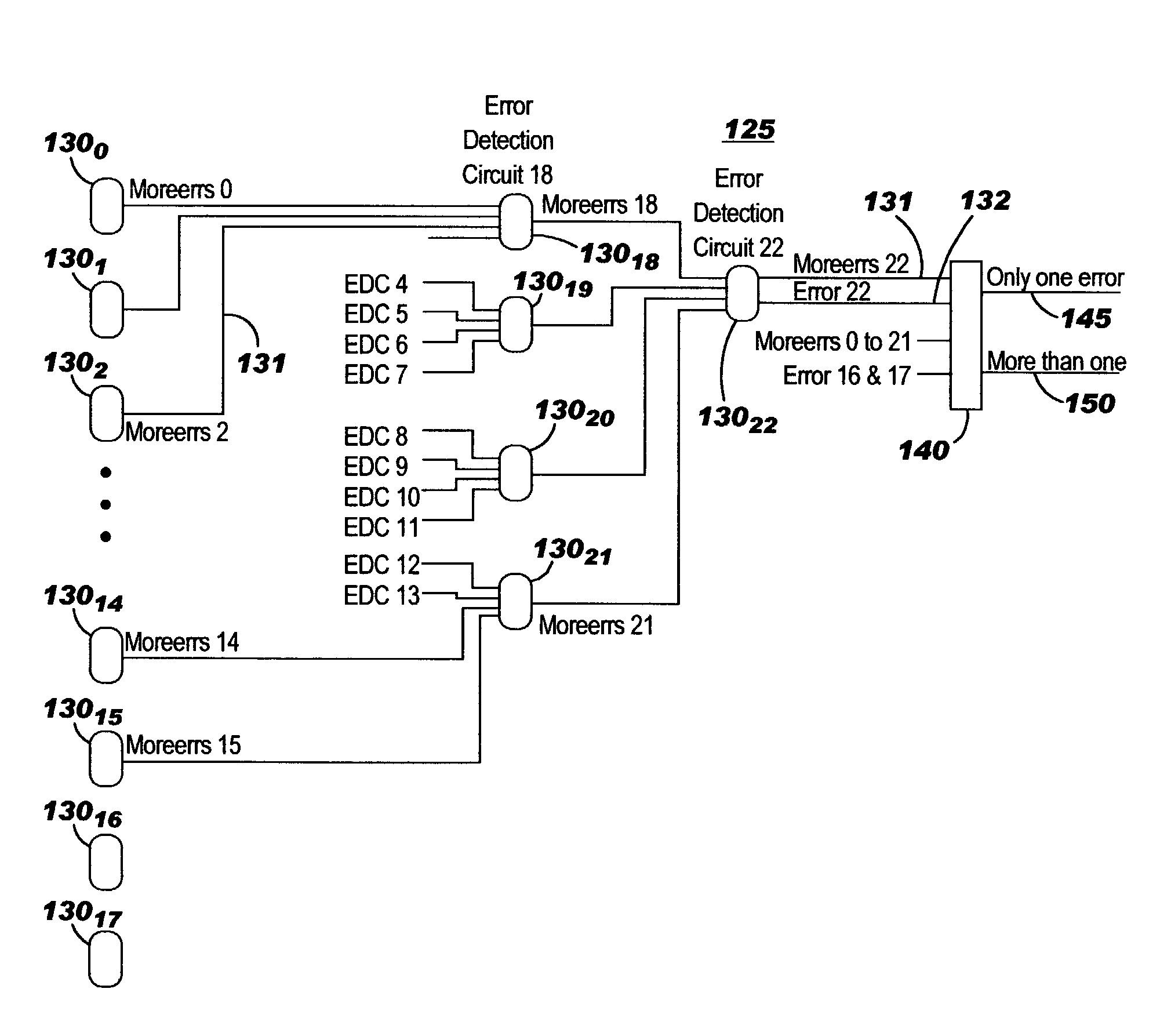

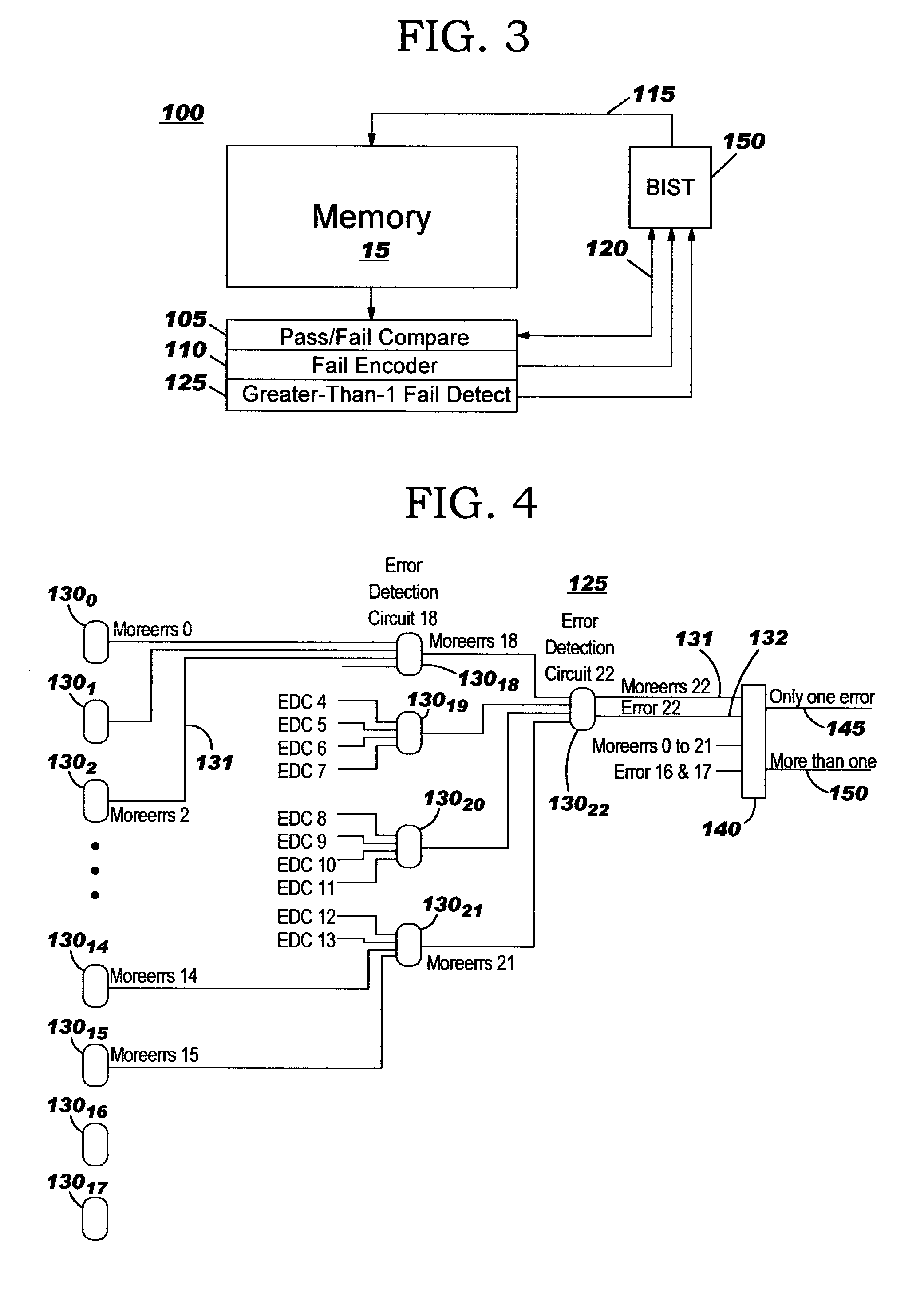

[0024]FIG. 3 illustrates a high level view of the two-dimensional redundancy calculation system 100 according to the present invention. As shown in FIG. 3, the system components include a normal pass / fail compare circuit 105 which may comprise, for example, the row pass / fail circuitry 20 of FIG. 1, a fail encoder device 110, and a greater-than-one fail detect circuit 125. Each of these components interact with memory 115 and, as shown in FIG. 3, may be separate from the BIST circuitry 150, or, as will be described in greater detail herein, may be integrated within the BIST 150. Particularly, the BIST 150 provides data, address, and control inputs 115 to the memory 15. The BIST additionally includes connection 120 with the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More