Patents

Literature

45 results about "Memory redundancy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Redundancy (in a memory) The provision of extra memory cells, usually rows or columns, that can be mapped into the memory array to replace defective (or nonconforming) cells.

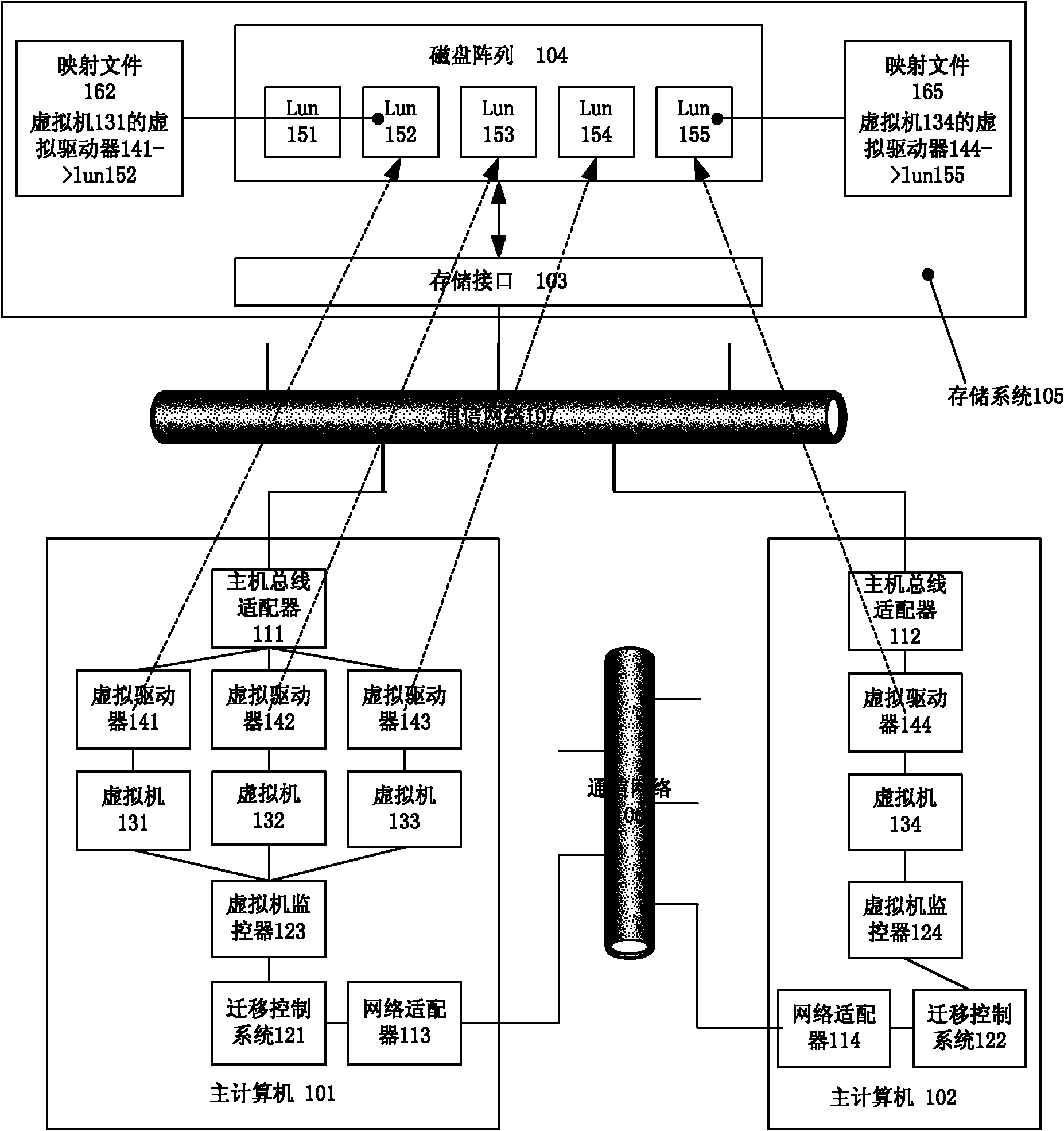

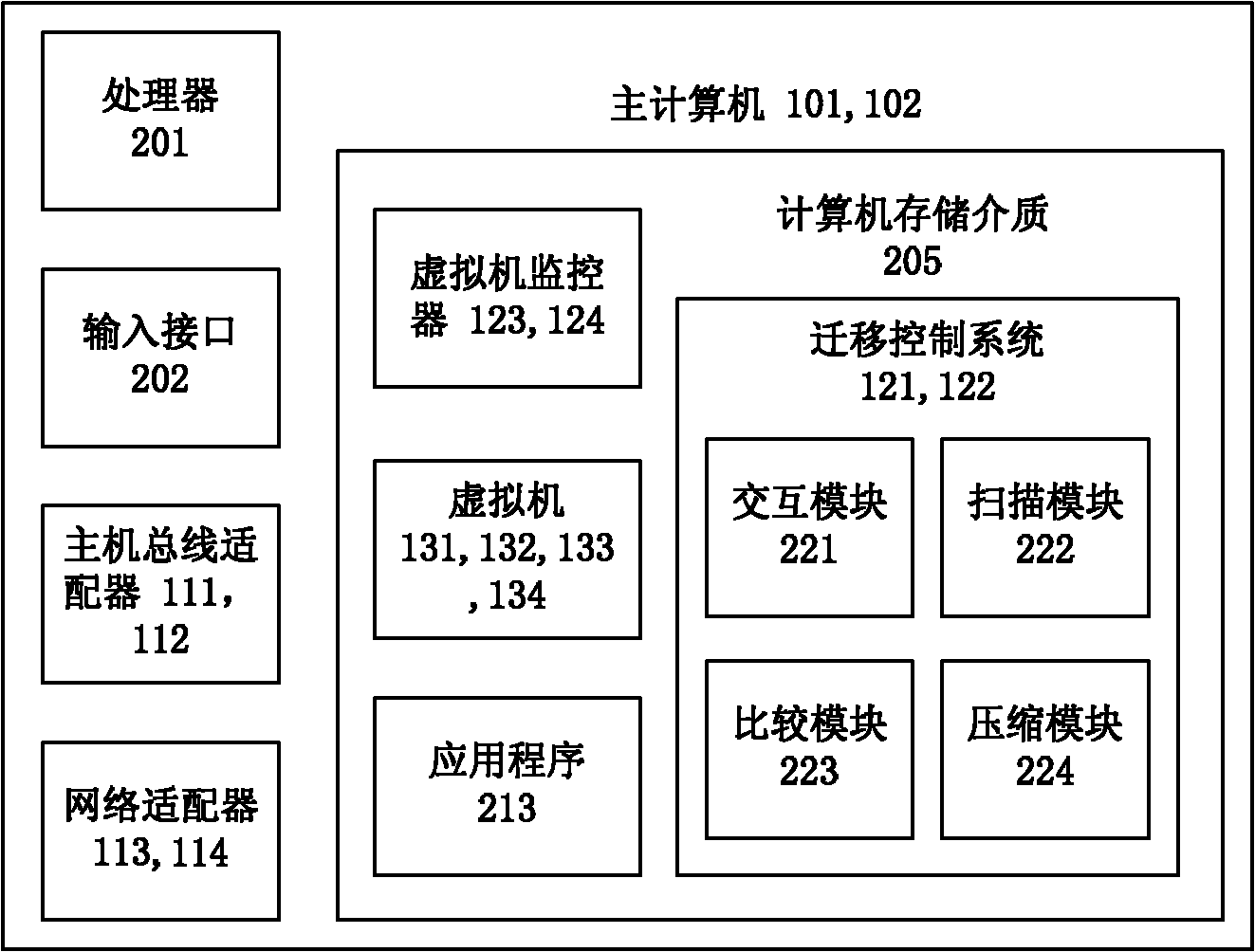

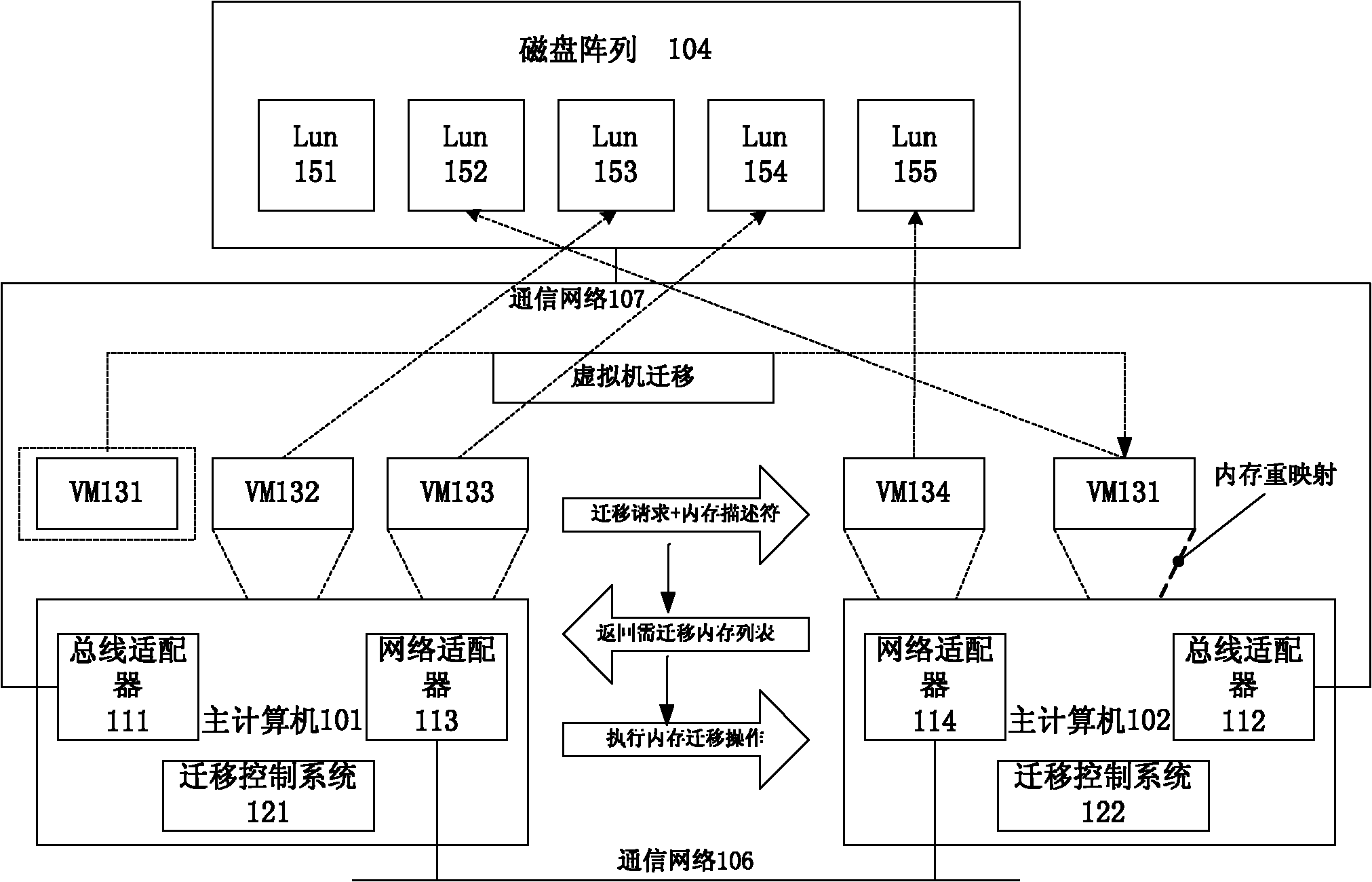

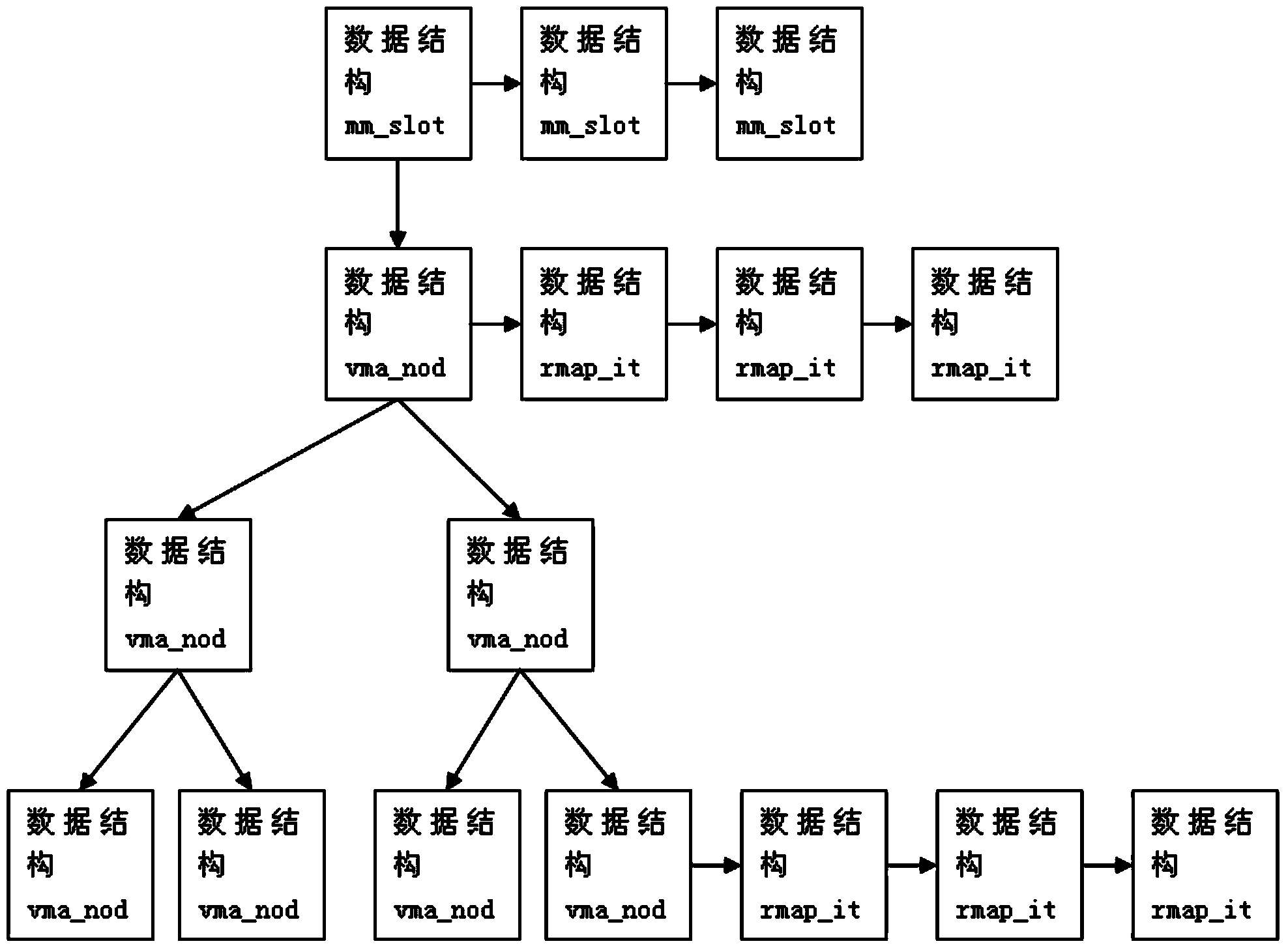

Memory redundancy oriented virtual machine migration device and method

InactiveCN102103524ASave bandwidthImprove migration speedResource allocationTransmissionData compressionData center

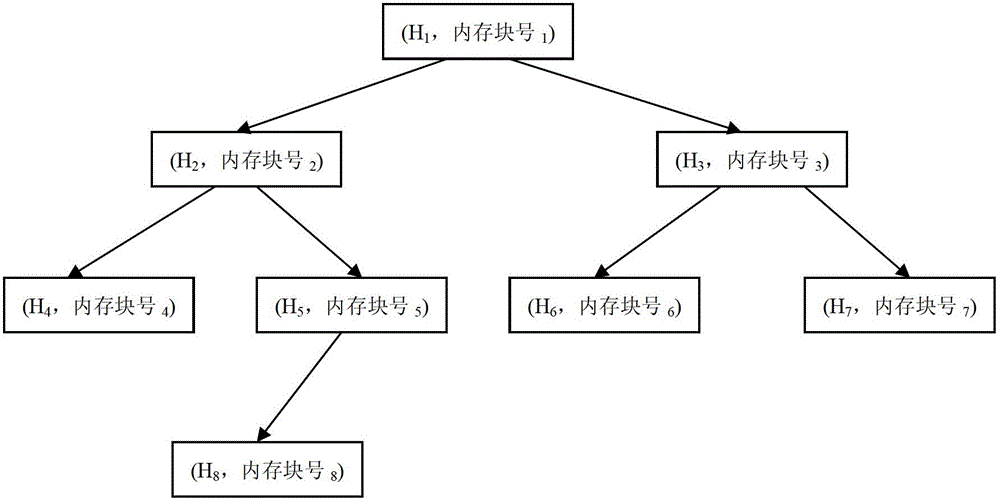

The invention discloses a memory redundancy oriented virtual machine migration device and method, wherein the method comprises the following steps: integrating the characteristics of a virtual machine with memory data redundancy by using a data center, and before the virtual machine is subjected to formal migration, scanning a memory page of the virtual machine so as to obtain a memory descriptor of the virtual machine which is required to be migrated; comparing the obtained memory descriptor with a targeted-node memory page so as to obtain part of memory page list of the virtual machine which is required to be migrated; and according to the obtained memory page list, canceling the transmission of redundant memories, and reducing the transmission quantity of data for migration by using a data compression technology. Therefore, by using the device and method disclosed by the invention, in the process of virtual machine migration with the purpose of saving the memory resources of the data center, the network load can be reduced as far as possible, and the overall resource utilization ratio of the data center can be improved.

Owner:HUAWEI TECH CO LTD

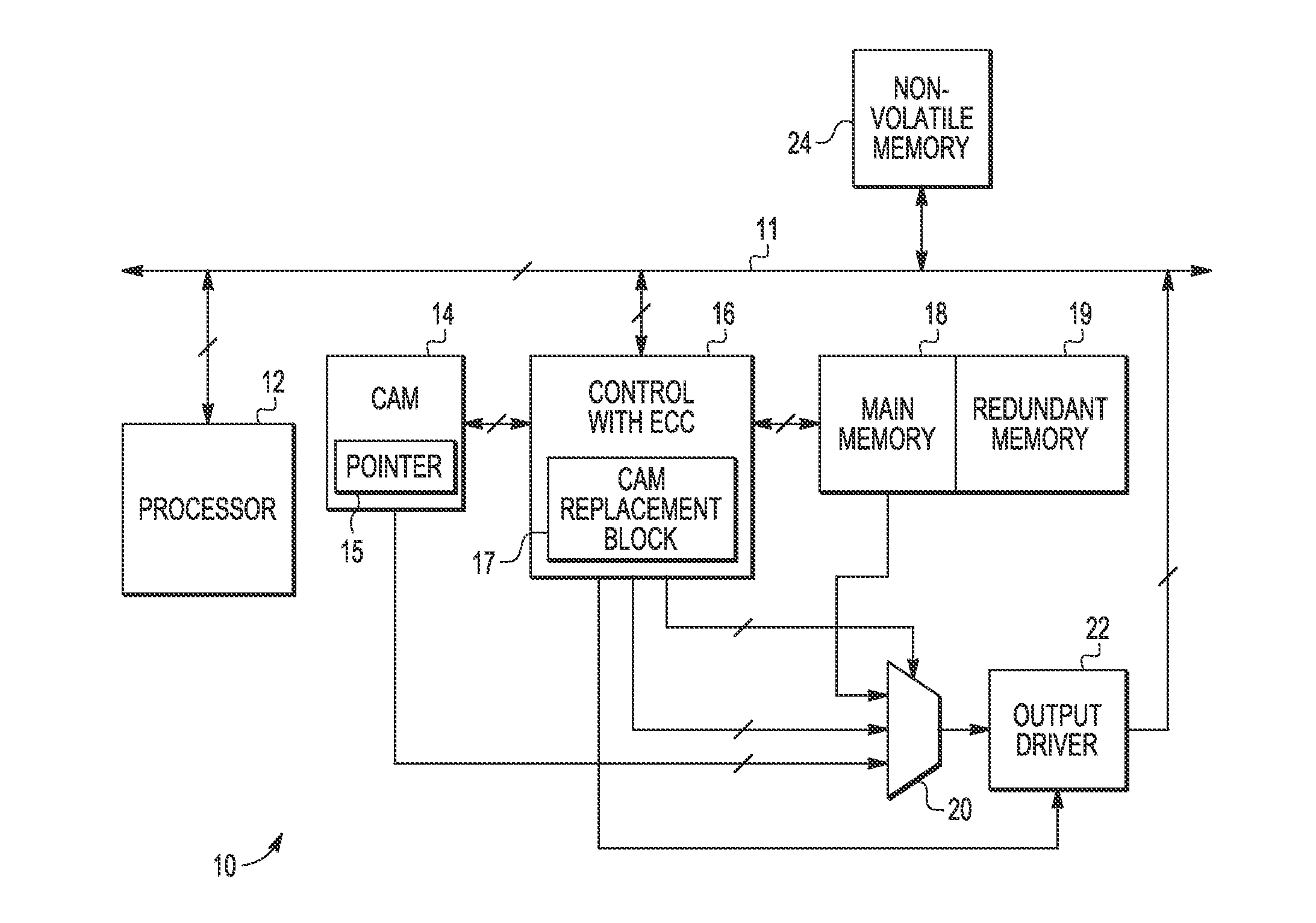

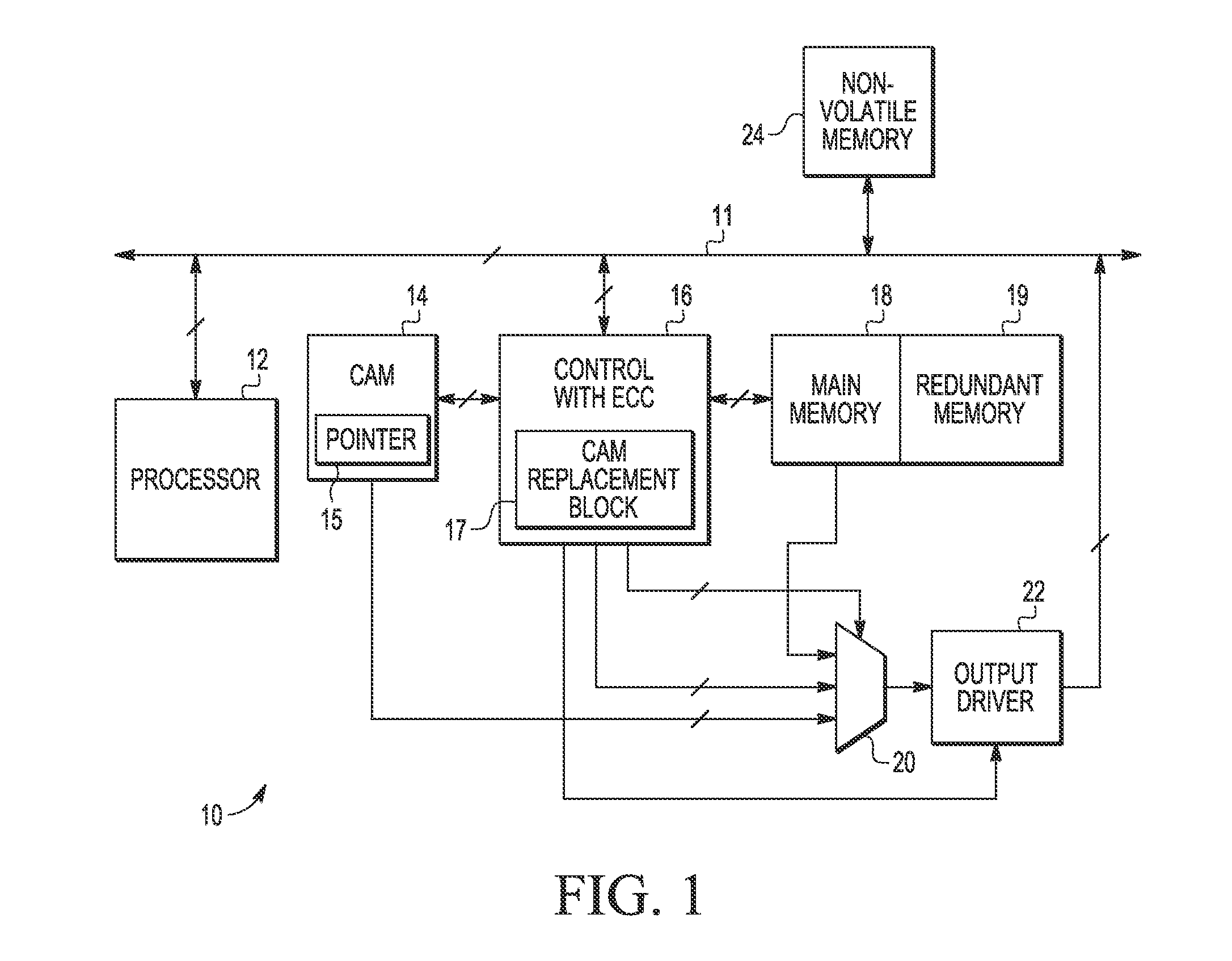

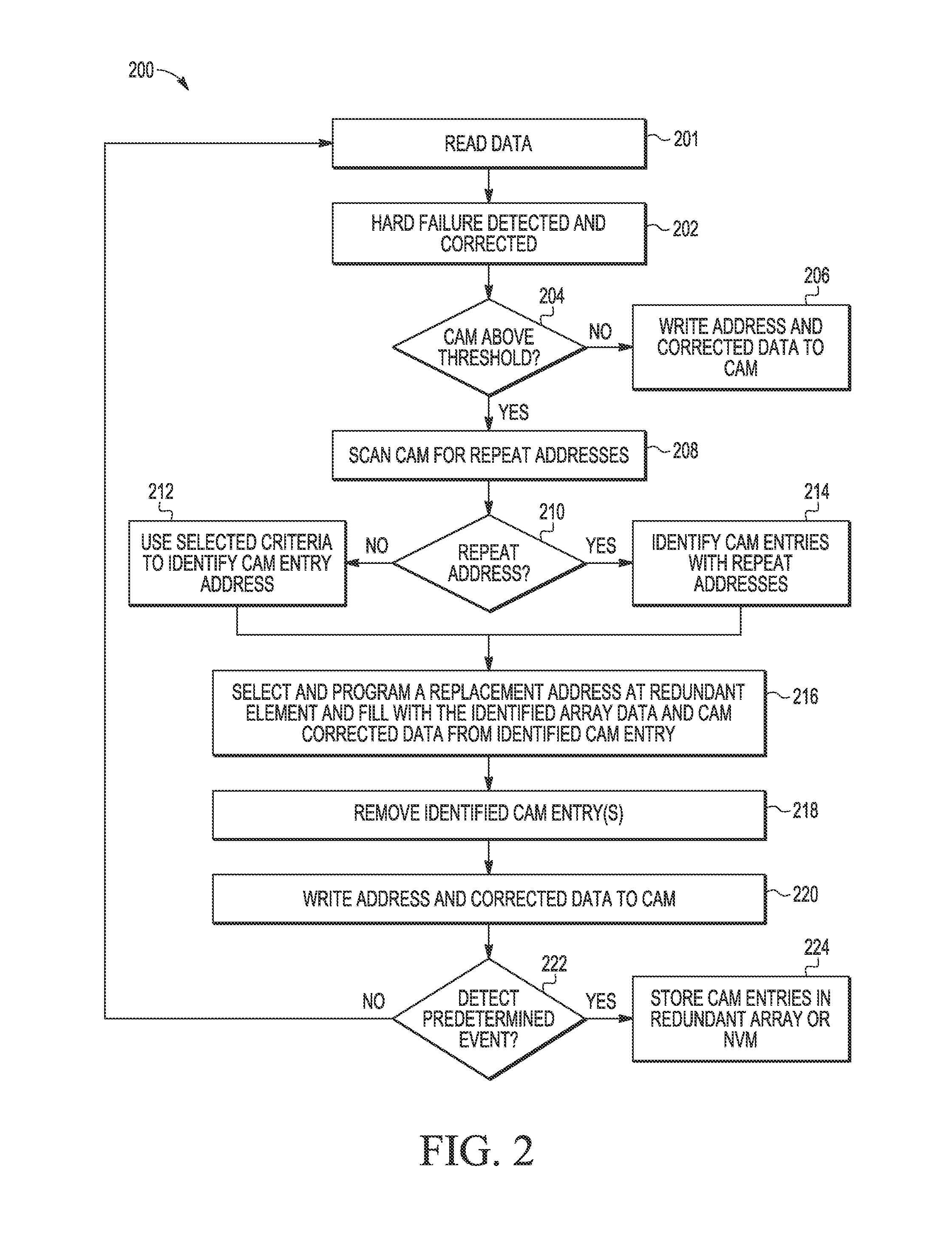

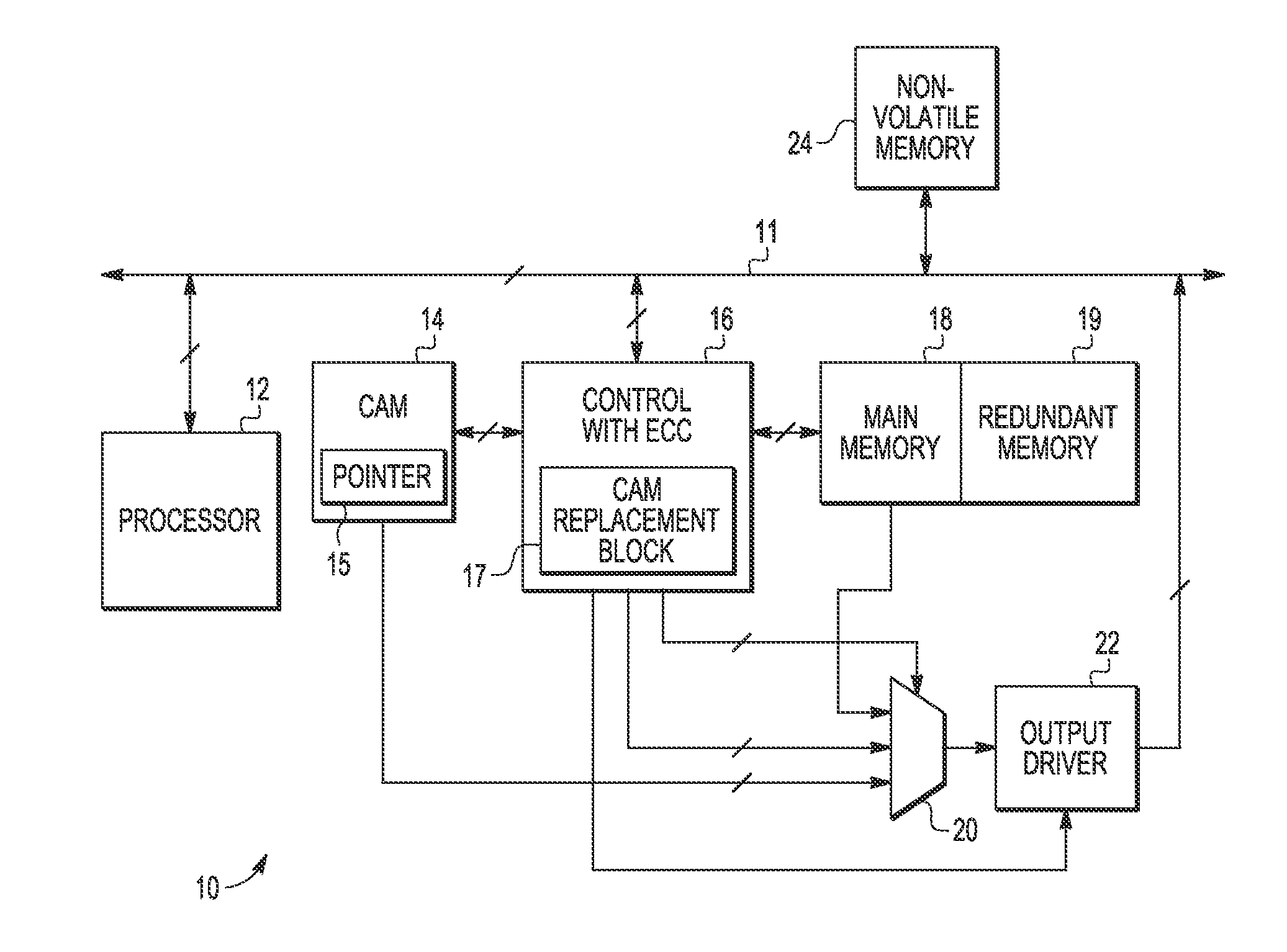

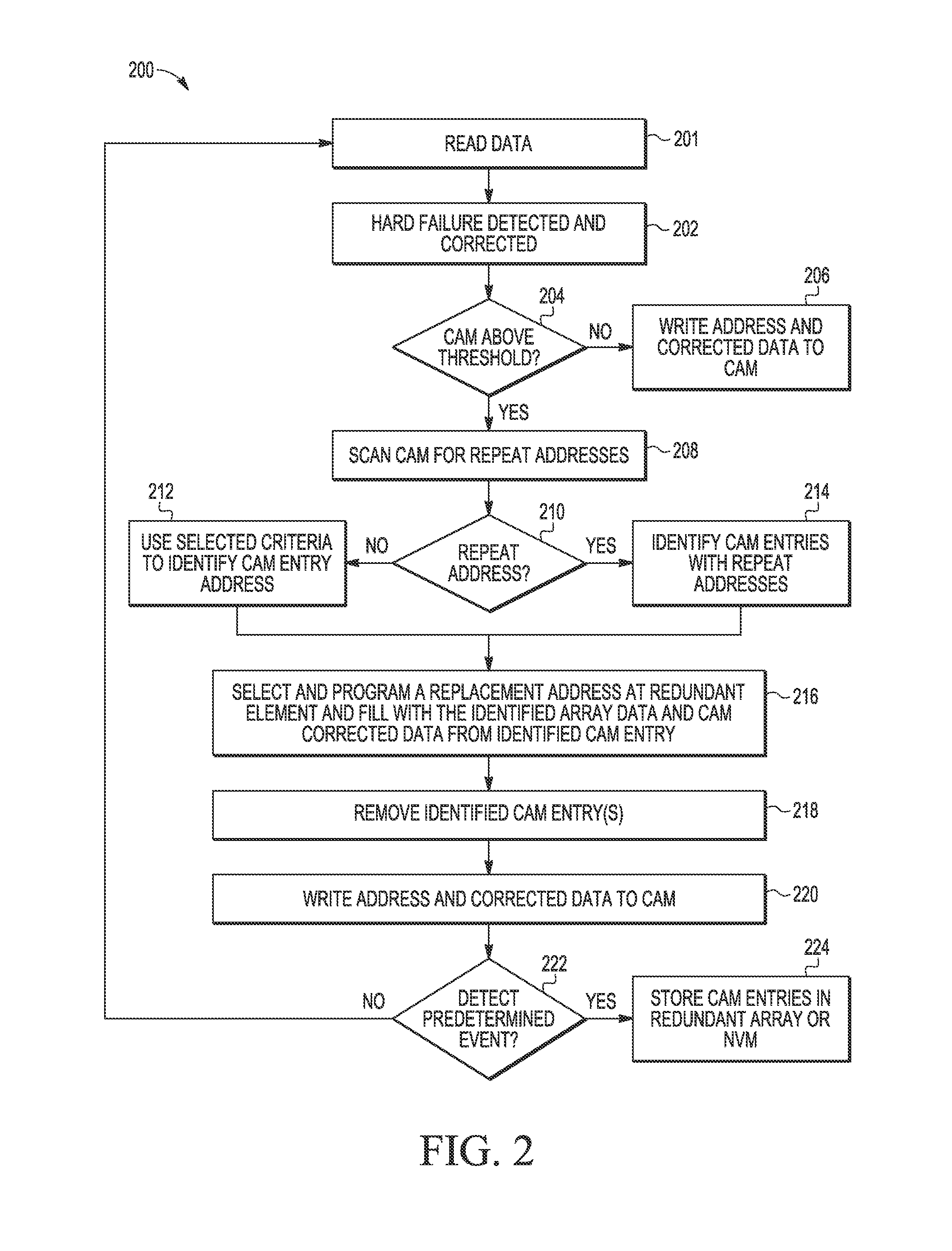

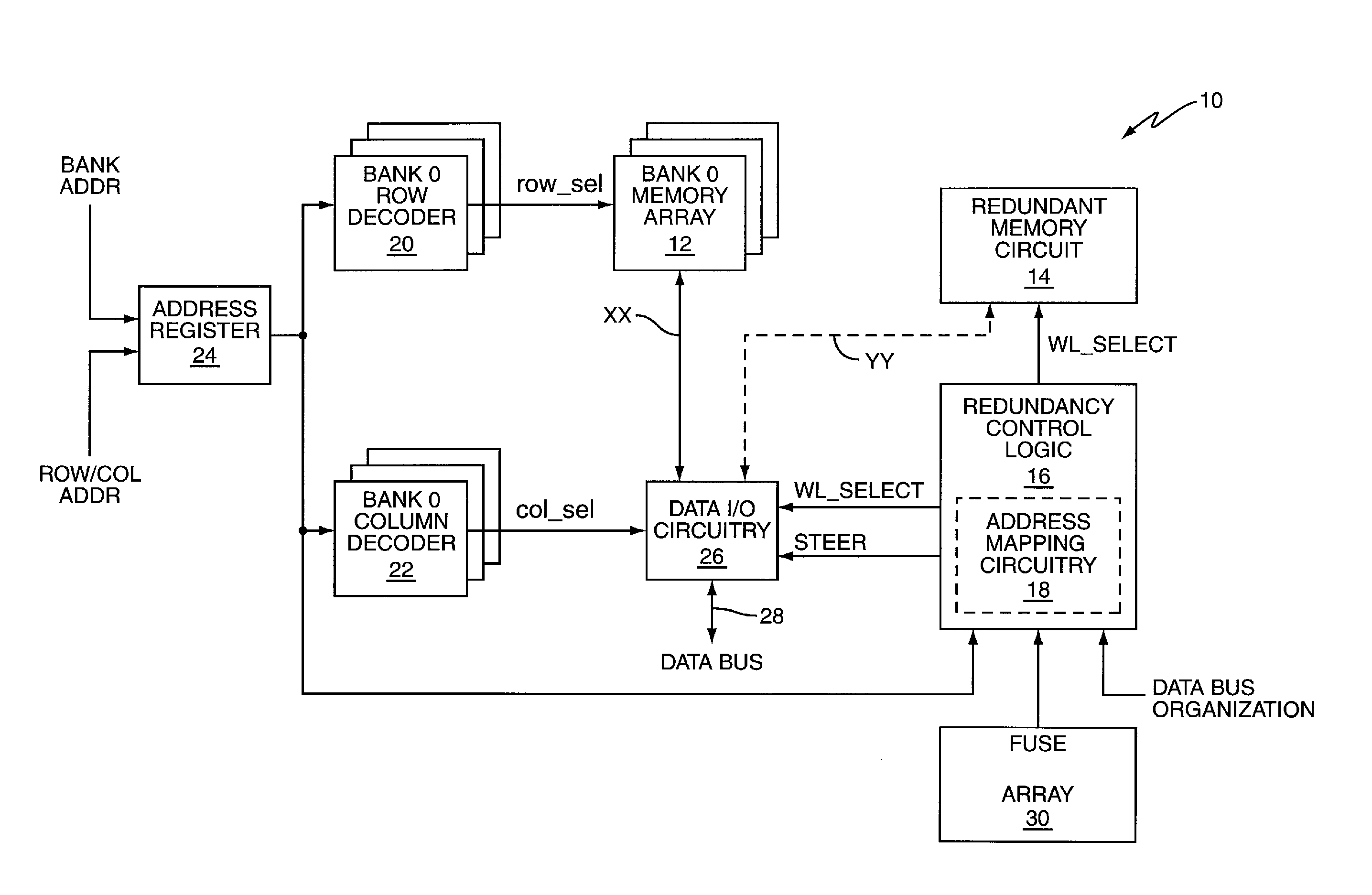

Memory Redundancy to Replace Addresses with Multiple Errors

A method and apparatus are provided for error correction of a memory by using a first memory (18), second memory (14), and redundant memory (19) to perform error correction code (ECC) processing on data retrieved from the first memory (18) by using the redundant memory (19) to replace entries in the second memory (14) having repeat addresses, thereby freeing entries in the second memory (14) for use in detecting and managing errors identified by the ECC processing.

Owner:NXP USA INC

Memory redundancy to replace addresses with multiple errors

A method and apparatus are provided for error correction of a memory by using a first memory (18), second memory (14), and redundant memory (19) to perform error correction code (ECC) processing on data retrieved from the first memory (18) by using the redundant memory (19) to replace entries in the second memory (14) having repeat addresses, thereby freeing entries in the second memory (14) for use in detecting and managing errors identified by the ECC processing.

Owner:NXP USA INC

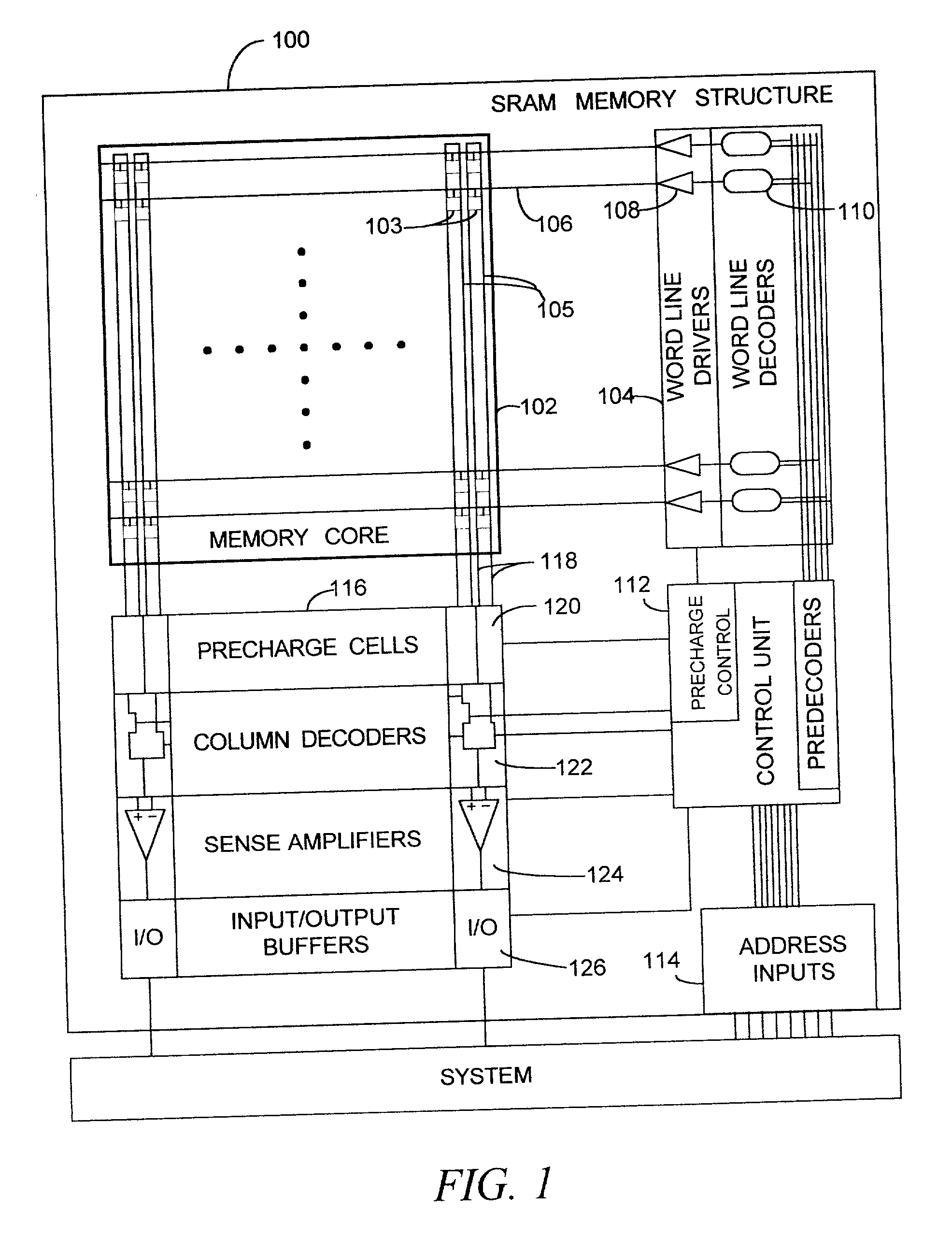

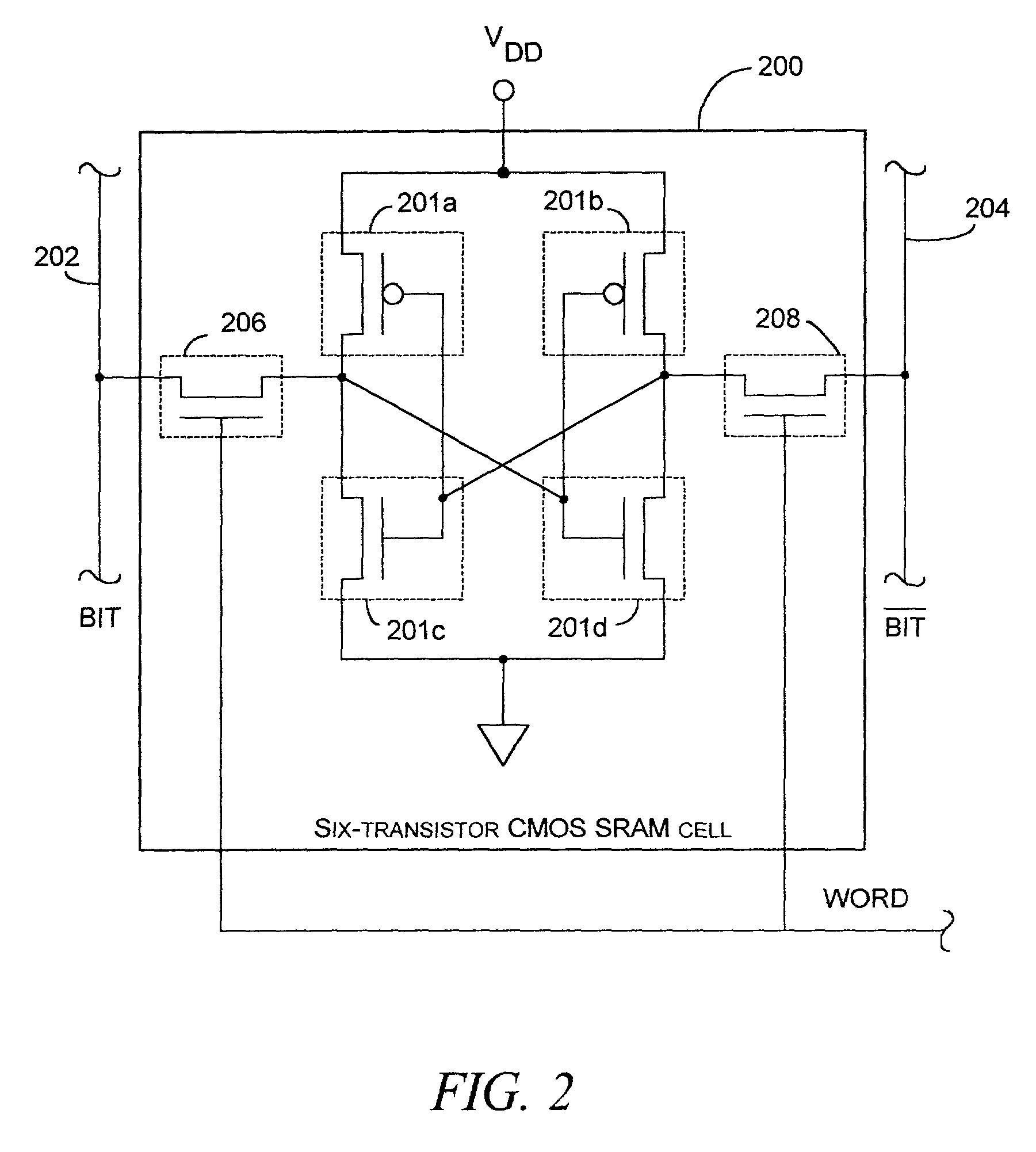

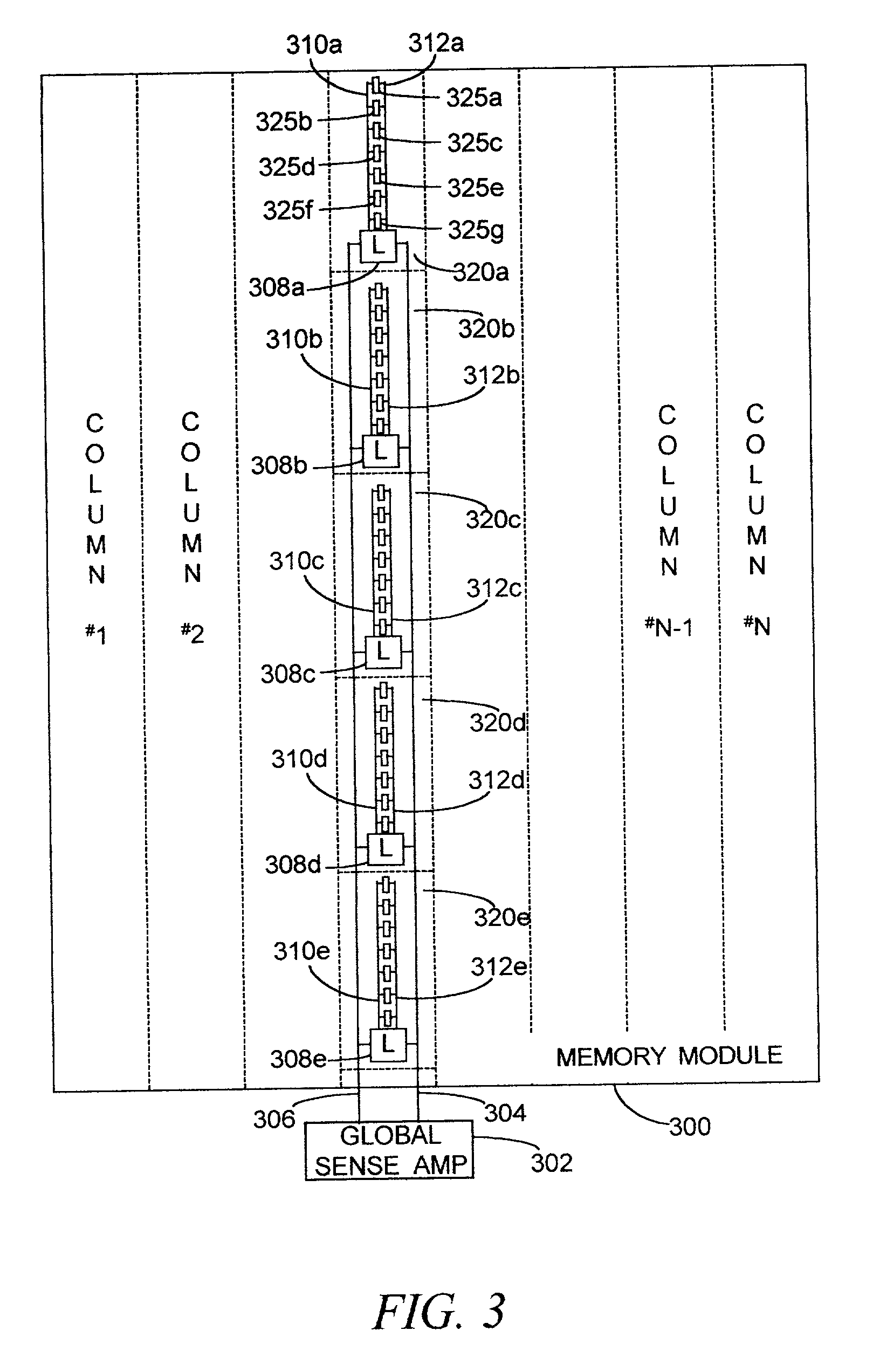

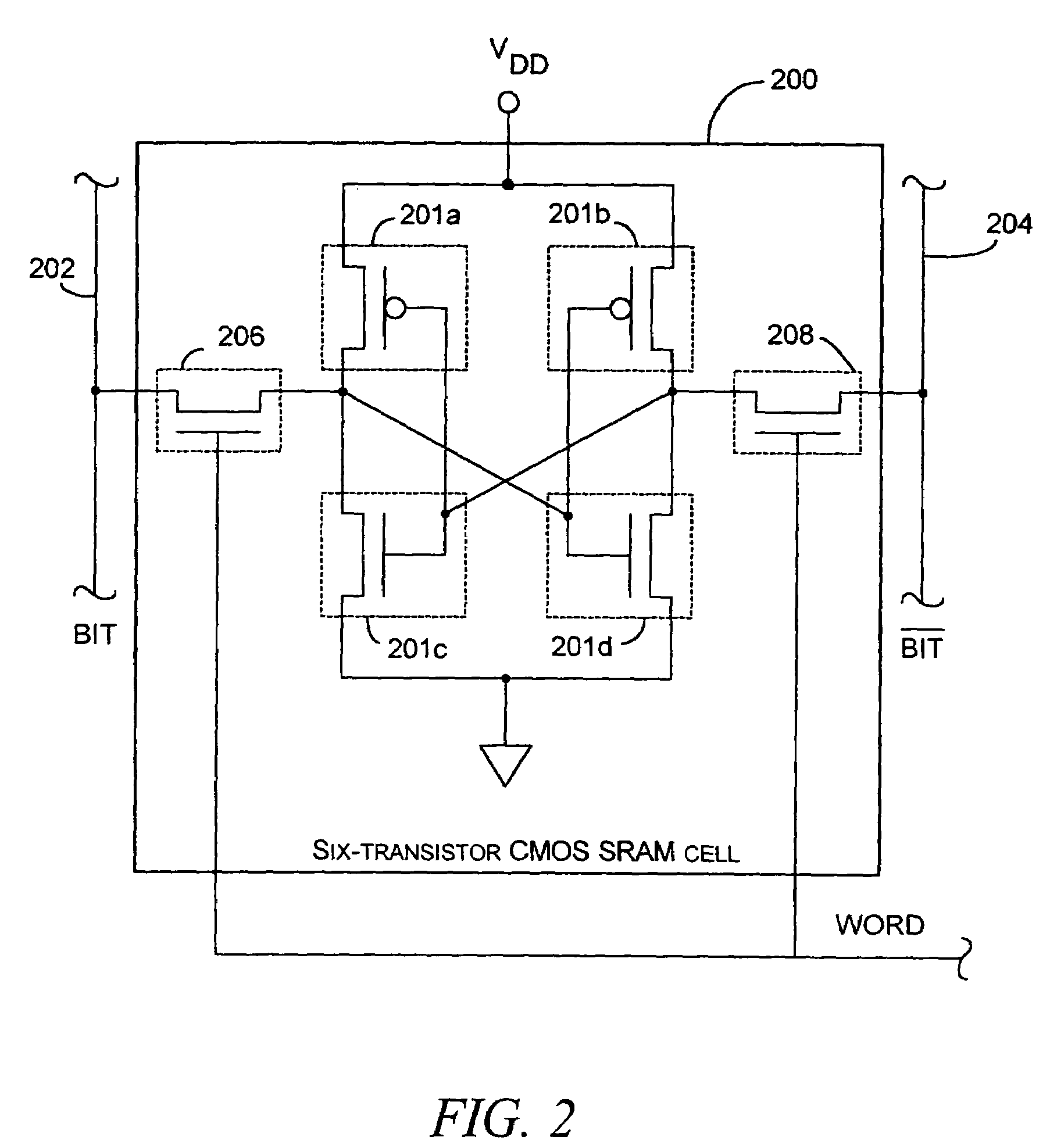

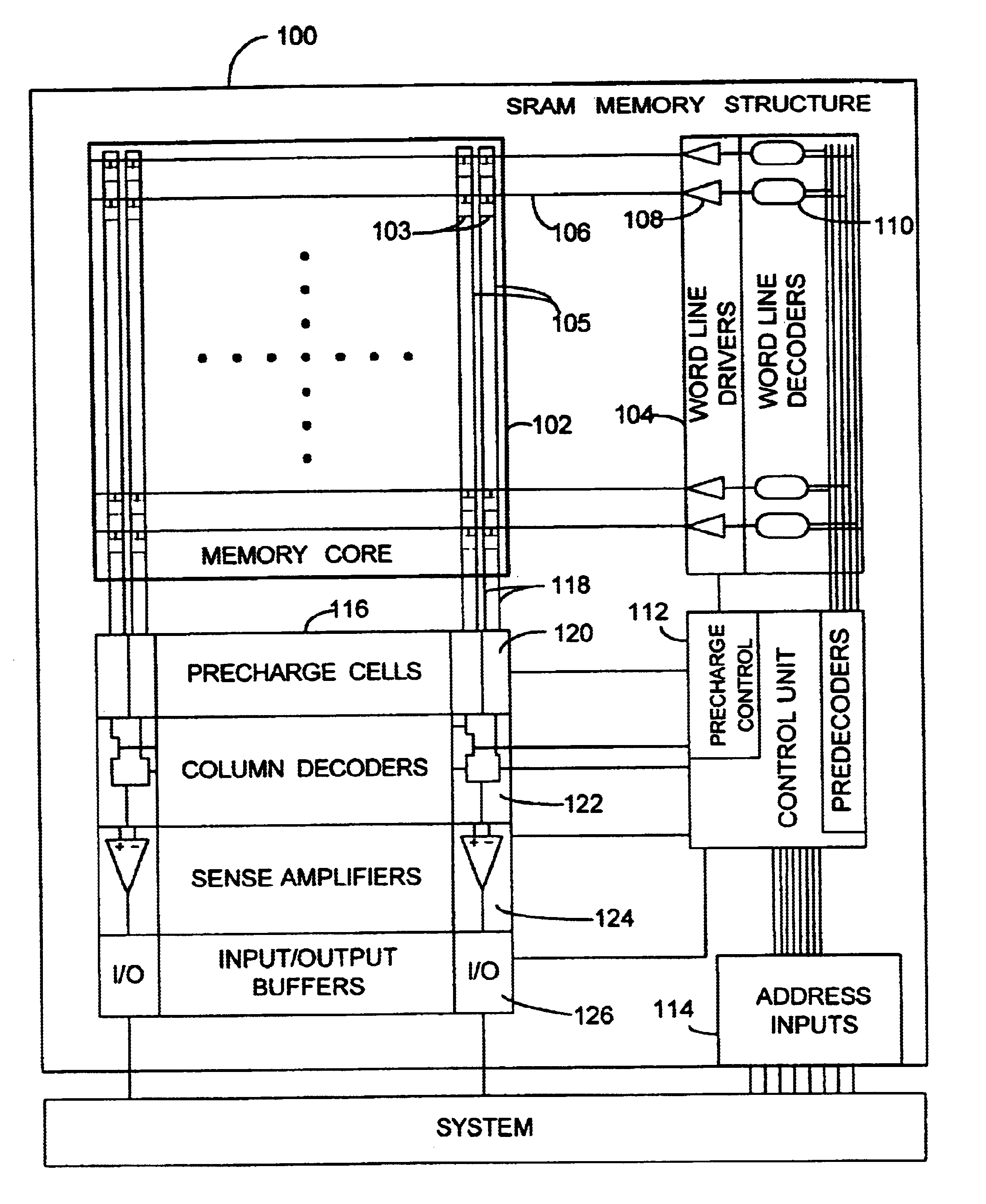

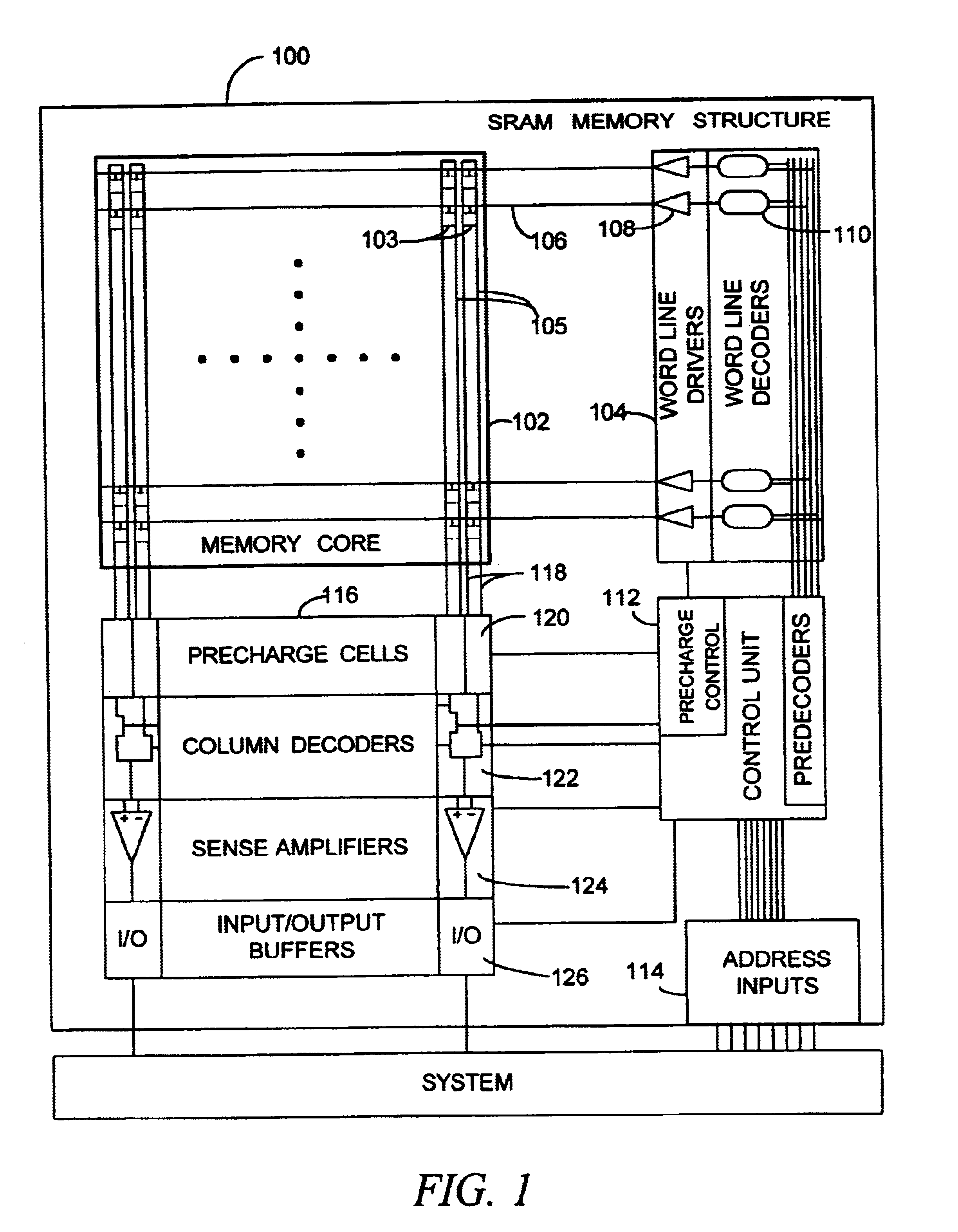

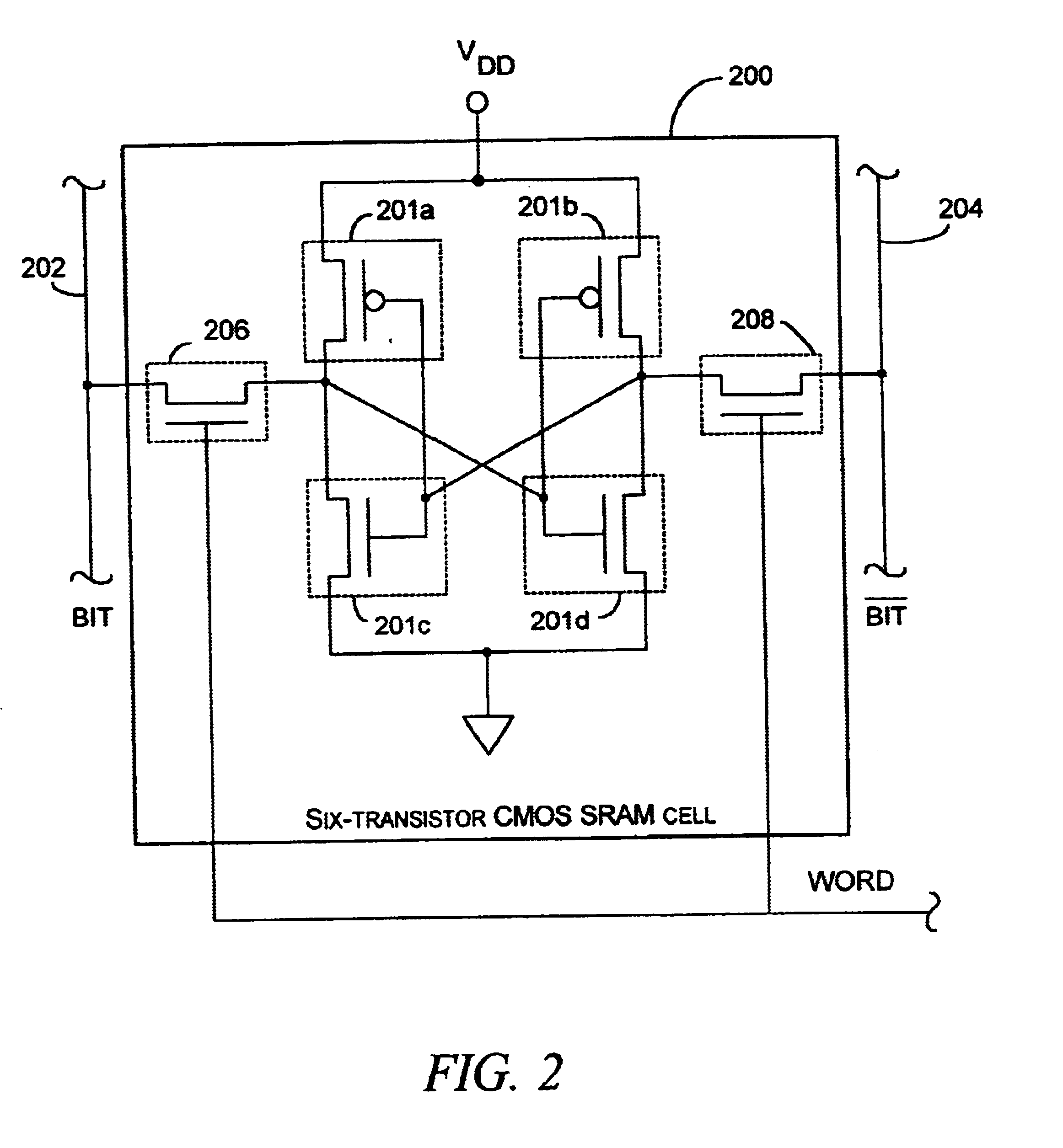

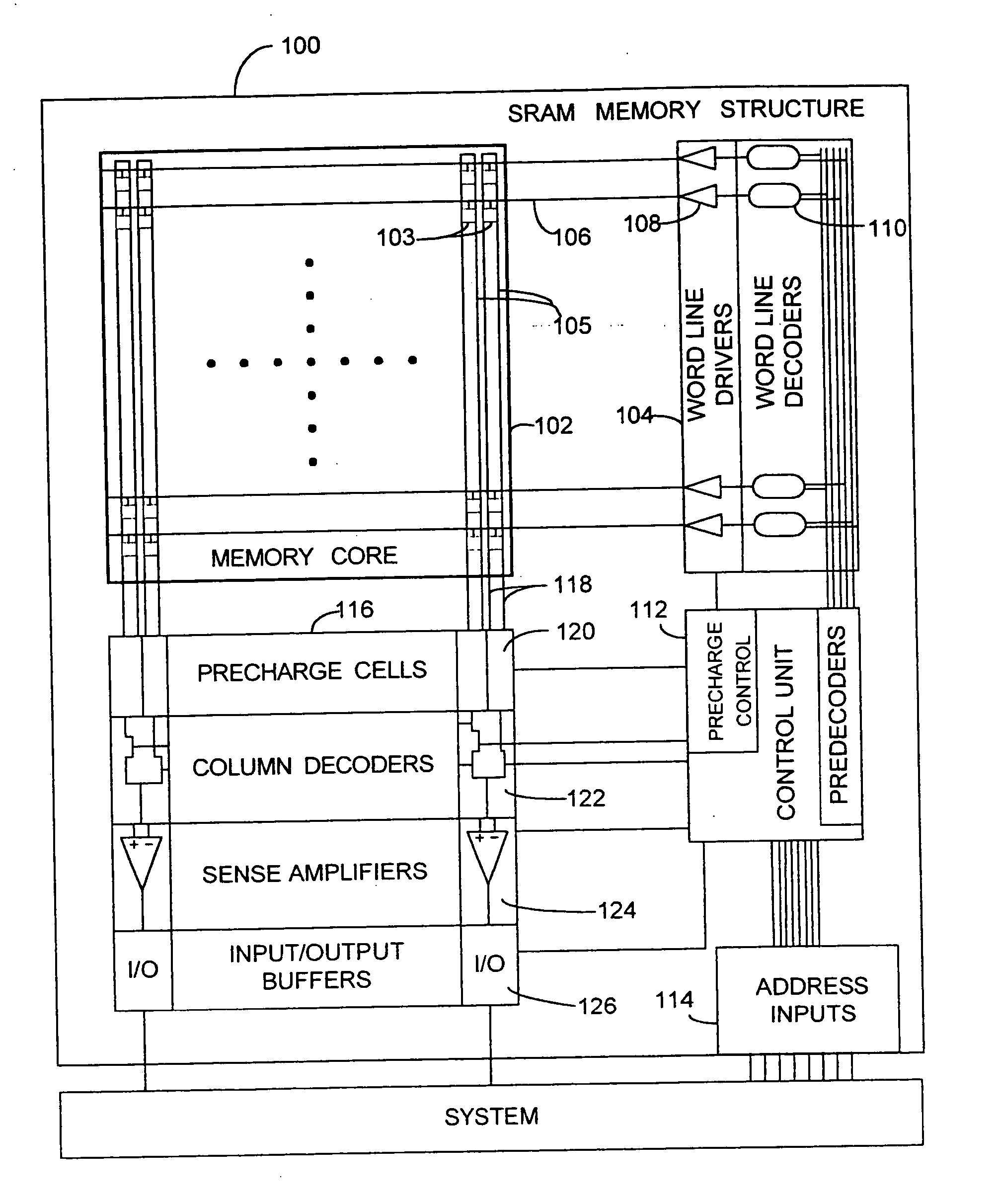

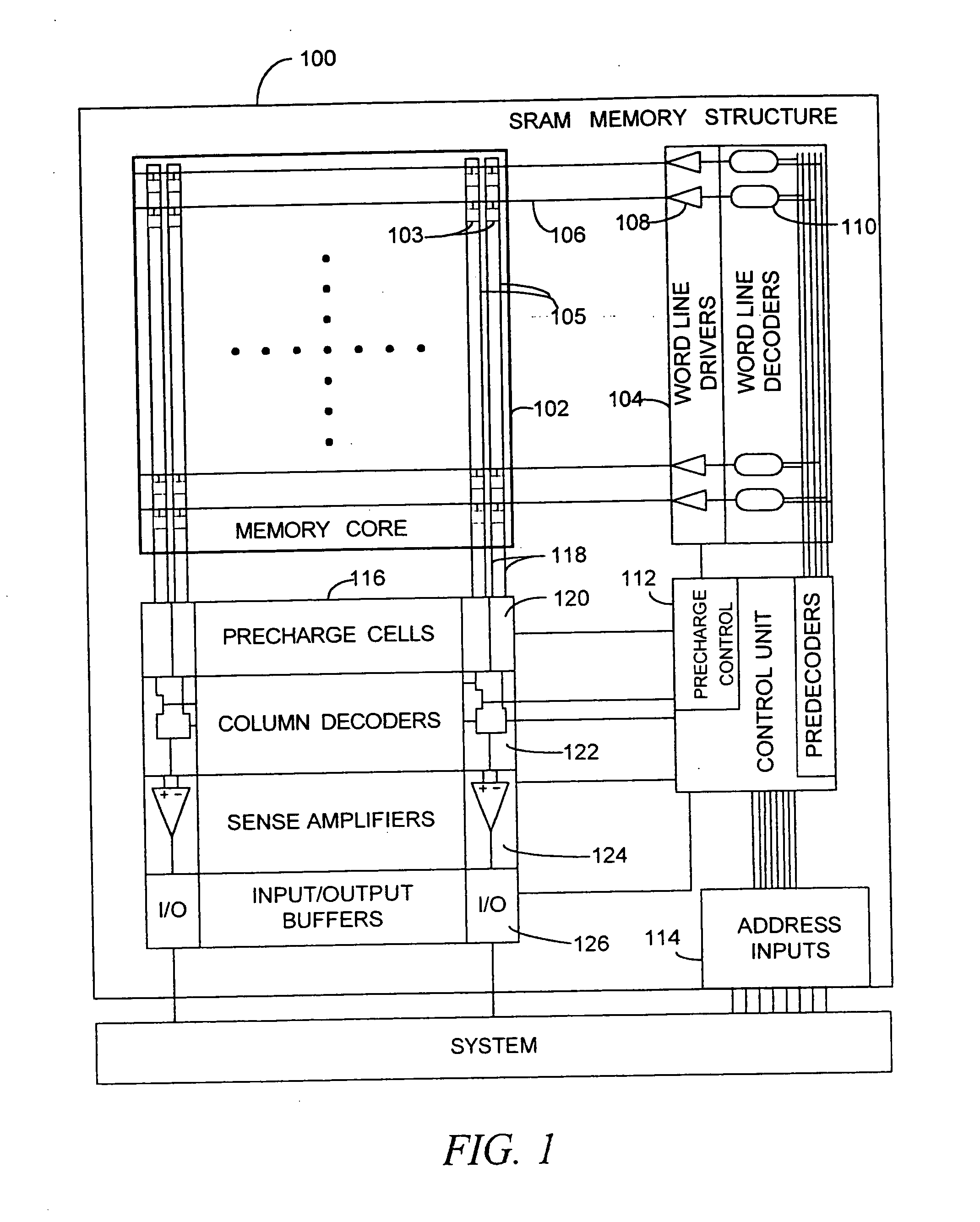

Memory architecture with single-port cell and dual-port (read and write) functionality

In a memory module having a designated group of memory cells assigned to represent a logical portion of the memory structure, a memory redundancy circuit having a redundant group of memory cells; and a redundancy controller coupled with the designated group and the redundant group. The redundancy controller, which can include a redundancy decoder, assigns the redundant group to the logical portion of the memory structure in response to a preselected memory group condition, e.g., a "FAILED" memory group condition. The redundancy controller also can includeselectable switches, for example, fuses, which can encode the preselected memory group condition. The designated group of memory cells and the redundant group of memory cells can be a memory row, a memory column, a preselected portion of a memory module, a selectable portion of a memory module, a memory module, or a combination thereof.

Owner:AVAGO TECH INT SALES PTE LTD

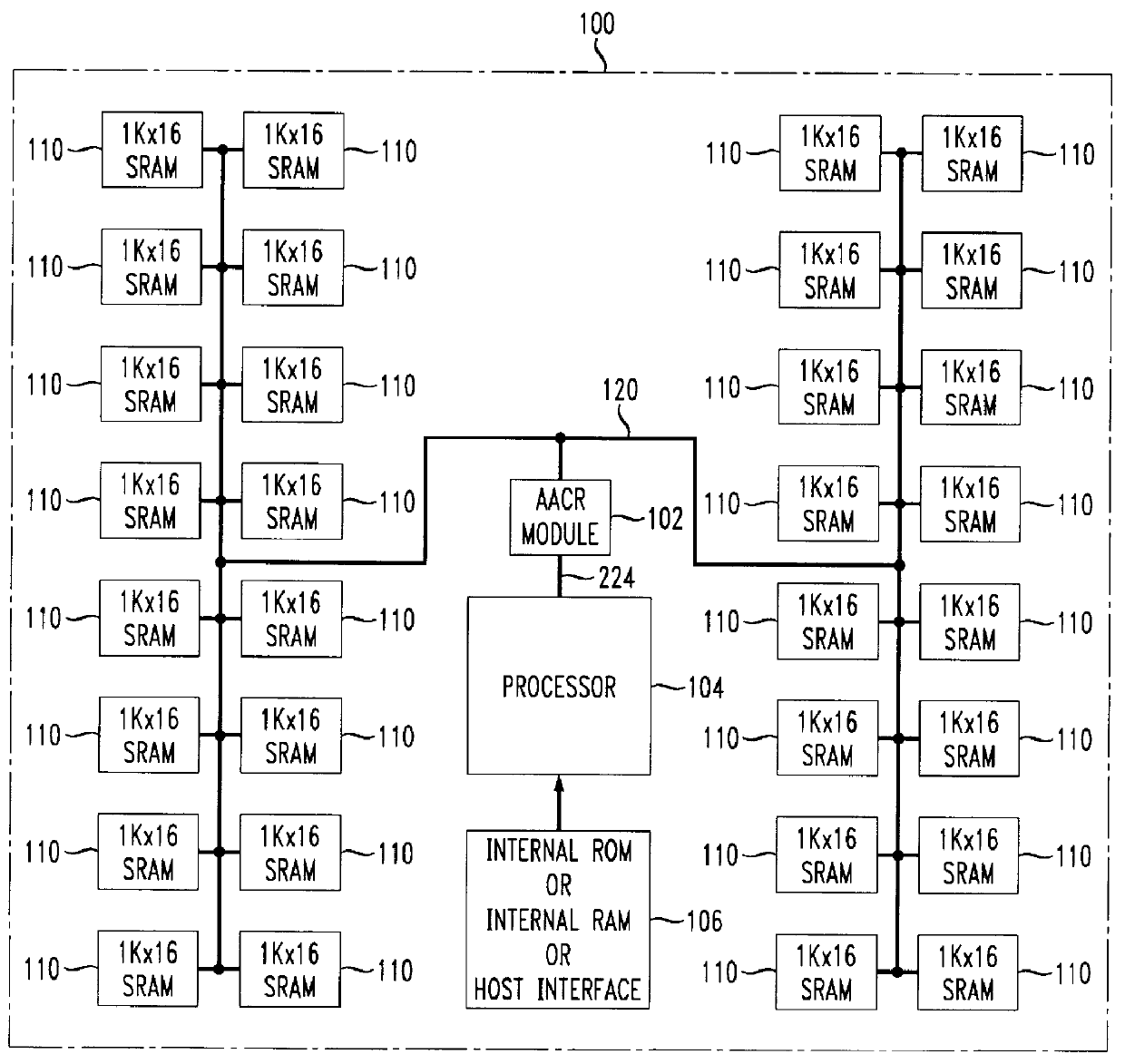

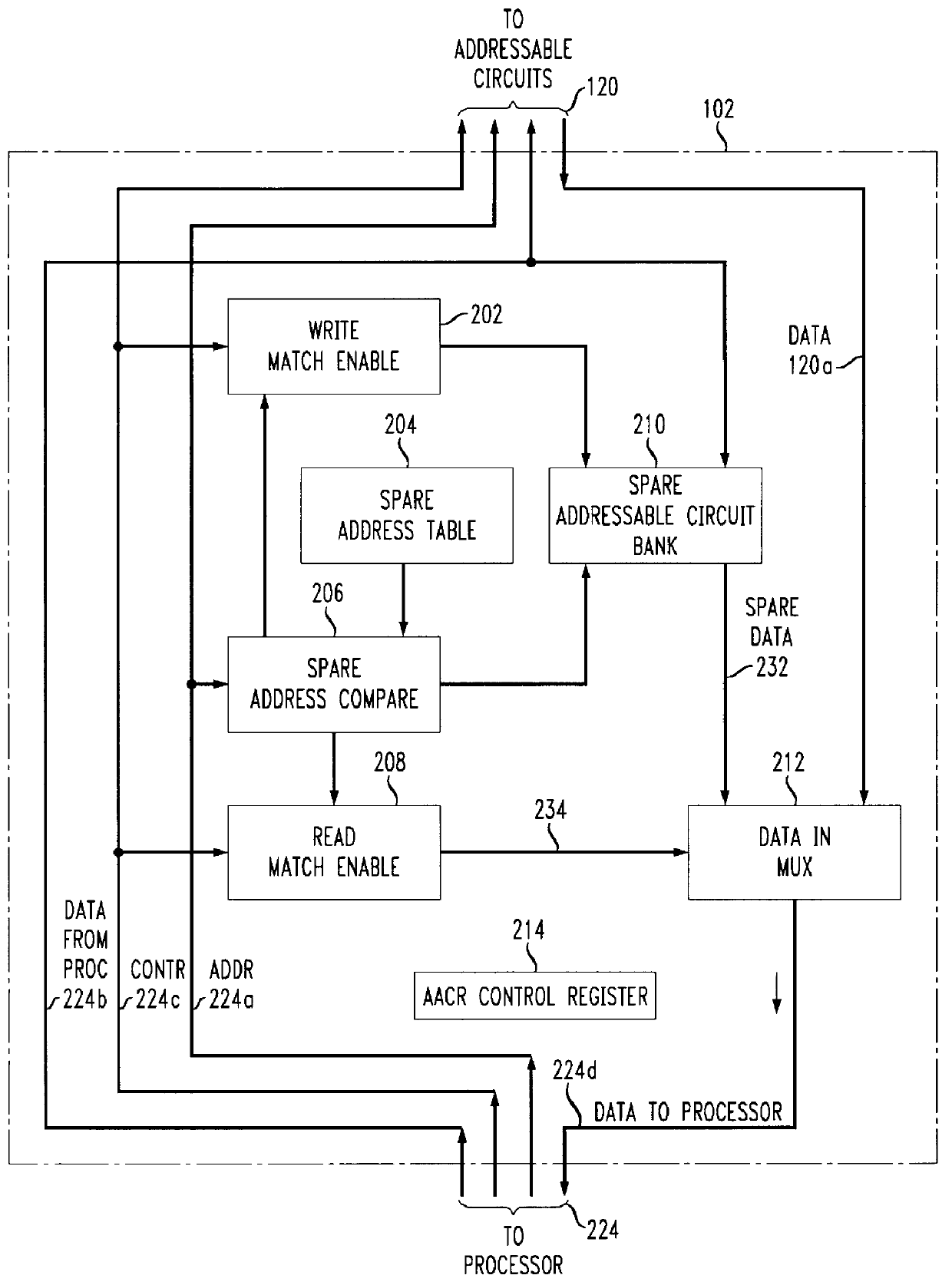

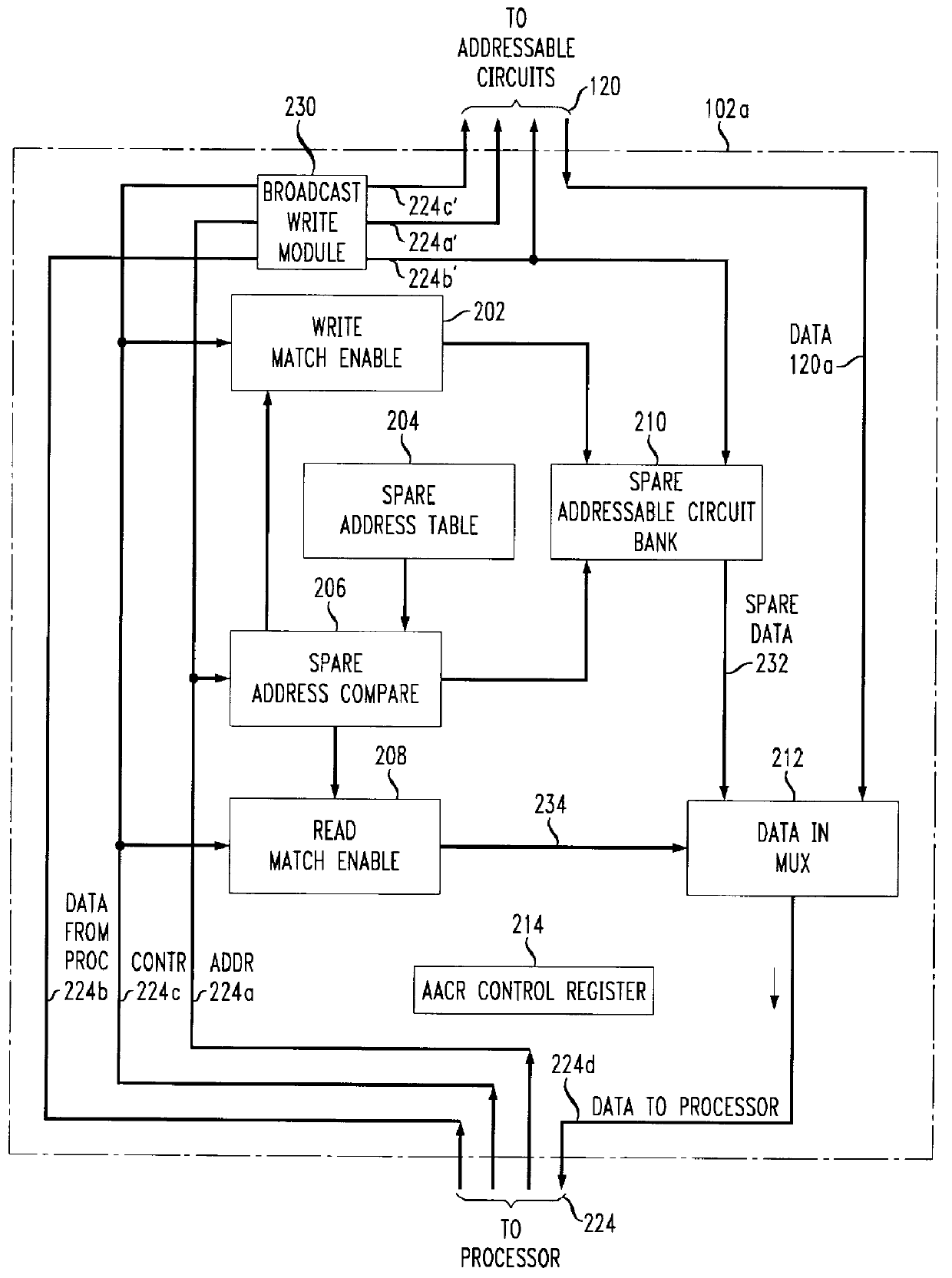

Adaptive addressable circuit redundancy method and apparatus

An adaptive addressable circuit redundancy method and apparatus, e.g., an adaptive memory redundancy method and apparatus, utilizes an on-chip processor to test, analyze and reassign spare addressable circuits to replace defective or intermittent addressable circuits. The present invention is applicable both in a manufacturing environment and / or in a field environment wherein the integrated circuit is operational. An adaptive addressable circuit redundancy module intercepts a data path between the on-chip processor and the addressable circuits to reassign defective addresses as necessary to utilize a spare addressable circuit bank. In another embodiment of the present invention, a broadcast write module cuts memory test time almost in half by writing a same data pattern to a significant portion or all of the addressable circuits, e.g., memory, substantially simultaneously.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE +1

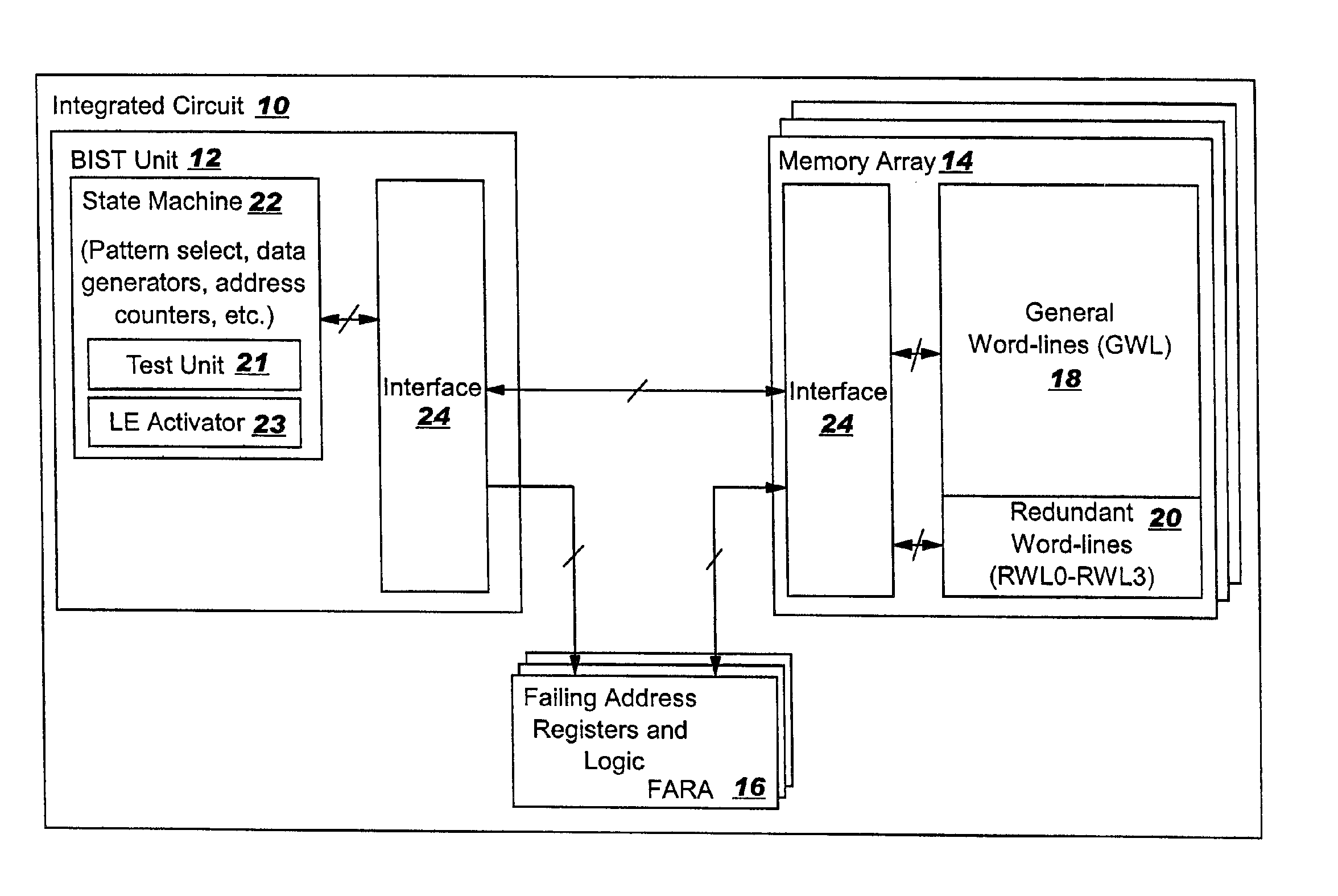

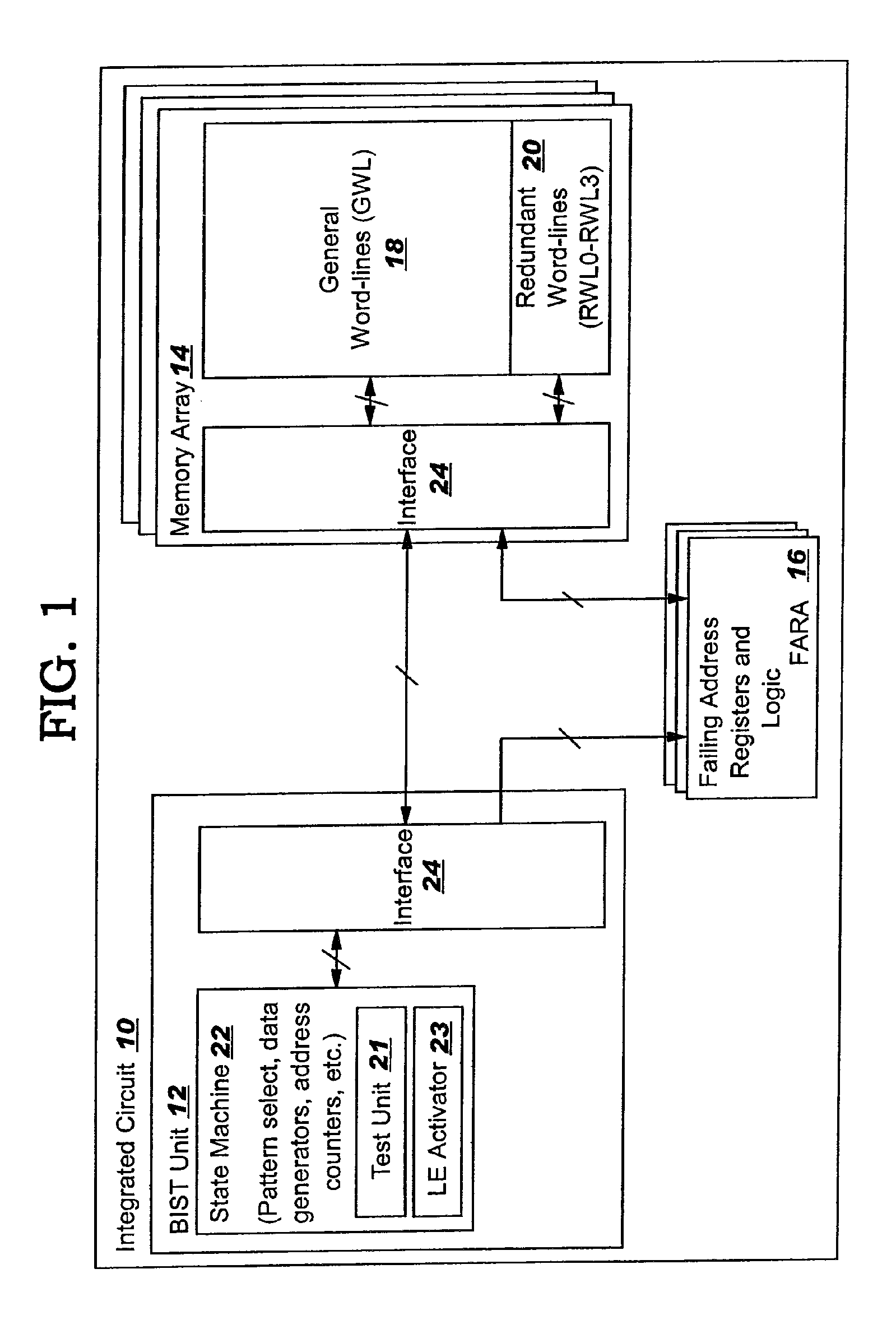

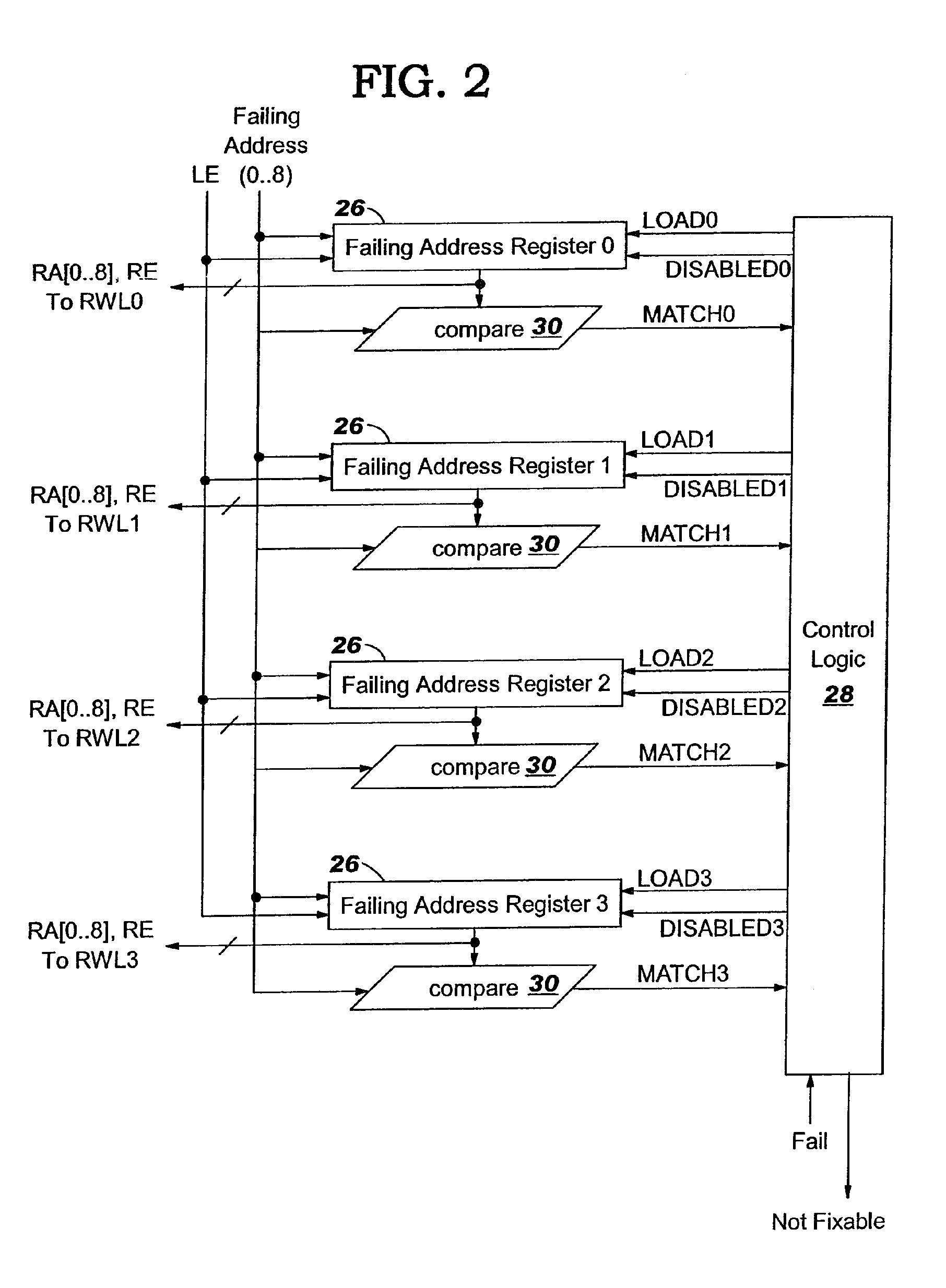

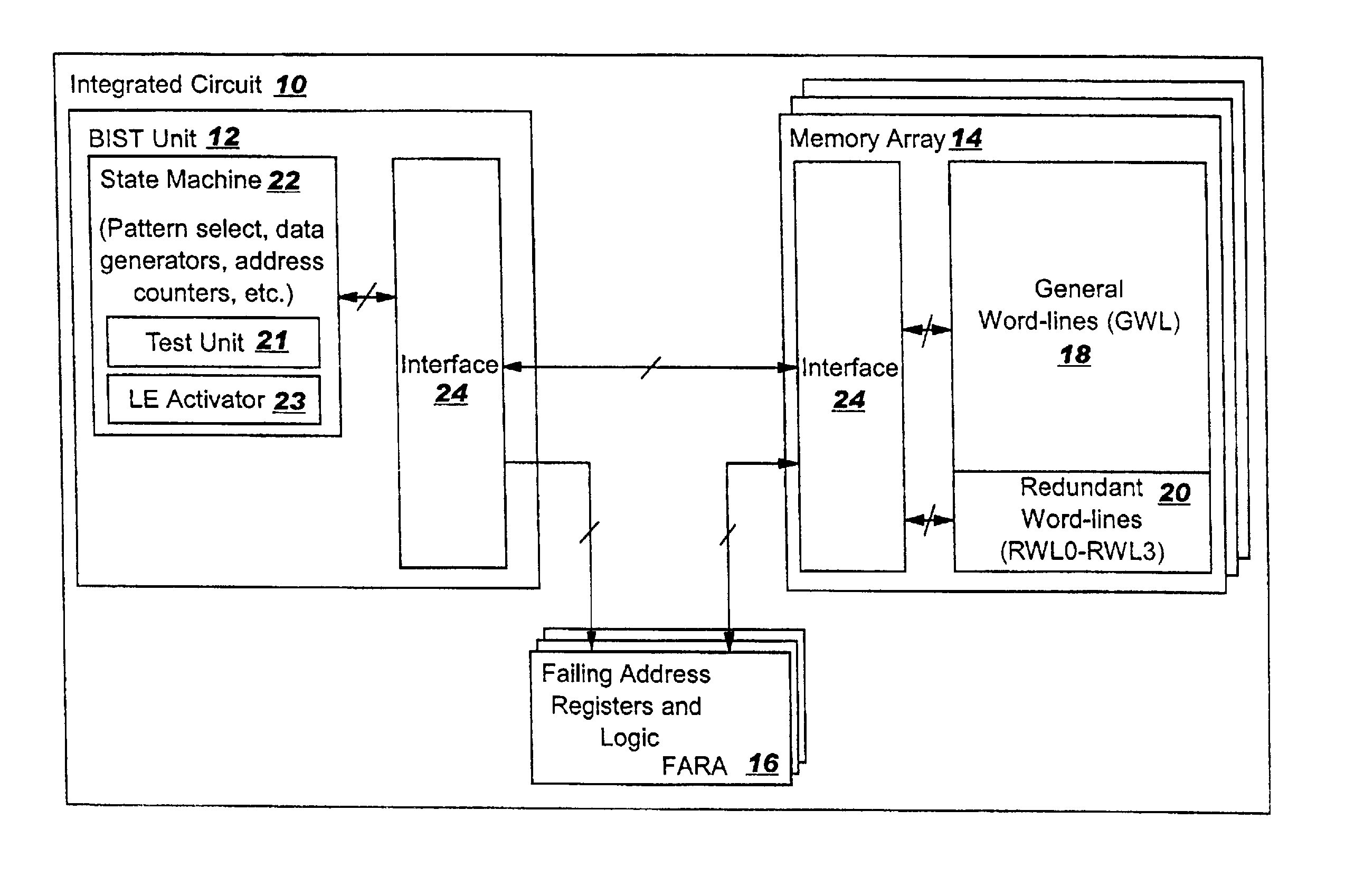

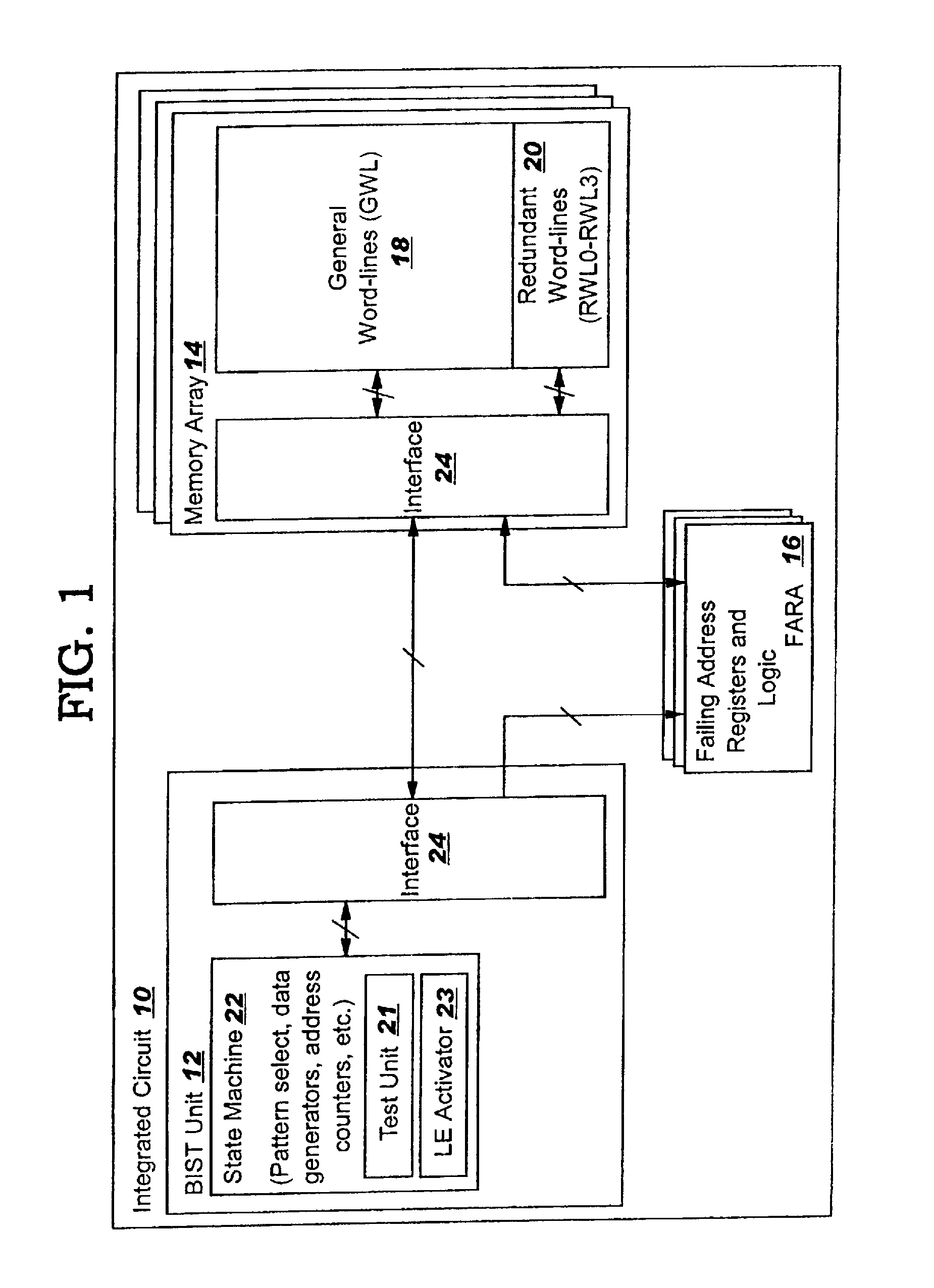

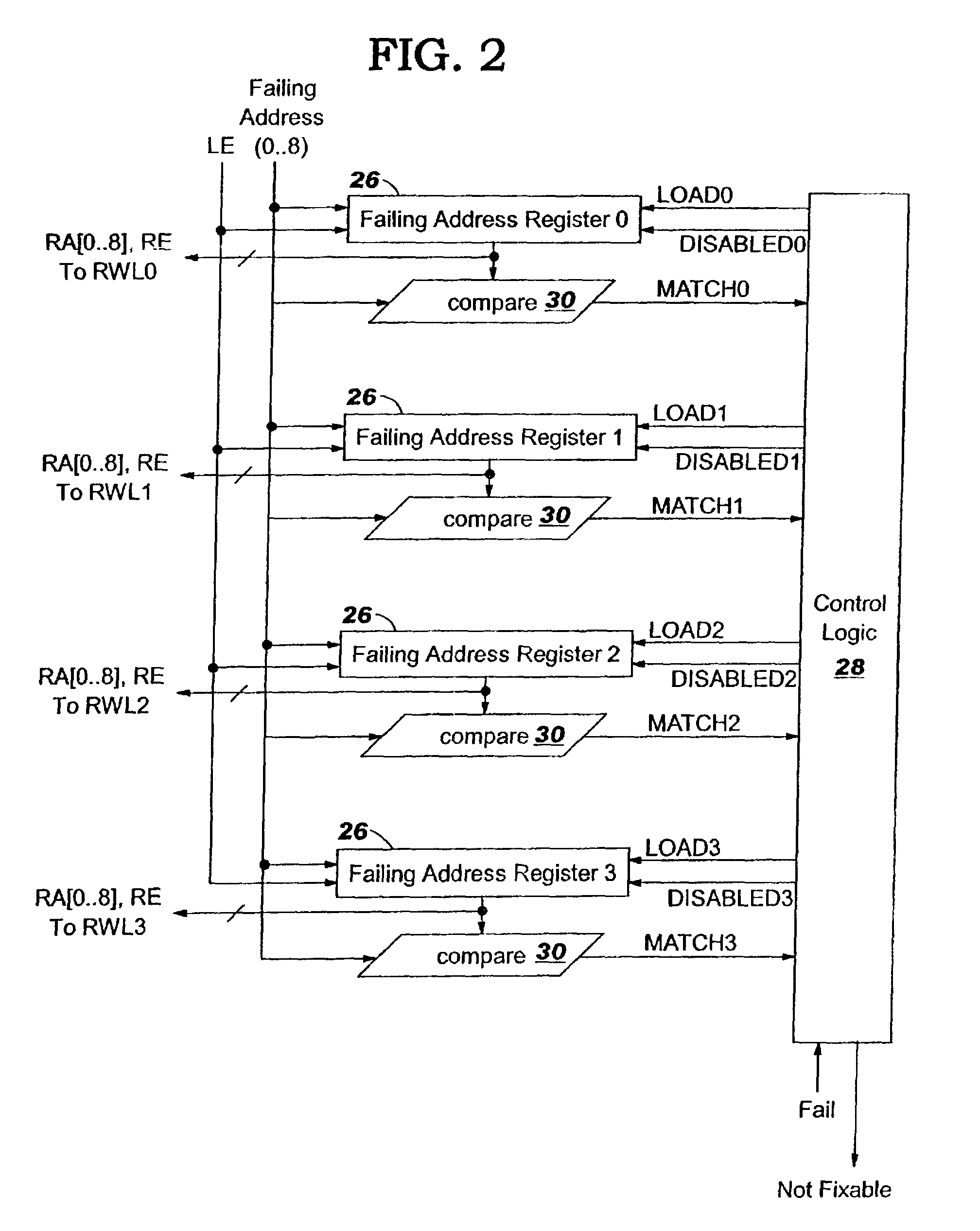

Enabling memory redundancy during testing

InactiveUS20050270866A1Enabling redundantAvoid testingDigital storageComputer scienceMemory redundancy

Methods and apparatuses for enabling a redundant memory element (20) during testing of a memory array (14).

Owner:MARVELL ASIA PTE LTD

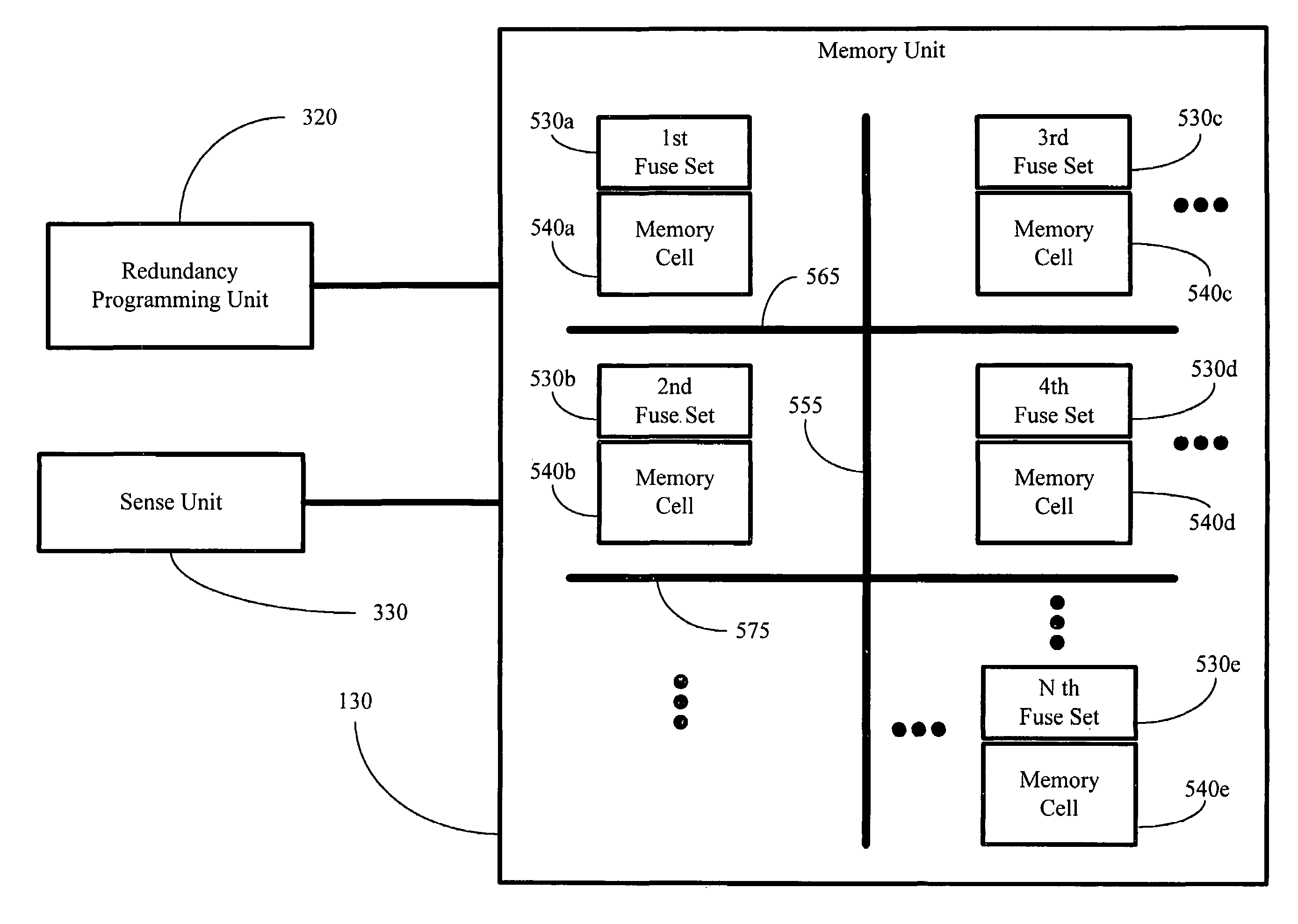

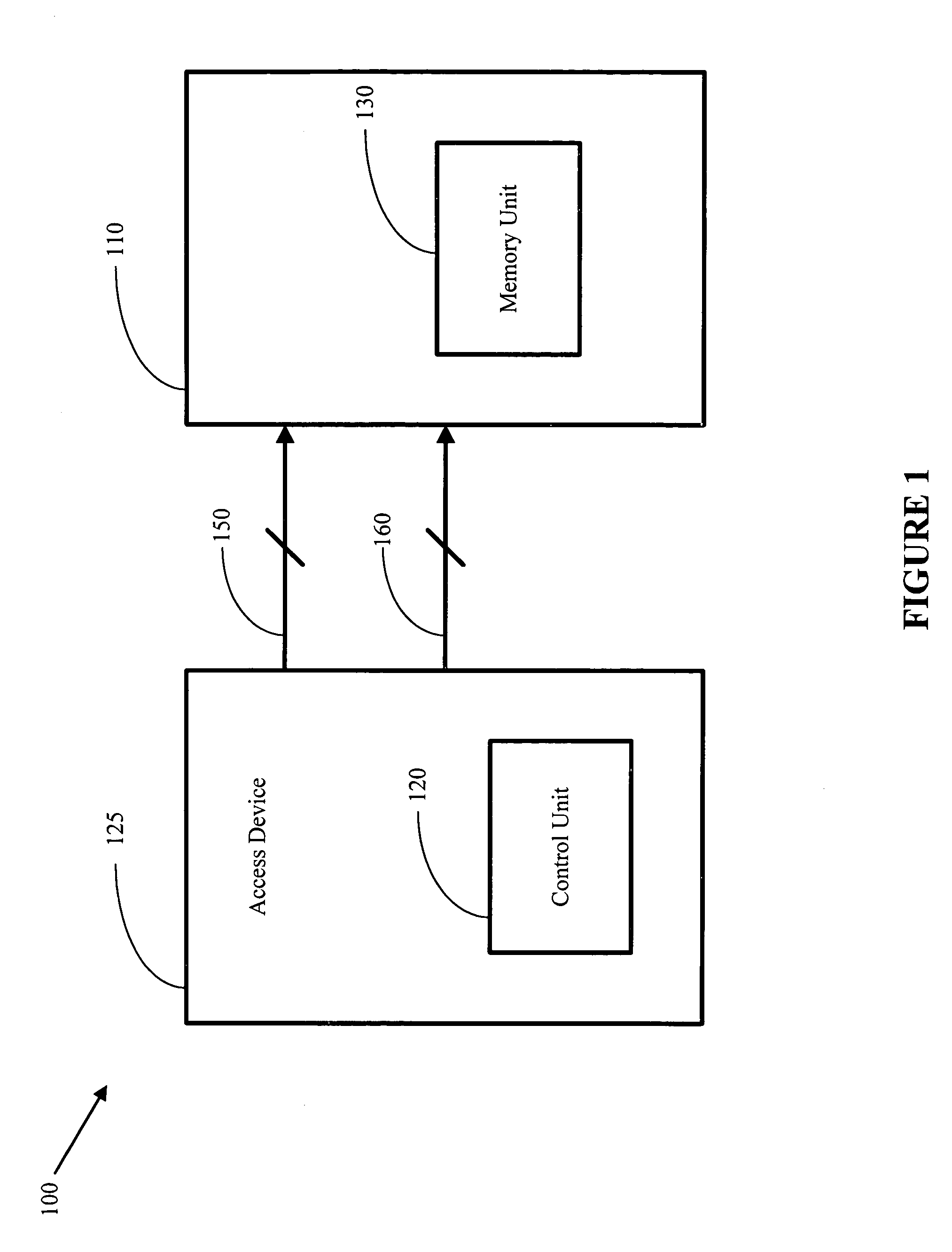

Memory redundancy programming

A method and apparatus is provided for performing a redundancy programming. The system of the present invention includes a device testing unit for performing a memory test. The system also includes a memory device operatively coupled to the device testing unit. The memory device includes an access transistor that includes a charge trapping area. A threshold voltage of the access transistor is modified upon trapping of charges in the charge trapping unit. The memory device also includes a memory element and a fuse associated with the memory element. The fuse is capable of entering an alternative state in response to modifying the threshold voltage of the access transistor. The state of the fuse may be used to program or de-program the memory element.

Owner:MICRON TECH INC

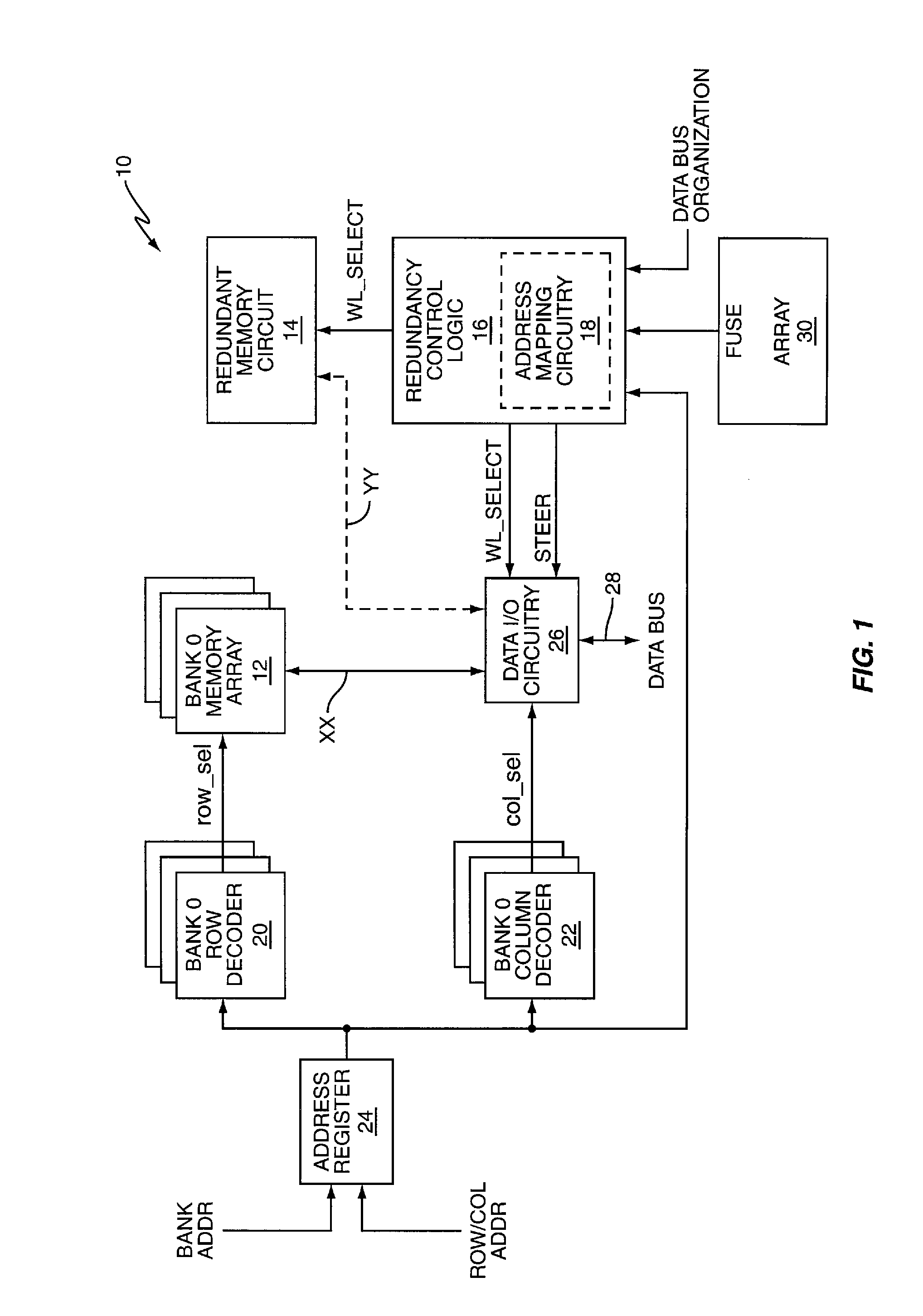

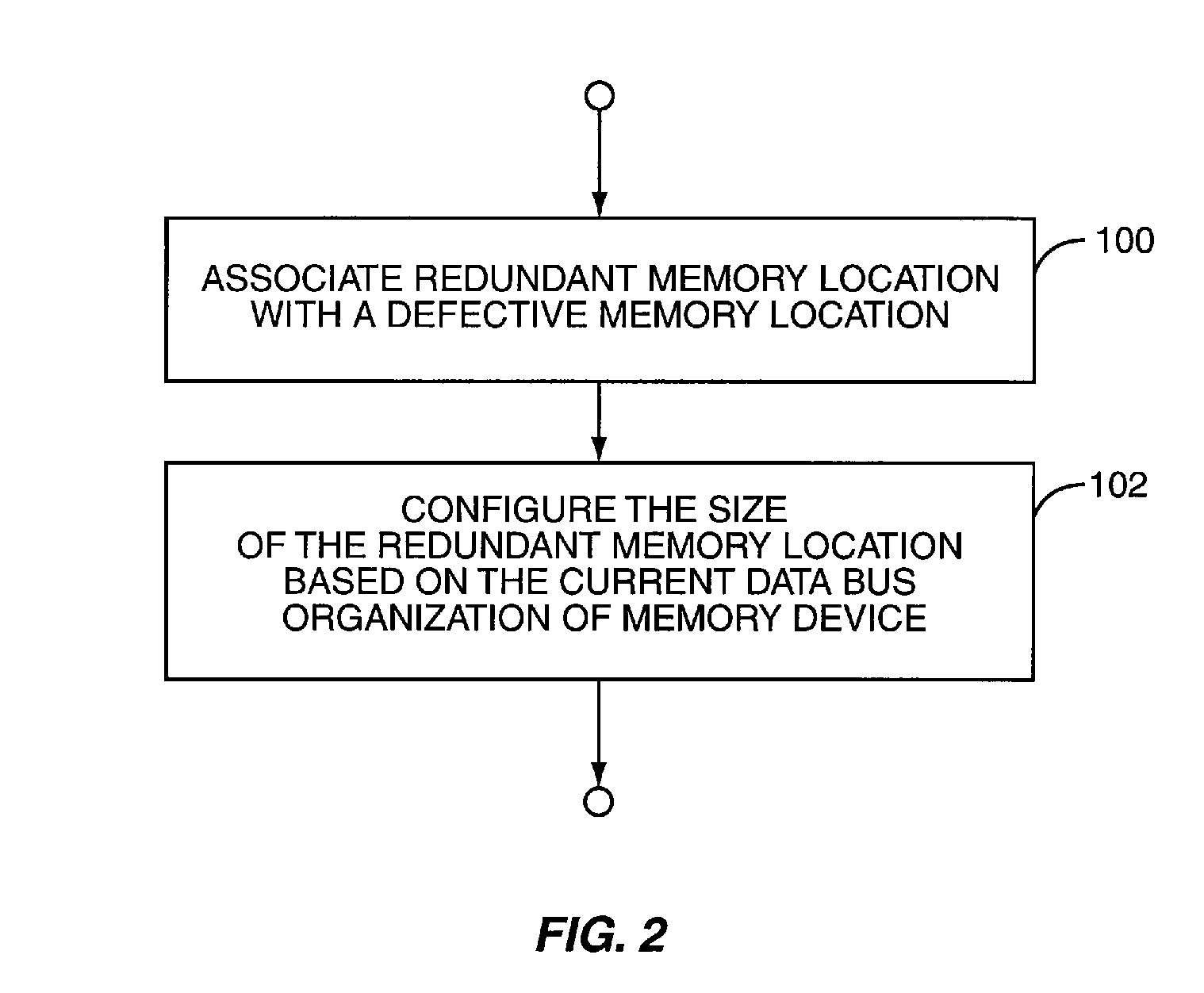

Memory redundancy circuit techniques

In a memory module having a designated group of memory cells assigned to represent a logical portion of the memory structure, a memory redundancy circuit having a redundant group of memory cells; and a redundancy controller coupled with the designated group and the redundant group. The redundancy controller, which can include a redundancy decoder, assigns the redundant group to the logical portion of the memory structure in response to a preselected memory group condition, e.g., a “FAILED” memory group condition. The redundancy controller also can include selectable switches, for example, fuses, which can encode the preselected memory group condition. The designated group of memory cells and the redundant group of memory cells can be a memory row, a memory column, a preselected portion of a memory module, a selectable portion of a memory module, a memory module, or a combination thereof.

Owner:AVAGO TECH INT SALES PTE LTD

Memory redundancy implementation

Owner:AVAGO TECH INT SALES PTE LTD

Low-cost efficient internal storage redundancy removing method and system

InactiveCN104035822AEliminate limitationsSave memoryResource allocationTransmissionOperational systemComputer science

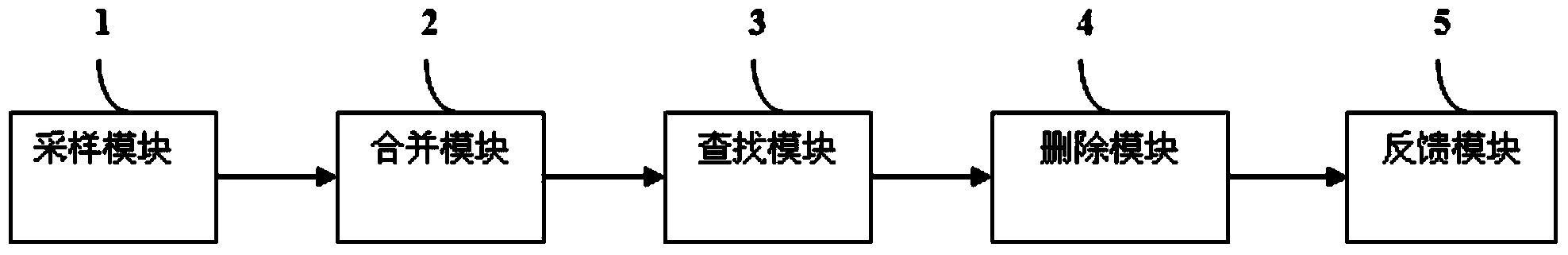

The invention discloses an internal storage space redundancy removing method and system, relates to computer internal storage managing, and belongs to the field of operation systems. The method comprises the steps that a webpage in internal storage space is sampled, wherein sampling coefficients are set, the sampling range is determined according to the sampling coefficients, and the sampled webpage is acquired according to the sampling range; the internal storage space is searched for a webpage with the webpage content same as that of the sampled webpage, the webpage serves as a redundancy webpage and is combined with the sampled webpage, and the information of the redundancy webpage is recorded; the content in the redundancy webpage is deleted, and redundancy in the internal storage space is removed. According to the internal storage space redundancy removing method and system, a scanning area can be dynamically selected, the internal storage space redundancy removing method and system are suitable for a scene with a large number of repeating webpages and also suitable for a scene with a little internal storage redundancy, and the system cost can be reduced.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

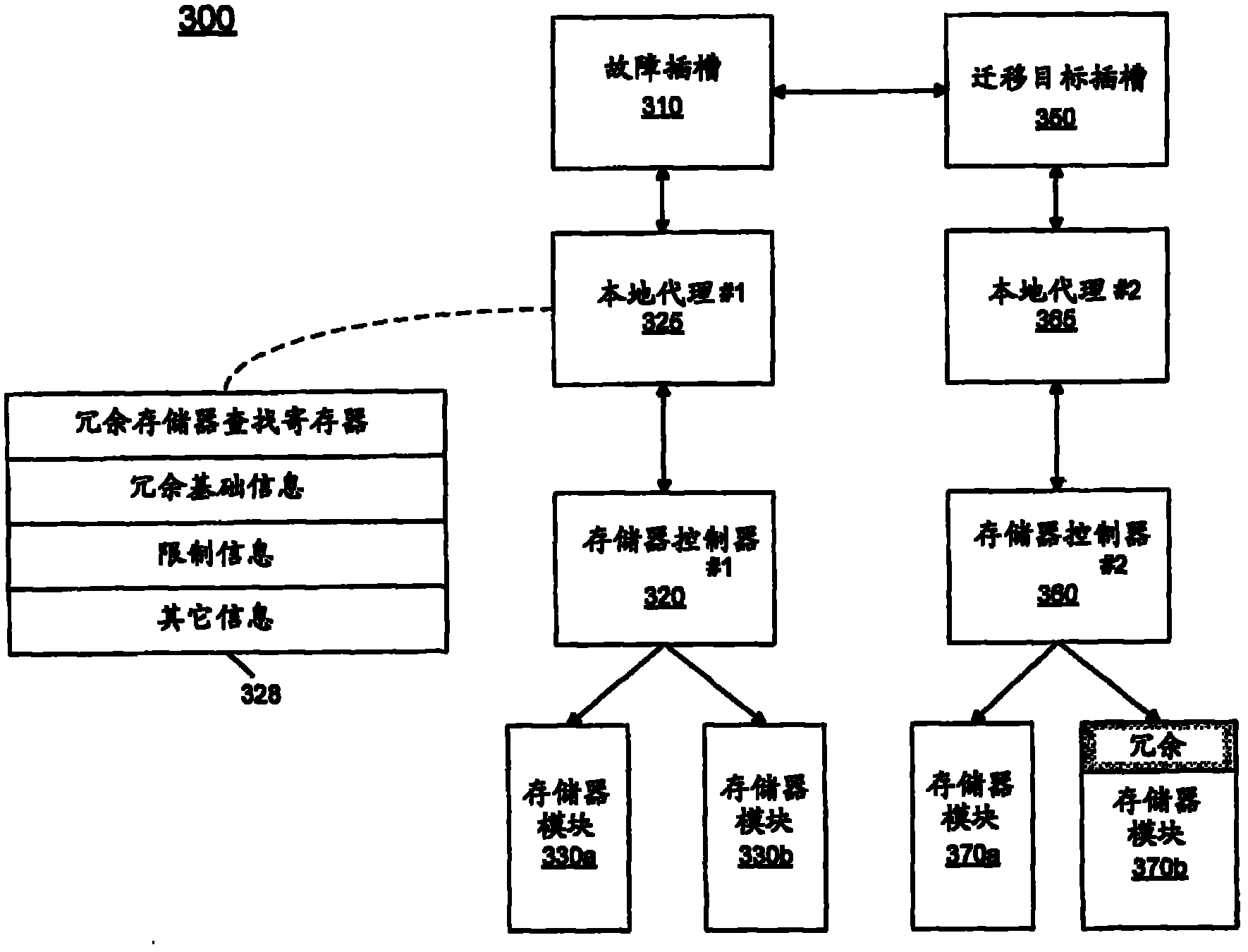

Controlling memory redundancy in a system

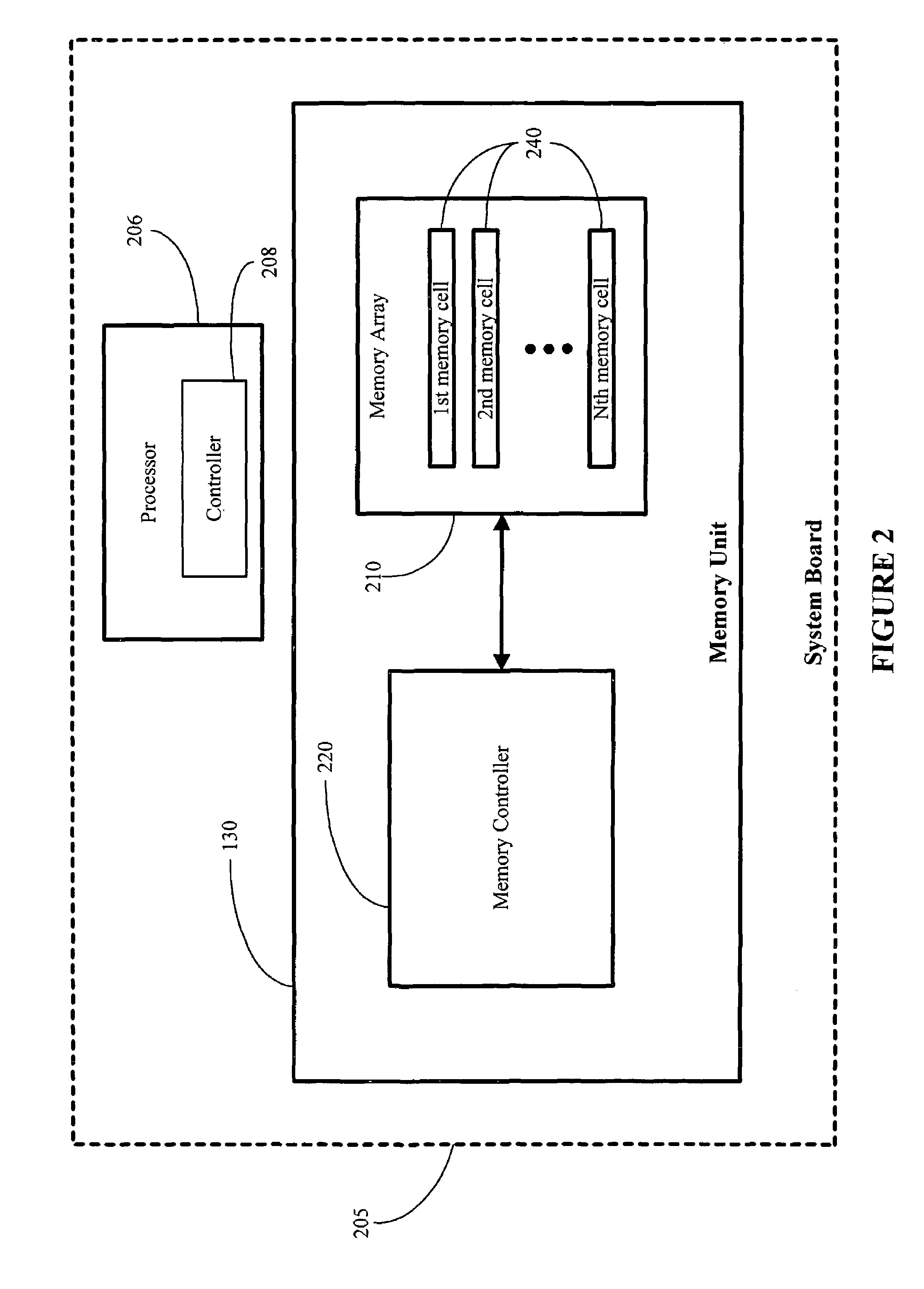

In one embodiment, the present invention provides an ability to handle an error occurring during a memory migration operation in a high availability system. In addition, a method can be used to dynamically remap a memory page stored in a non-mirrored memory region of memory to a mirrored memory region. This dynamic remapping may be responsive to a determination that the memory page has been accessed more than a threshold number of times, indicating a criticality of information on the page. Other embodiments are described and claimed.

Owner:INTEL CORP

System and method for running test and redundancy analysis in parallel

Owner:MICRON TECH INC

Memory redundancy device and method

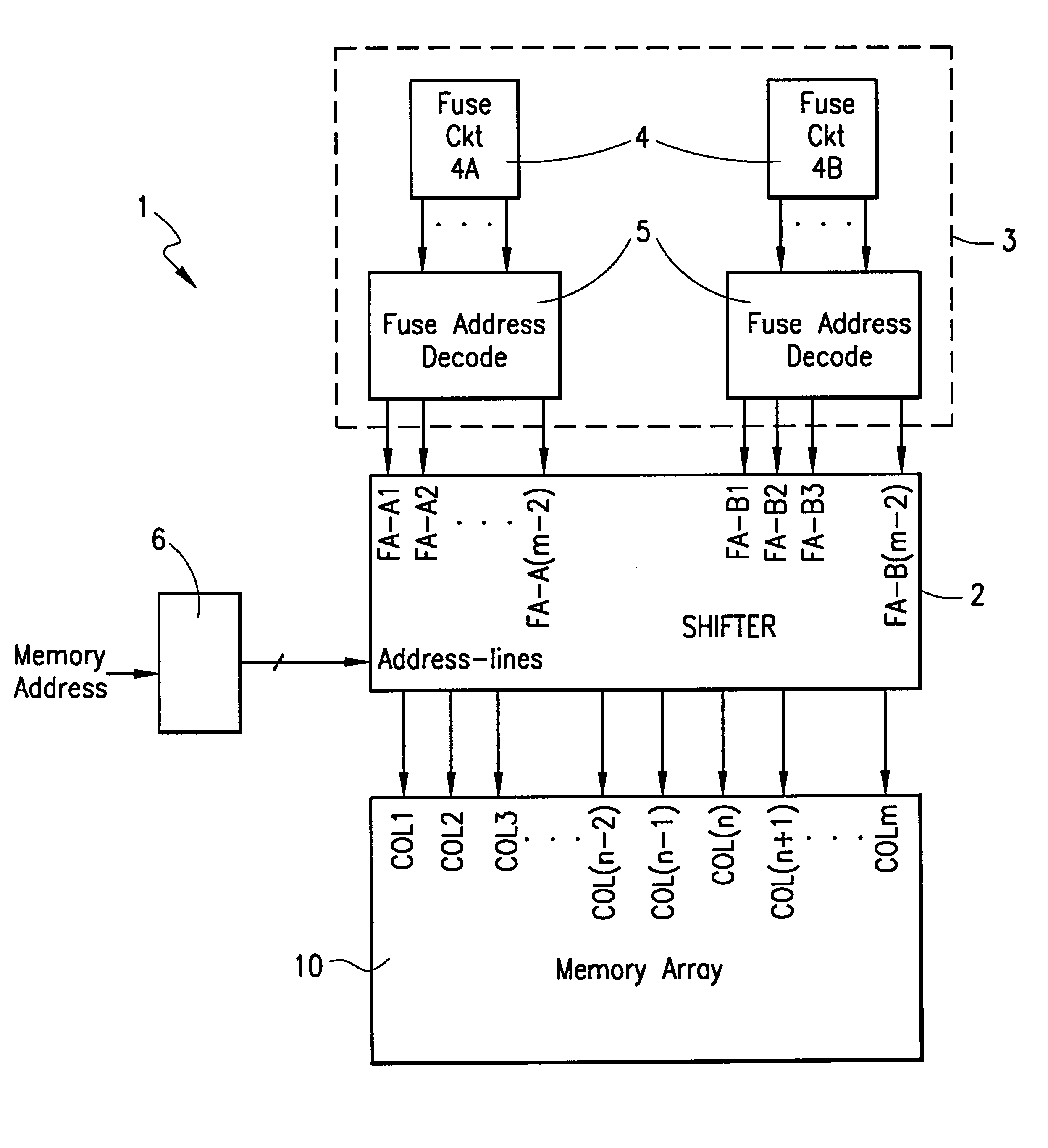

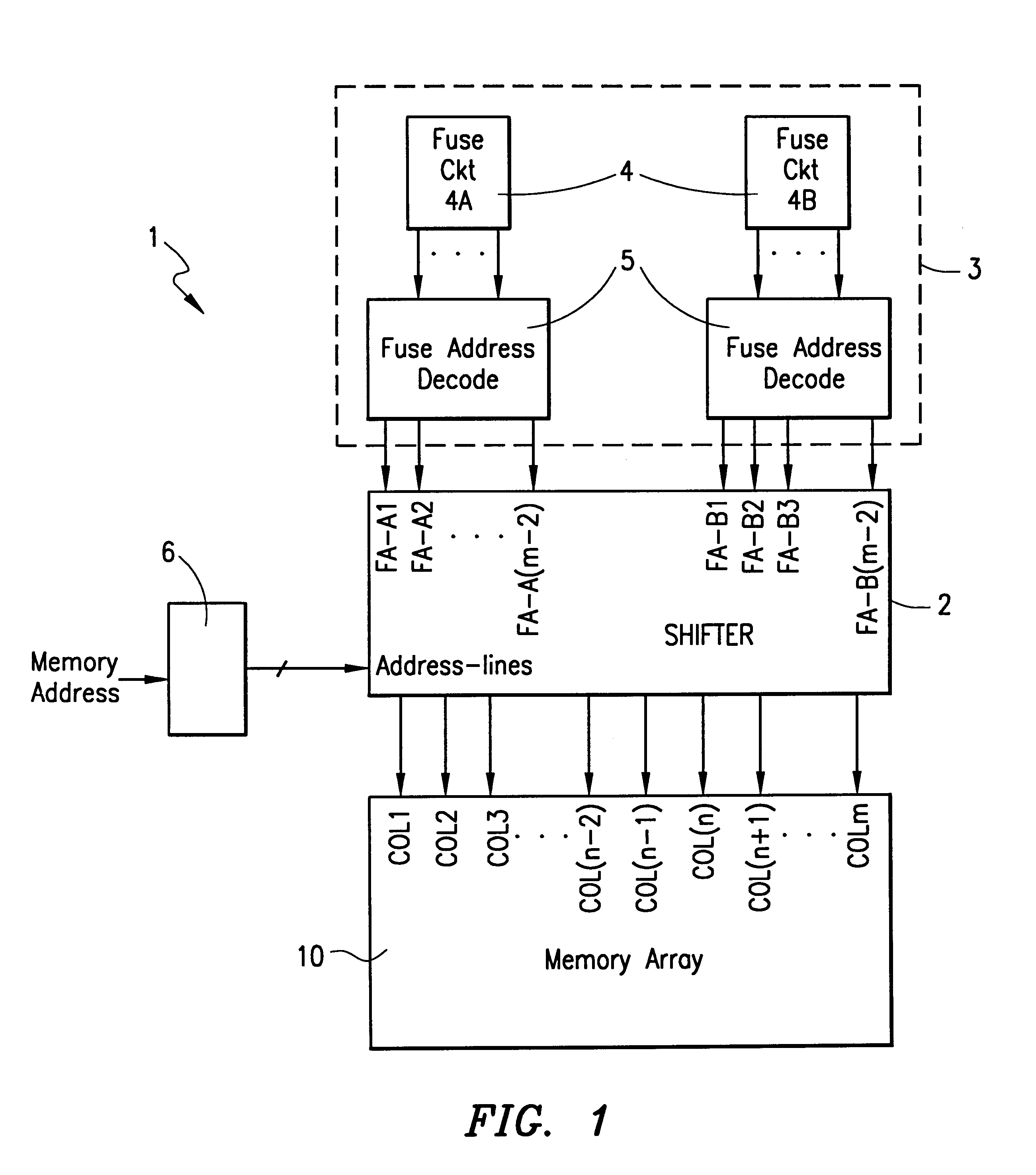

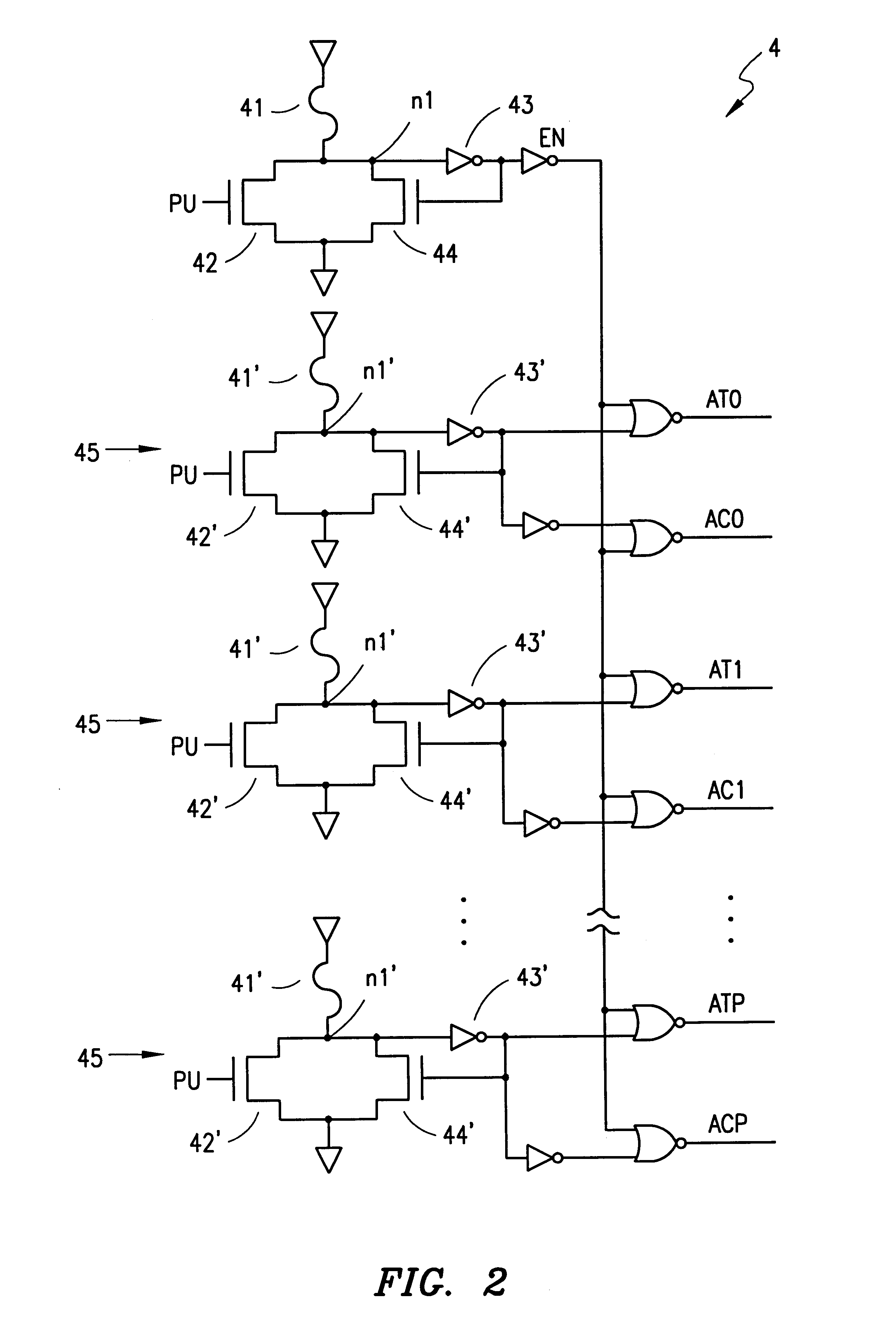

InactiveUS6243305B1Reduce yieldImprove processing yieldRead-only memoriesSemiconductor/solid-state device manufacturingProgrammable circuitsComputer science

A redundant circuit and method for a semiconductor memory device is disclosed. The redundant circuit includes a programmable circuit for selectively generating at least one first address corresponding to a defective memory row or column line, and shifter circuitry for remapping second addresses which are greater than the first address to row / column lines. For each second address which is greater than the first address, the shifter circuitry remaps the second address to a row / column line which was initially mapped to an immediately higher address relative to the second address. The programmable circuit is capable of generating a plurality of first addresses corresponding to a plurality of defective memory row or column lines.

Owner:STMICROELECTRONICS SRL

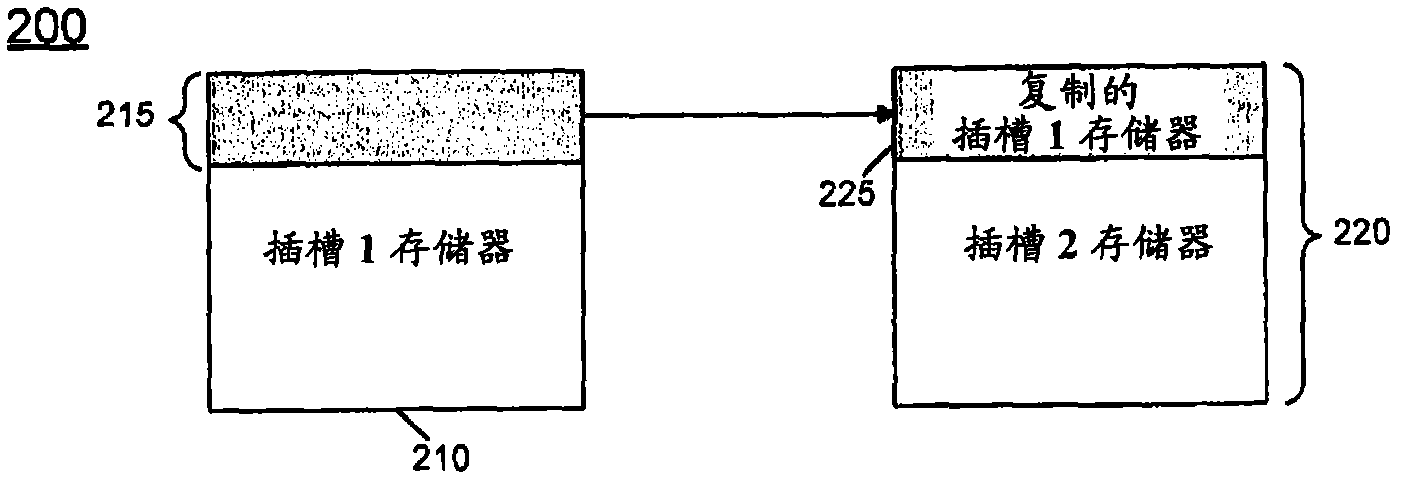

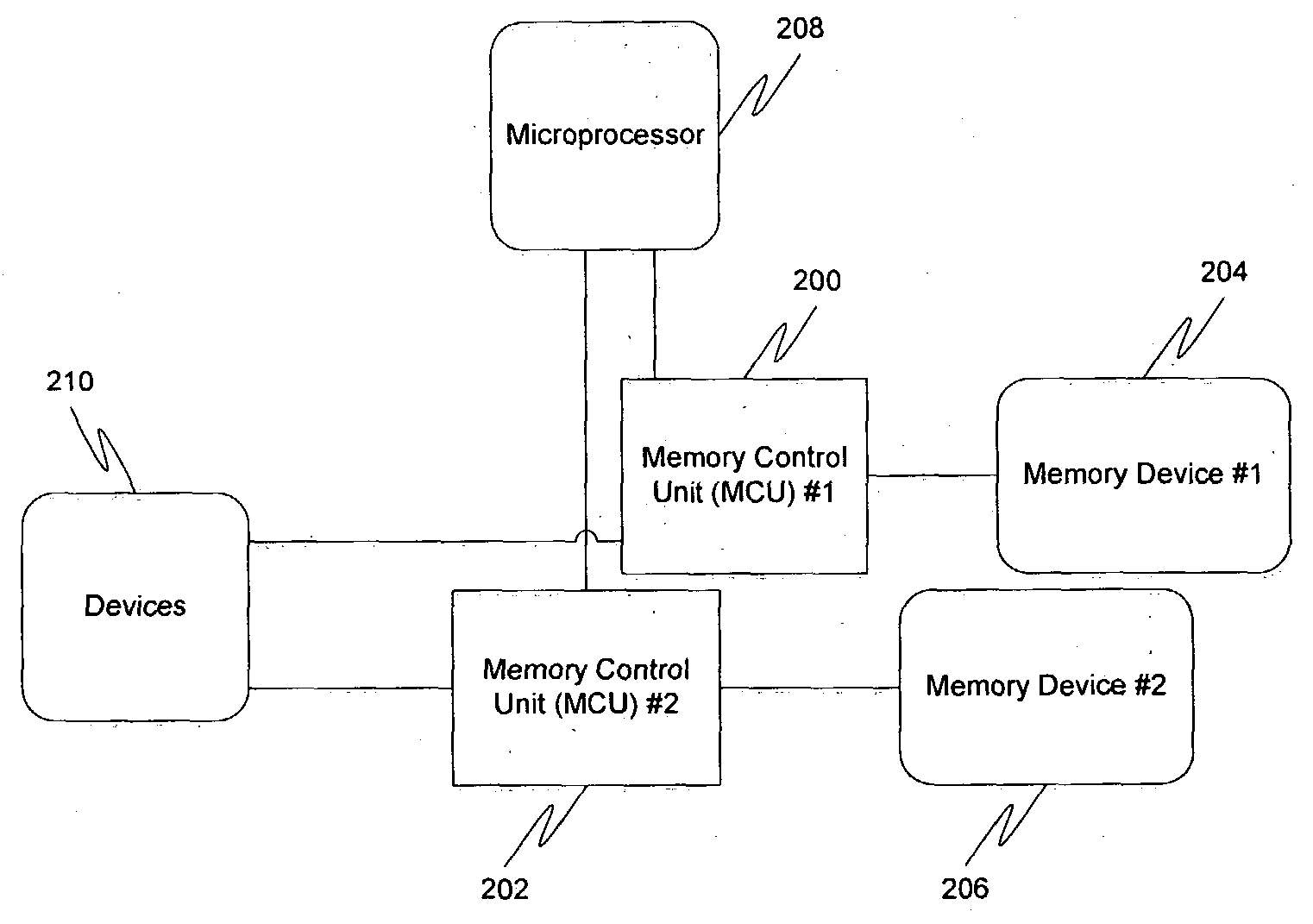

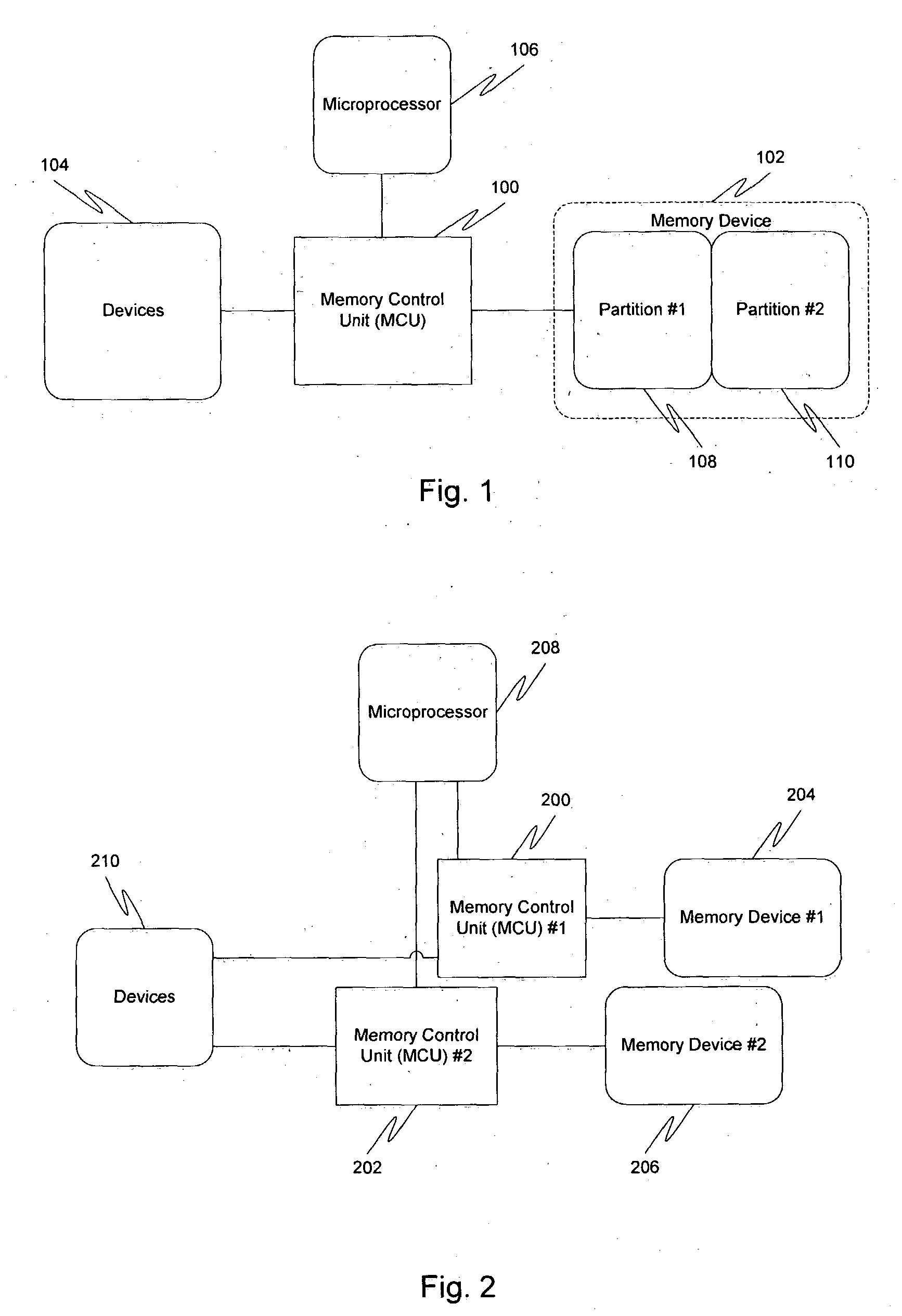

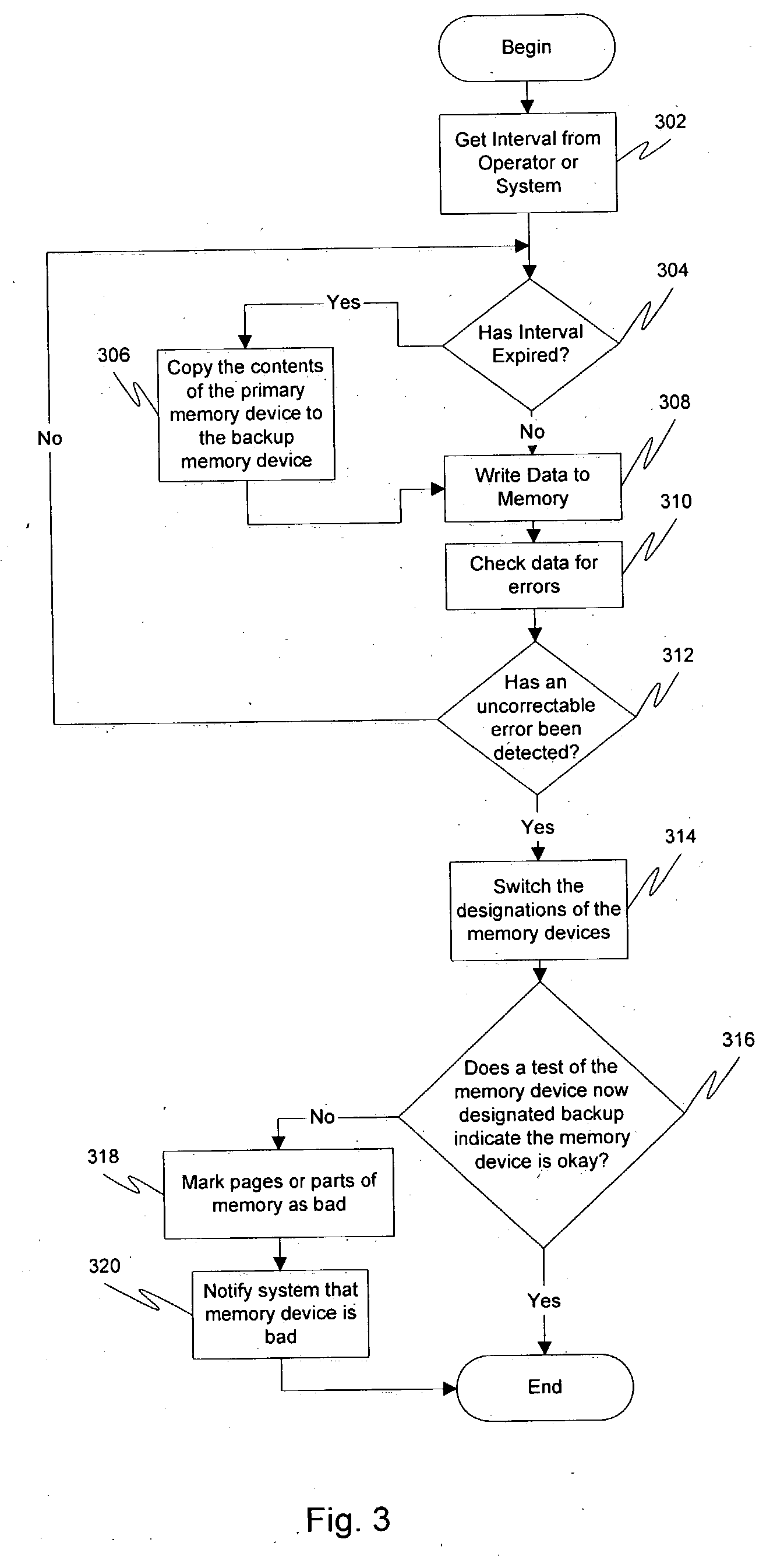

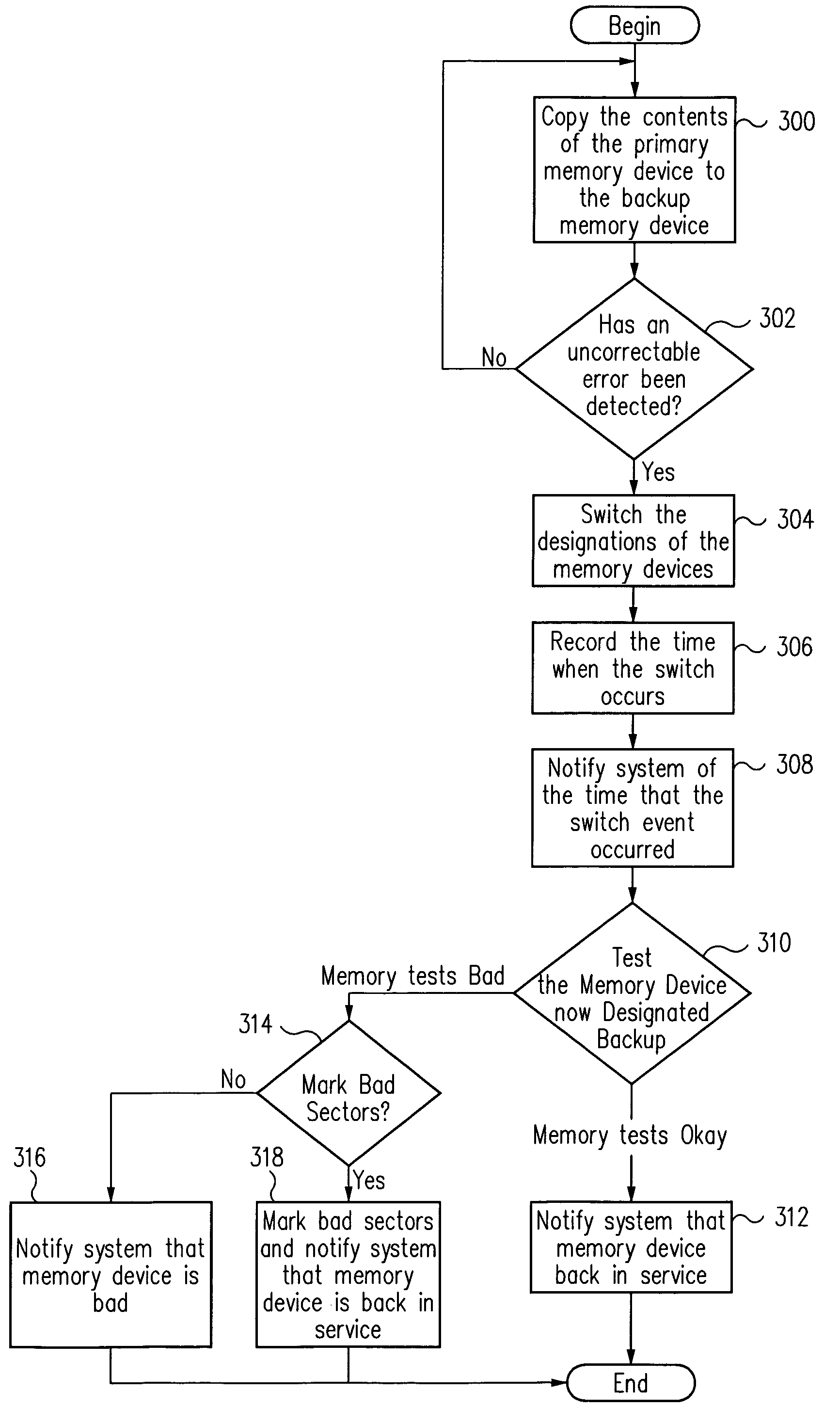

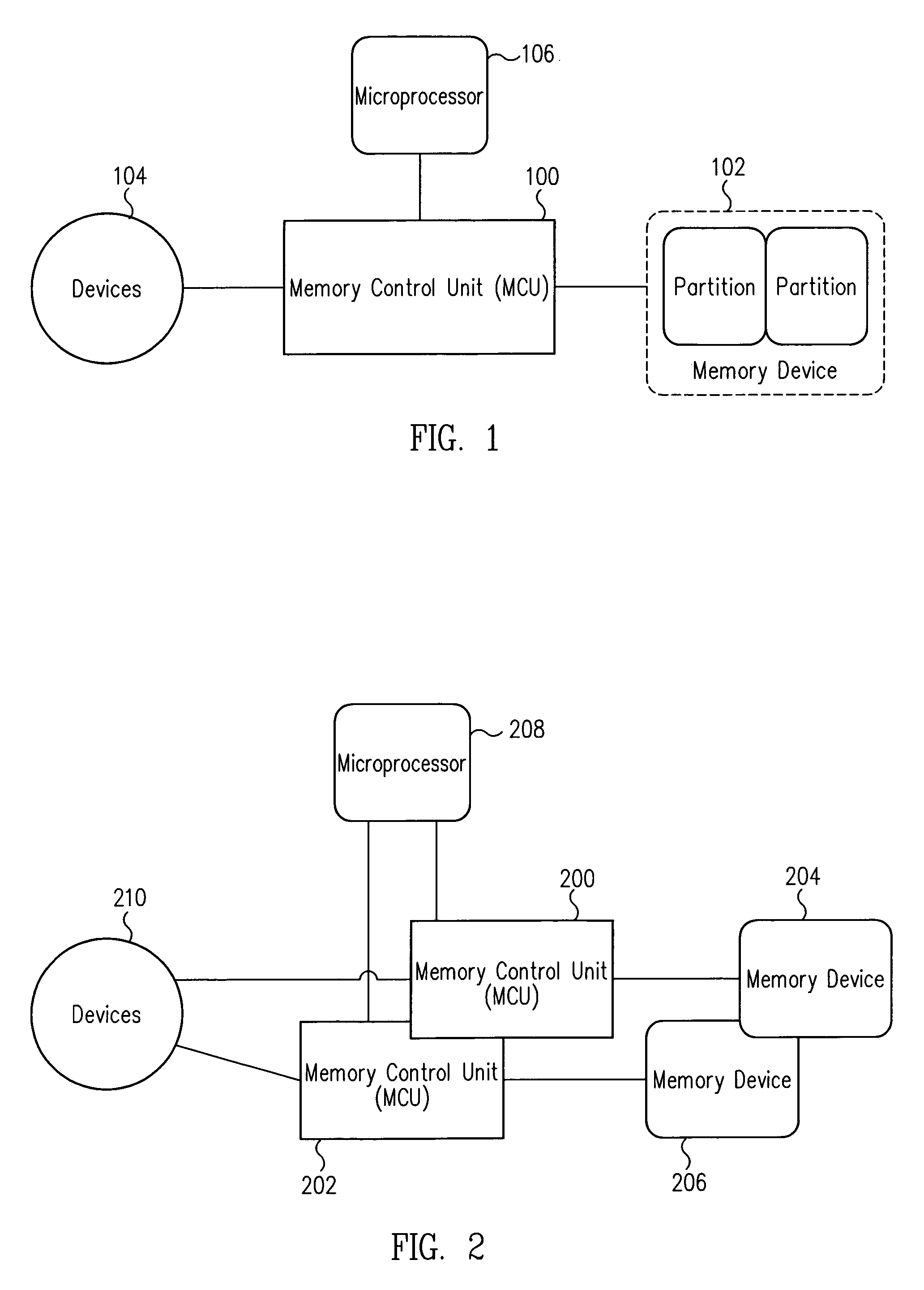

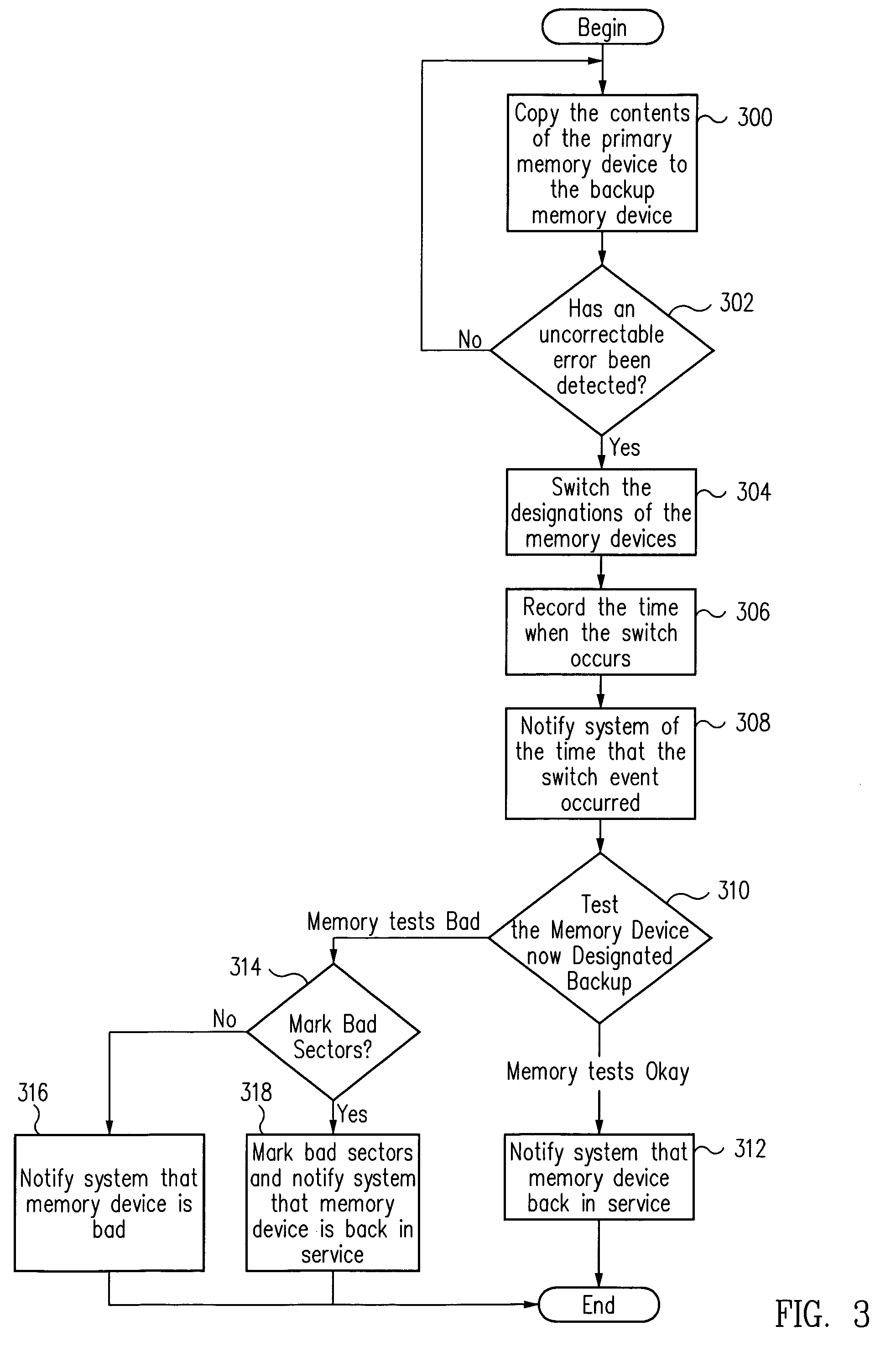

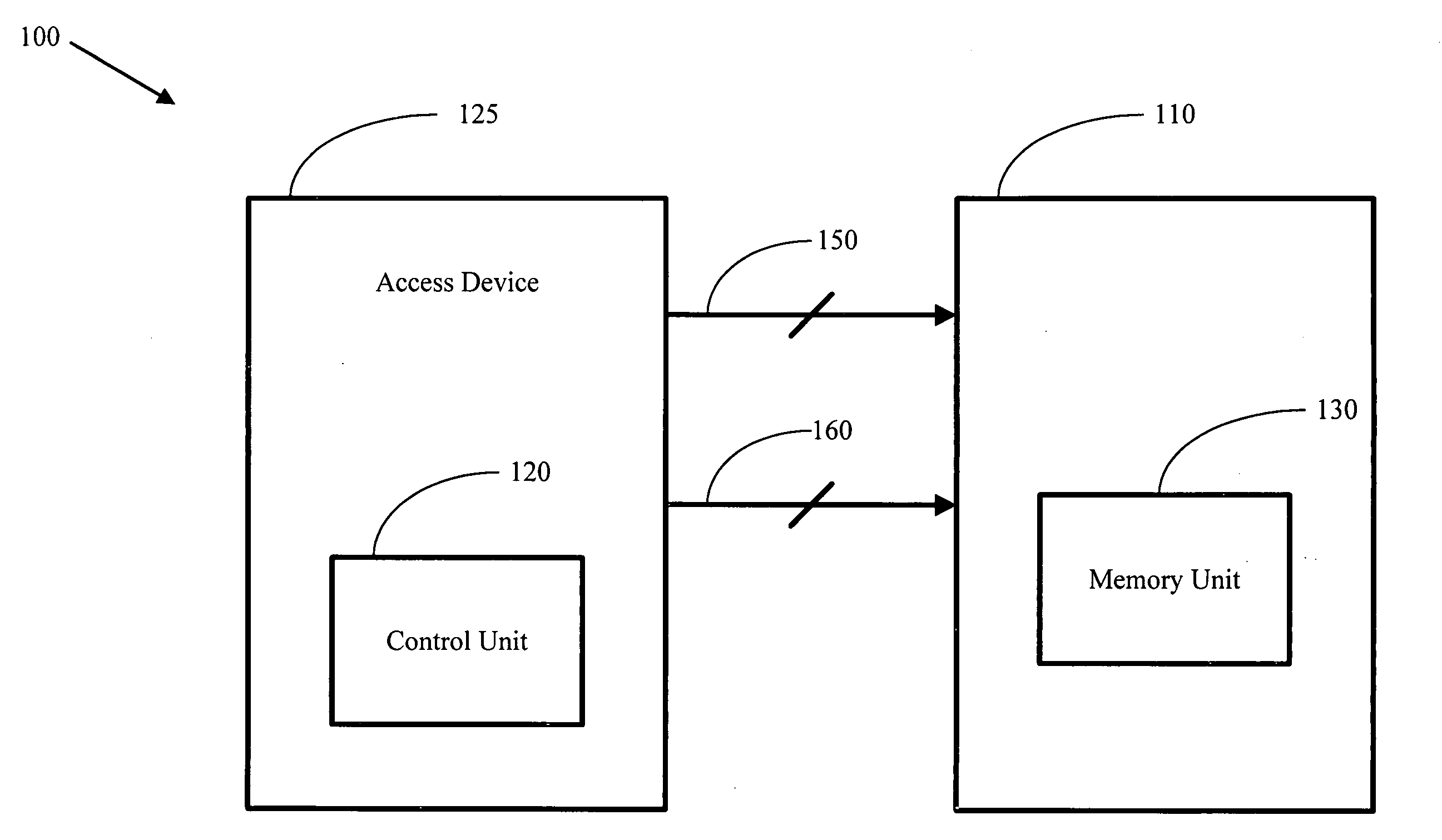

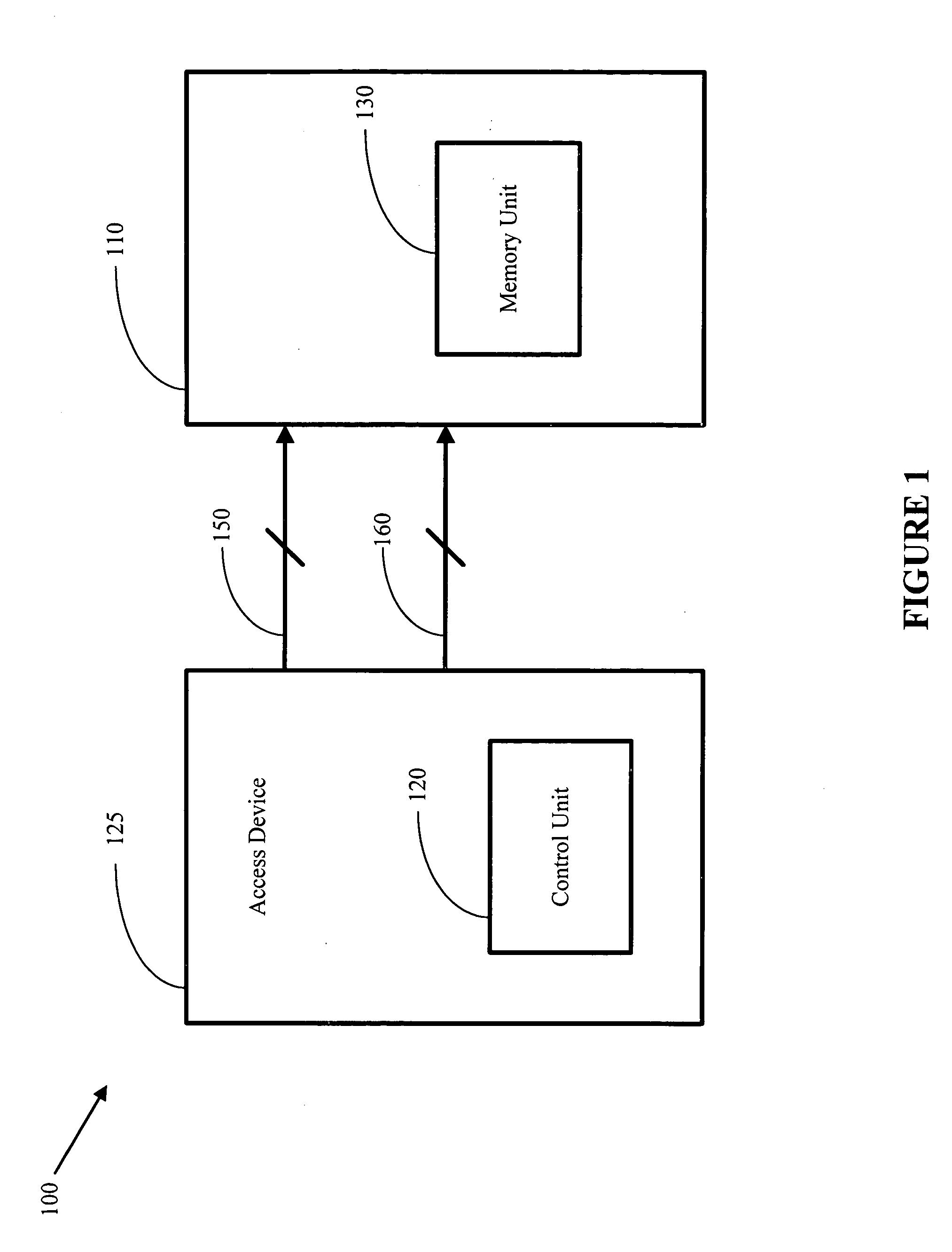

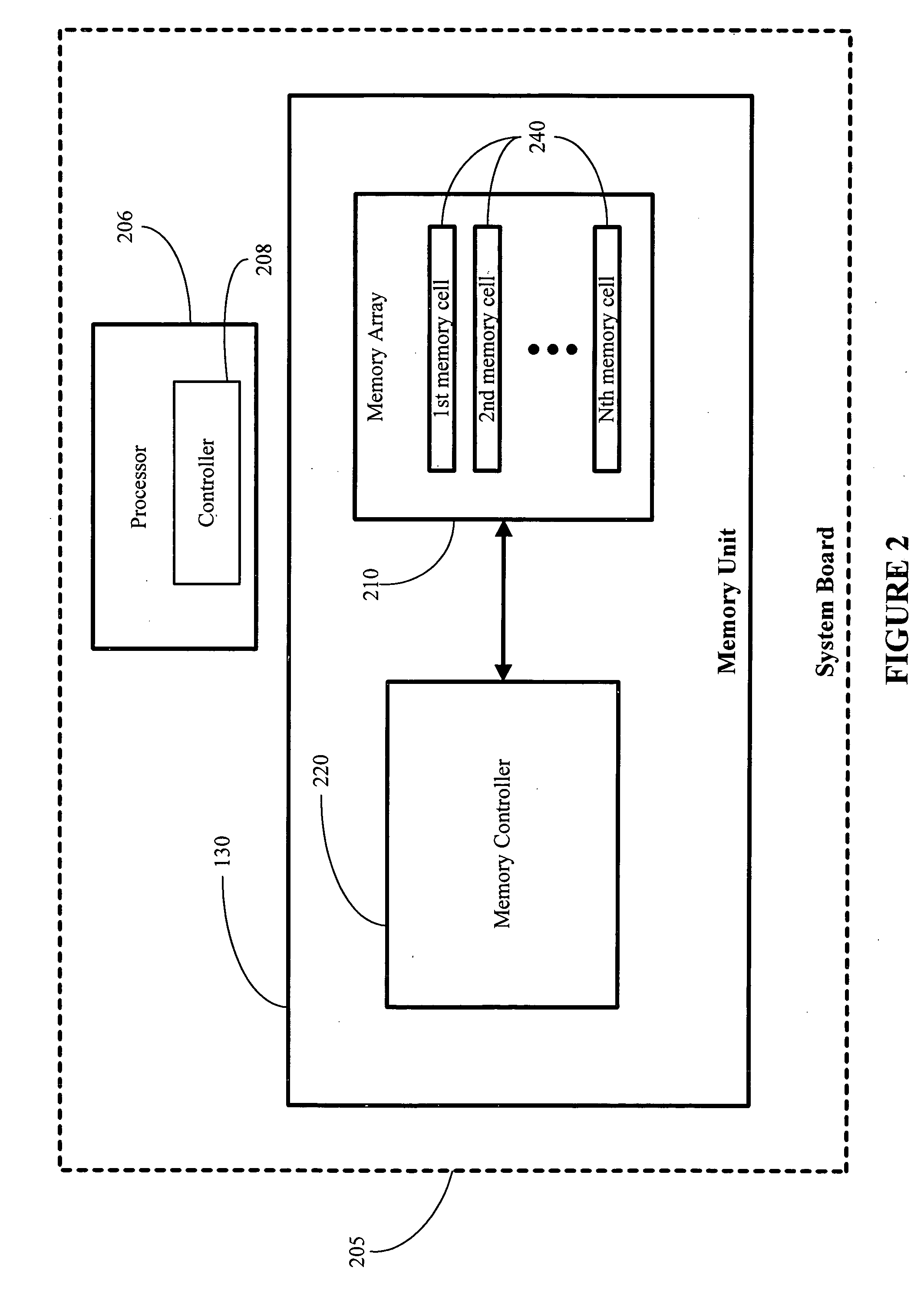

Method and apparatus for memory redundancy and recovery from uncorrectable errors

A system maintains a copy of data stored in a first memory device in a redundant distinct second memory device. Upon detecting an uncorrectable error in the first memory device, the system then relies on the copy of the data in the second memory device. The system, once it starts relying on the data in the second memory device, may then test the first memory device to determine if the uncorrectable error was due to a physical problem or a transient event. If the first memory device is then found to be working correctly, it may, in turn, become a redundant memory device for the second memory device.

Owner:ORACLE INT CORP

Enabling memory redundancy during testing

InactiveUS7930592B2Avoid testingError detection/correctionDigital storageTerm memoryComputer science

A design structure embodied in a machine readable medium for designing, manufacturing, testing and / or enabling a redundant memory element (20) during testing of a memory array (14), and a method of repairing a memory array.

Owner:GLOBALFOUNDRIES INC

Method and apparatus for memory redundancy and recovery from uncorrectable errors

A system maintains a copy of data stored in a first memory device in a redundant distinct second memory device. Upon detecting an uncorrectable error in the first memory device, the system then relies on the copy of the data in the second memory device. The system, once it starts relying on the data in the second memory device, may then test the first memory device to determine if the uncorrectable error was due to a physical problem or a transient event. If the first memory device is then found to be working correctly, it may, in turn, become a redundant memory device for the second memory device.

Owner:ORACLE INT CORP

Semiconductor integrated circuit with memory redundancy circuit

Owner:RENESAS ELECTRONICS CORP

Memory redundance circuit techniques

In a memory module having a designated group of memory cells assigned to represent a logical portion of the memory structure, a memory redundancy circuit having a redundant group of memory cells; and a redundancy controller coupled with the designated group and the redundant group. The redundancy controller, which can include a redundancy decoder, assigns the redundant group to the logical portion of the memory structure in response to a preselected memory group condition, e.g., a "FAILED" memory group condition. The redundancy controller also can include selectable switches, for example, fuses, which can encode the preselected memory group condition. The designated group of memory cells and the redundant group of memory cells can be a memory row, a memory column, a preselected portion of a memory module, a selectable portion of a memory module, a memory module, or a combination thereof.

Owner:AVAGO TECH INT SALES PTE LTD

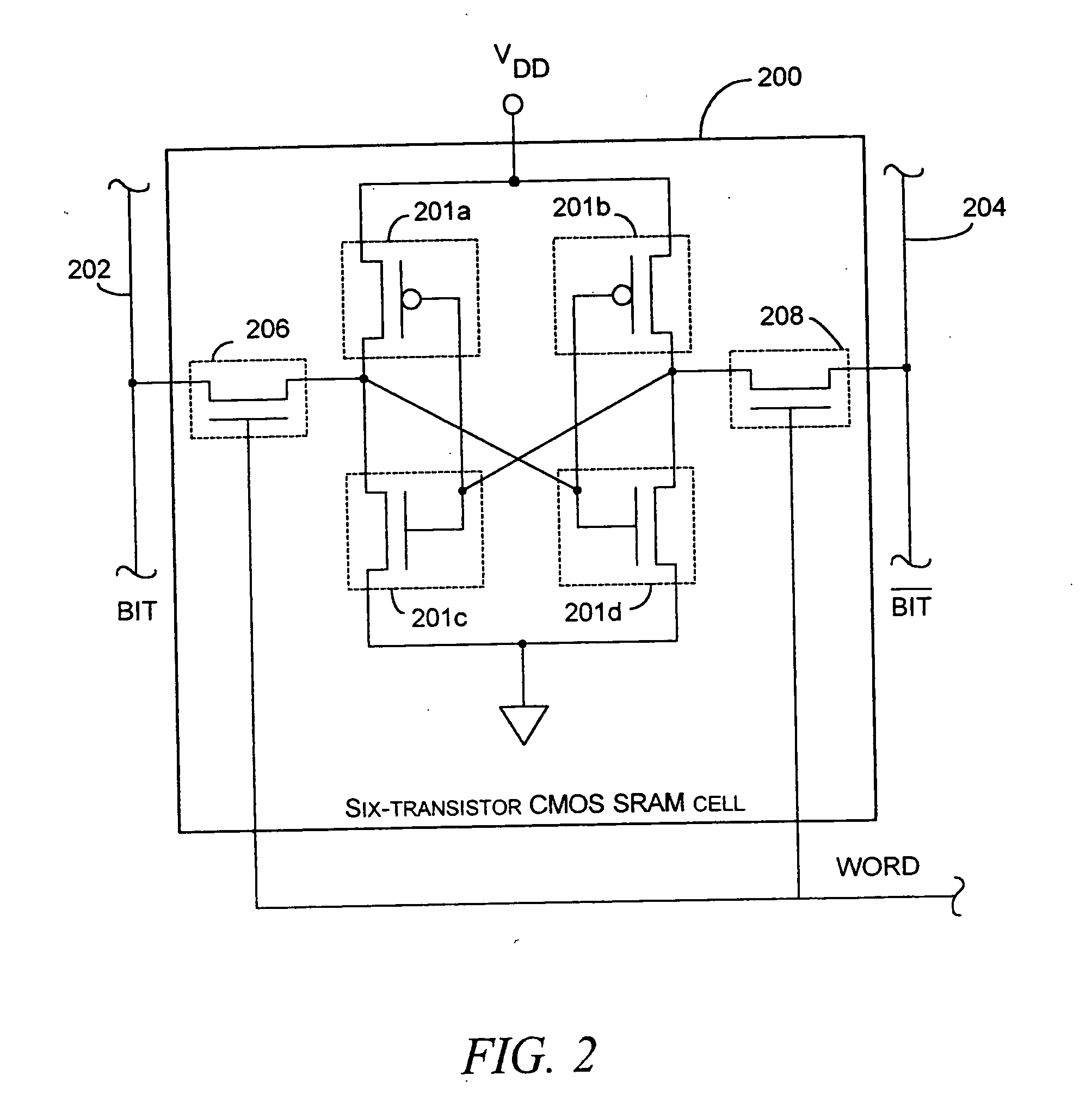

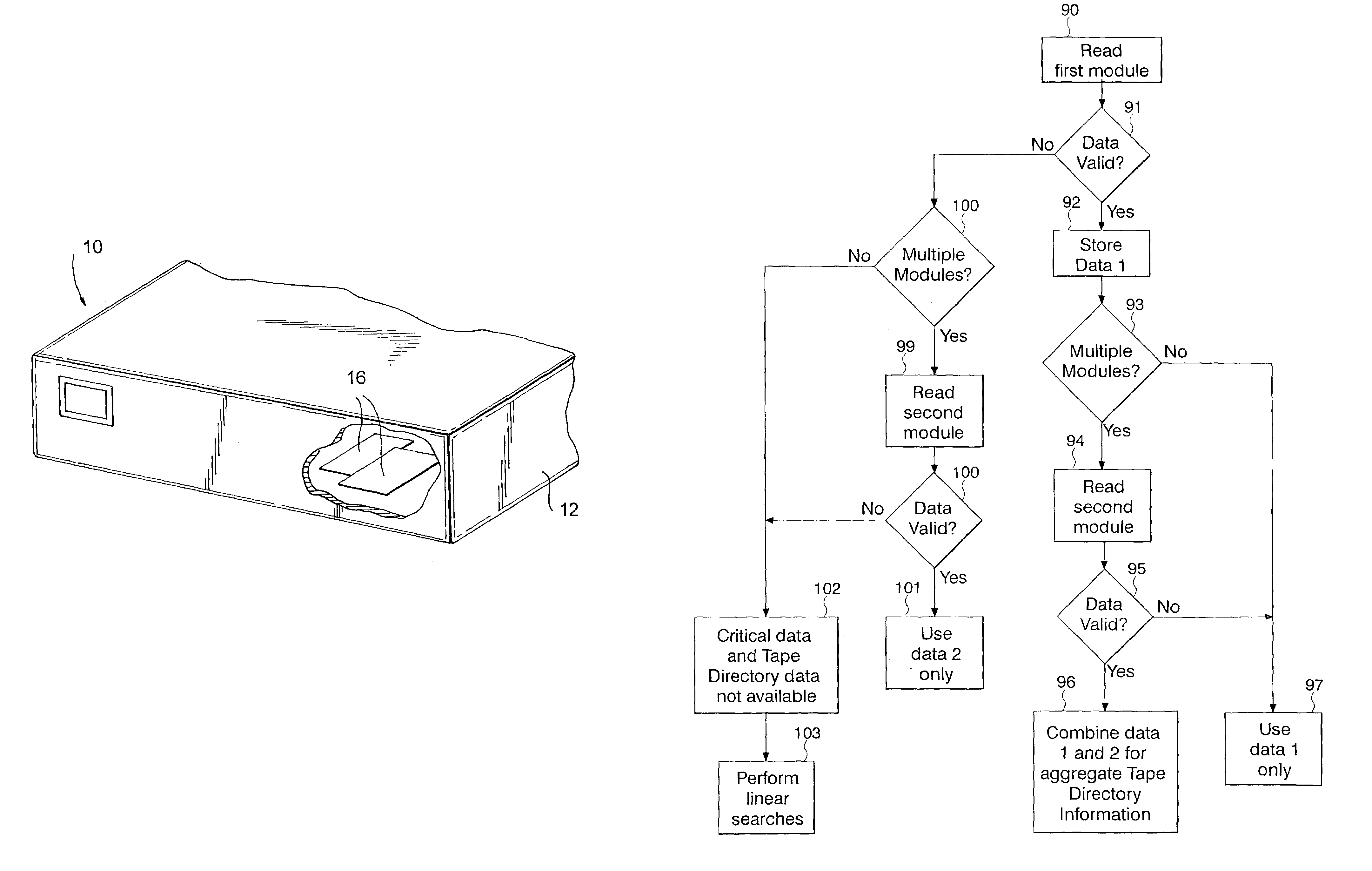

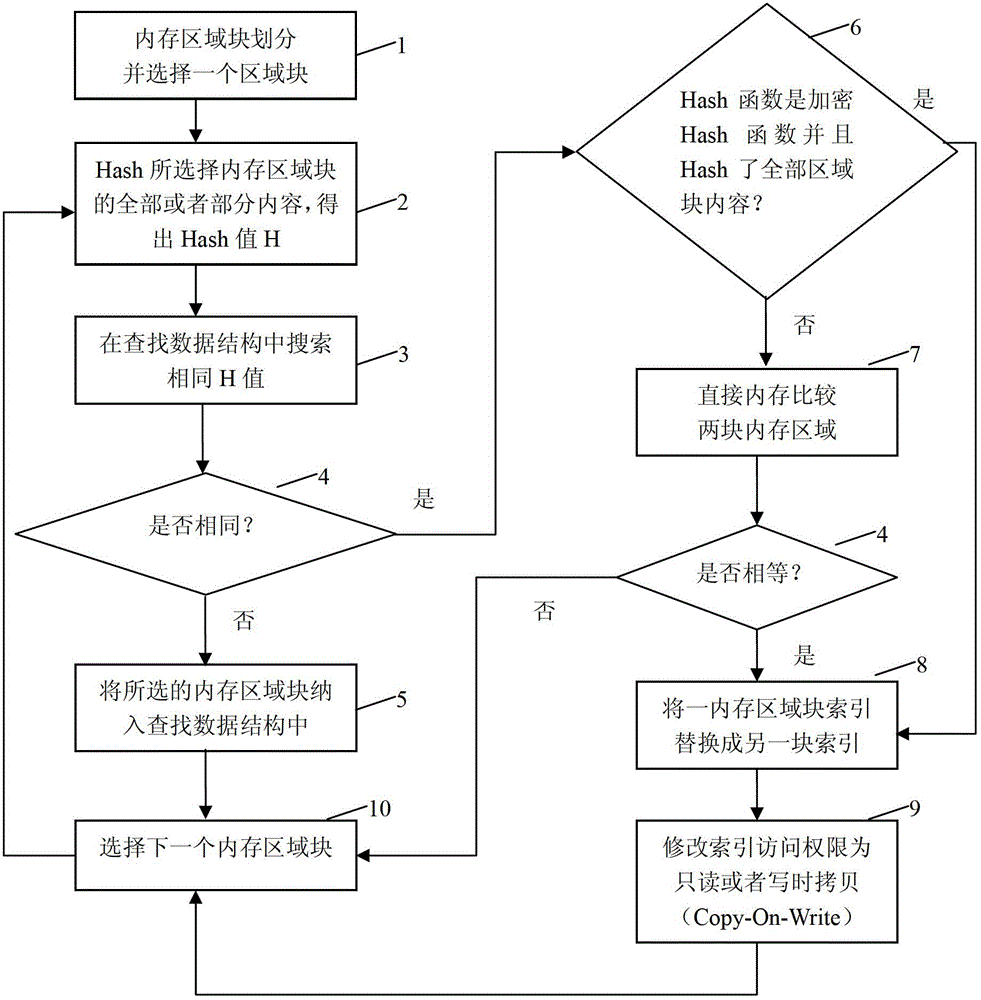

Random access time to data stored on LTO tape by incorporating stacked cartridge memory (CM) modules

InactiveUS7111135B2Provides redundancyIncrease the amount of space available for tape directory storageMemory loss protectionFilamentary/web record carriersMagnetic tapeRandom access memory

A tape cartridge having dual cartridge memory modules to provide memory redundancy, and a method and apparatus for providing redundancy of cartridge memory information within a tape cartridge. The tape cartridge comprises at least first and second cartridge memory modules, each of which stores an identical set of critical information. Each of the first and second cartridge memory modules includes enough critical information to recover from a failure of either of the cartridge memory modules. The method comprises the steps of providing at least two cartridge memory modules in the tape cartridge, and storing an identical set of critical information in each of the two cartridge memory modules. Each of the two cartridge memory modules includes enough critical information to recover from a failure of either cartridge memory module. In a preferred embodiment, the CM modules are stacked one on top of another and increase the amount of space available for tape directory storage.

Owner:IBM CORP

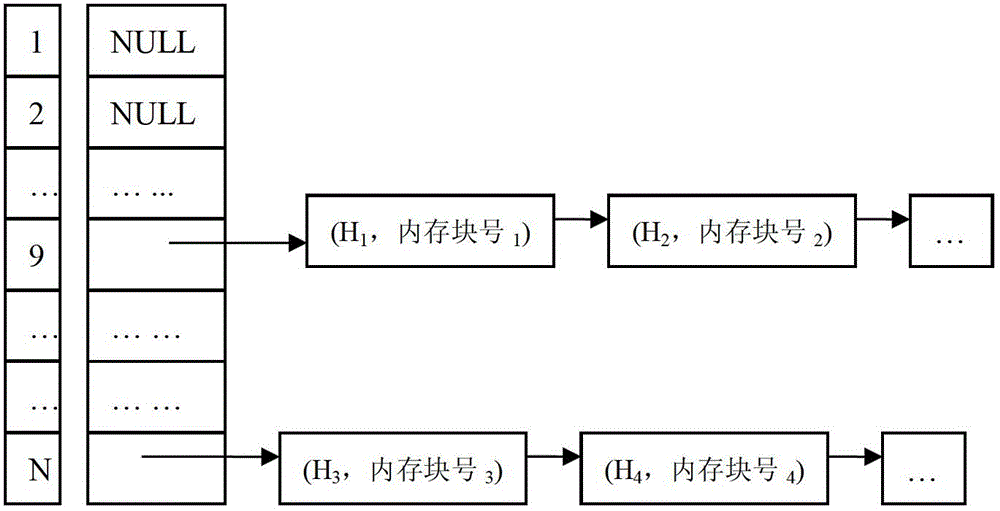

Memory redundancy eliminating method

InactiveCN102722452AImprove efficiencyHigh degree of redundancyMemory adressing/allocation/relocationComputer hardwareHash function

The invention relates to a memory redundancy eliminating method. The method comprises the steps of: 1, dividing a computer memory into different areas and selecting; 2, calculating the Hash value of a current selected area block; 3, searching for whether the Hash value of other area blocks is identical to that in the area block in the step 2; 4, if so, judging that the two area blocks are probably same and switching to step 6; 5, adding the area block and the Hash value into a searching data structure and switching to step 10; 6, if an encrypted Hash function is adopted in the step 2 and all contents of the area block are calculated by the Hash function, switching to step 8; 7, comparing whether the contents of the two area blocks are completely same or not; 8, replacing the index of one of the area blocks by the index of the other; 9, releasing the area block with the replaced index; and 10, selecting an area block from the residual area blocks and returning to the step 2.

Owner:NANJING UNIV

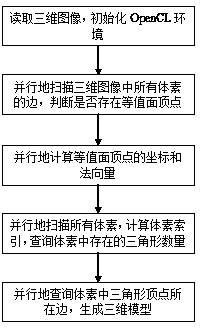

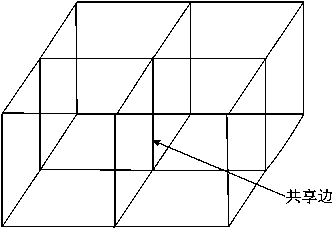

OpenCL (Open Computing Language)-based marching cube method

The invention discloses an OpenCL (Open Computing Language)-based marching cube method, belonging to the technical field of three-dimensional reconstruction. The OpenCL-based marching cube method runs on a computer provided with OpenCL calculation equipment. The method comprises the following steps: reading a three-dimensional image, and initializing an OpenCL environment; scanning the edges of all voxels in the three-dimensional image in parallel, and judging whether contour surface vertexes exist or not; calculating the coordinates and normal vectors of the contour surface vertexes in parallel; scanning all the voxels in parallel, calculating voxel indexes, and inquiring the number of triangles existing in the voxels; inquiring the edges of triangle vertexes in the voxels in parallel to generate a three-dimensional model. Parallel acceleration is performed on an algorithm based on an OpenCL technology; the edges in the voxels are traversed to generate vertexes, and the voxels are traversed to generate the three-dimensional model, so that memory redundancy is eliminated.

Owner:NORTHEASTERN UNIV

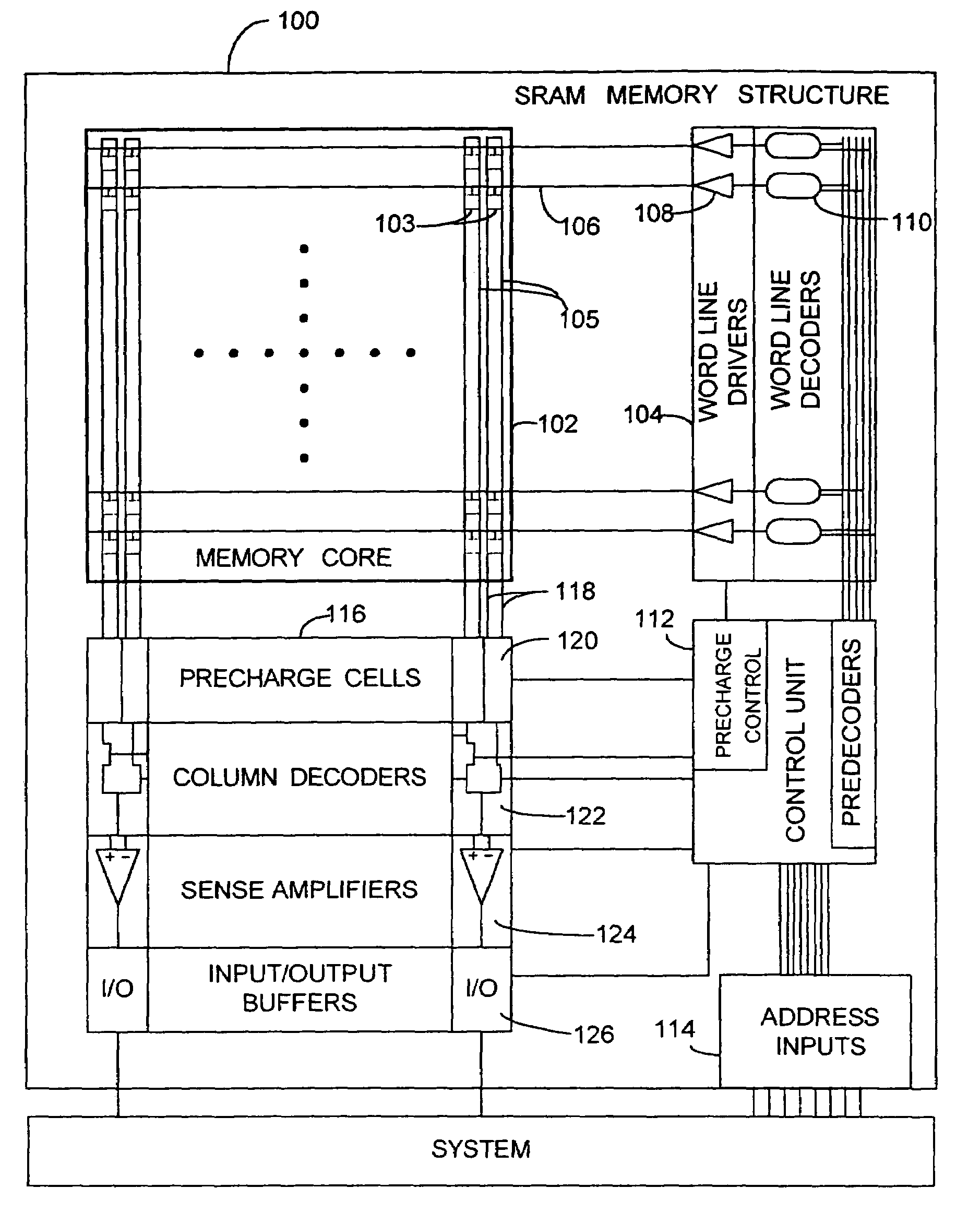

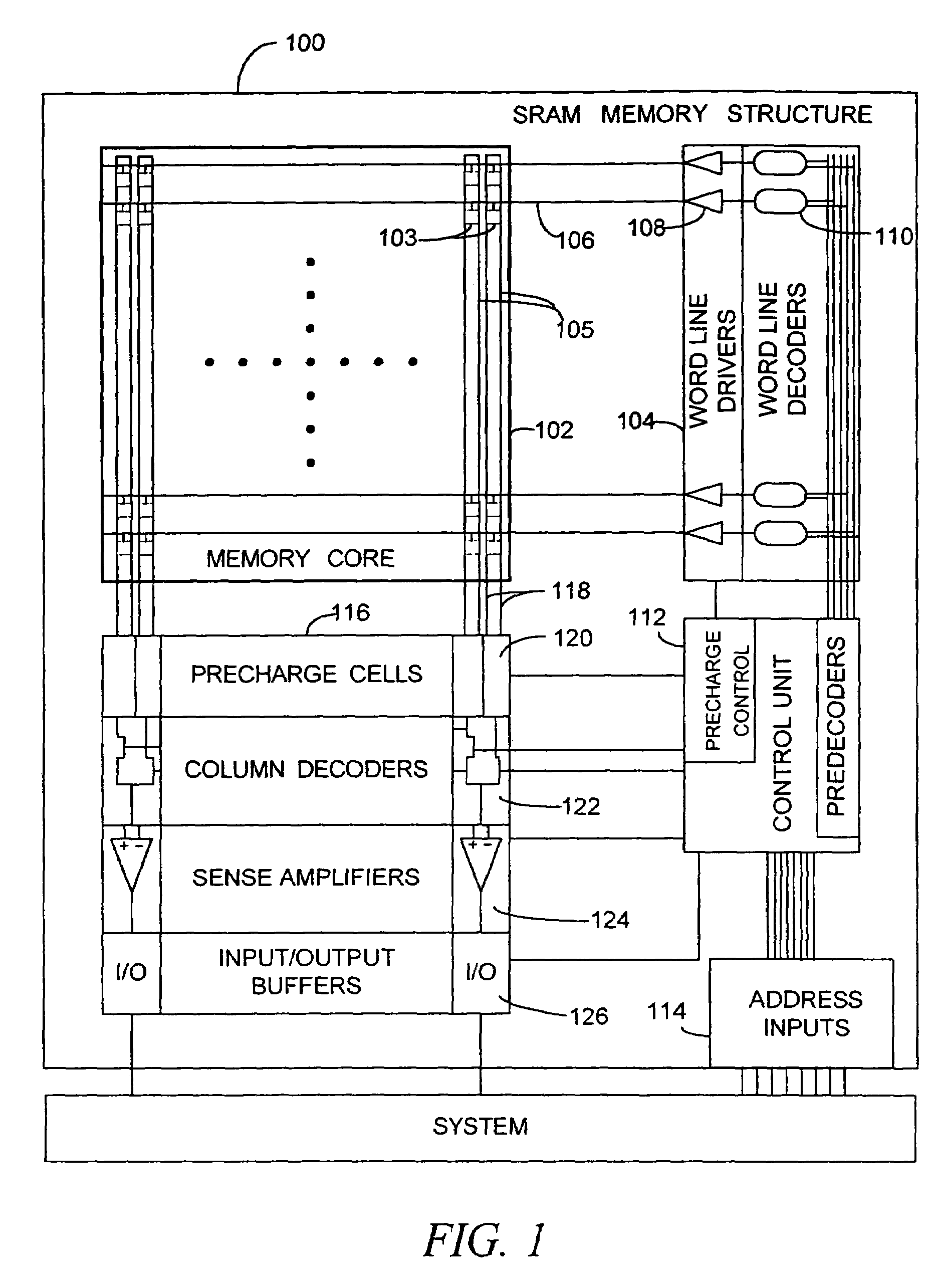

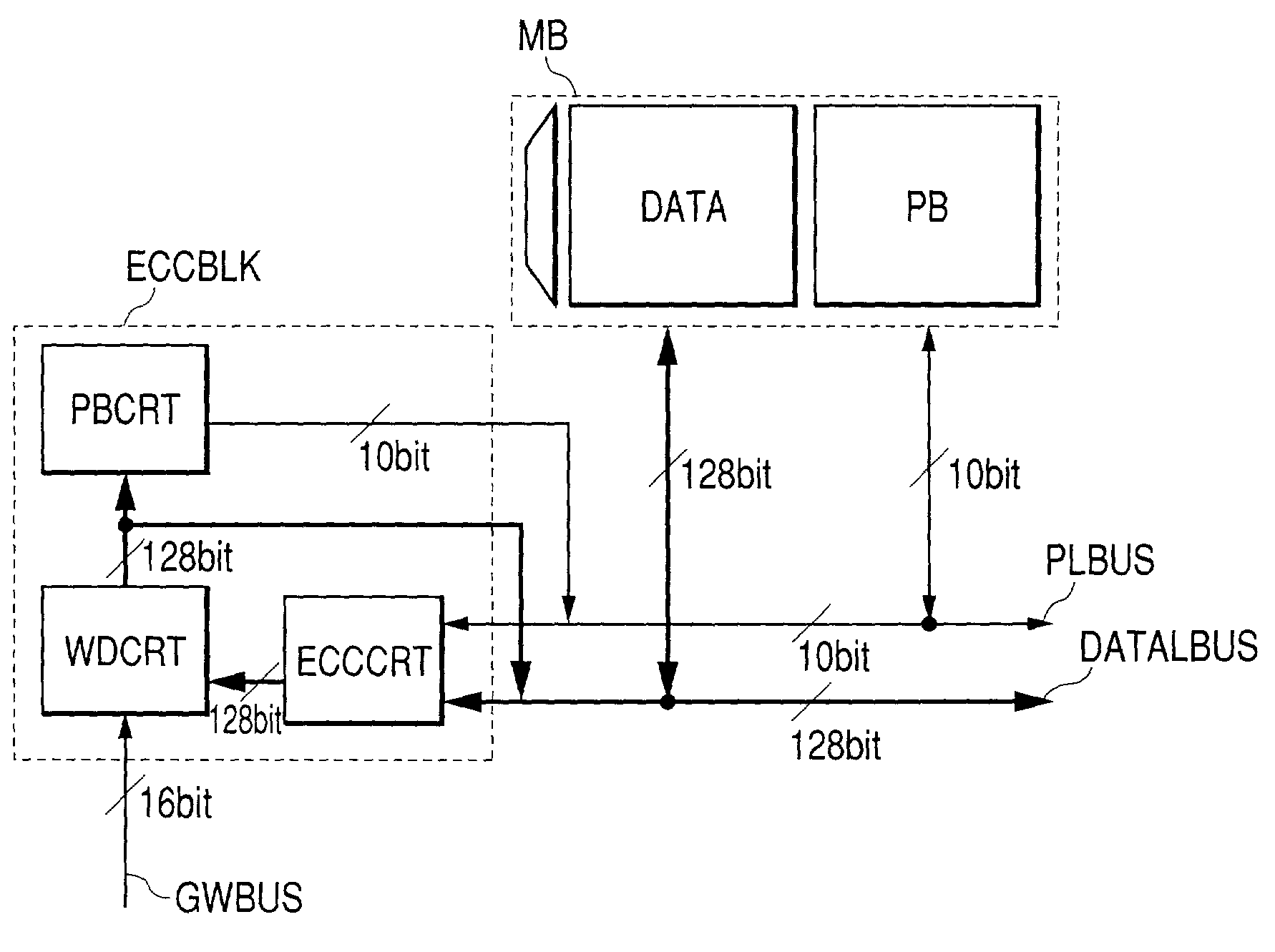

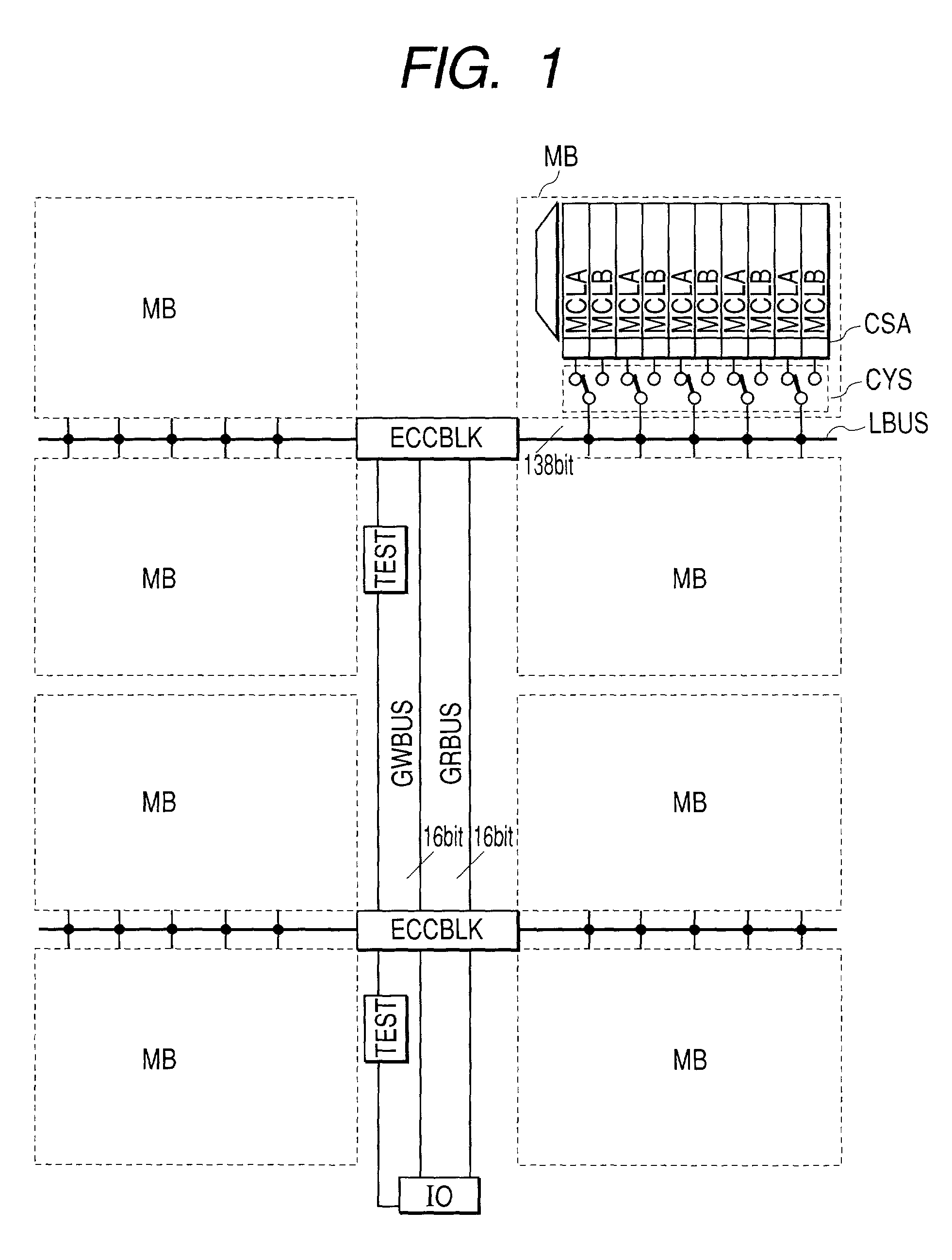

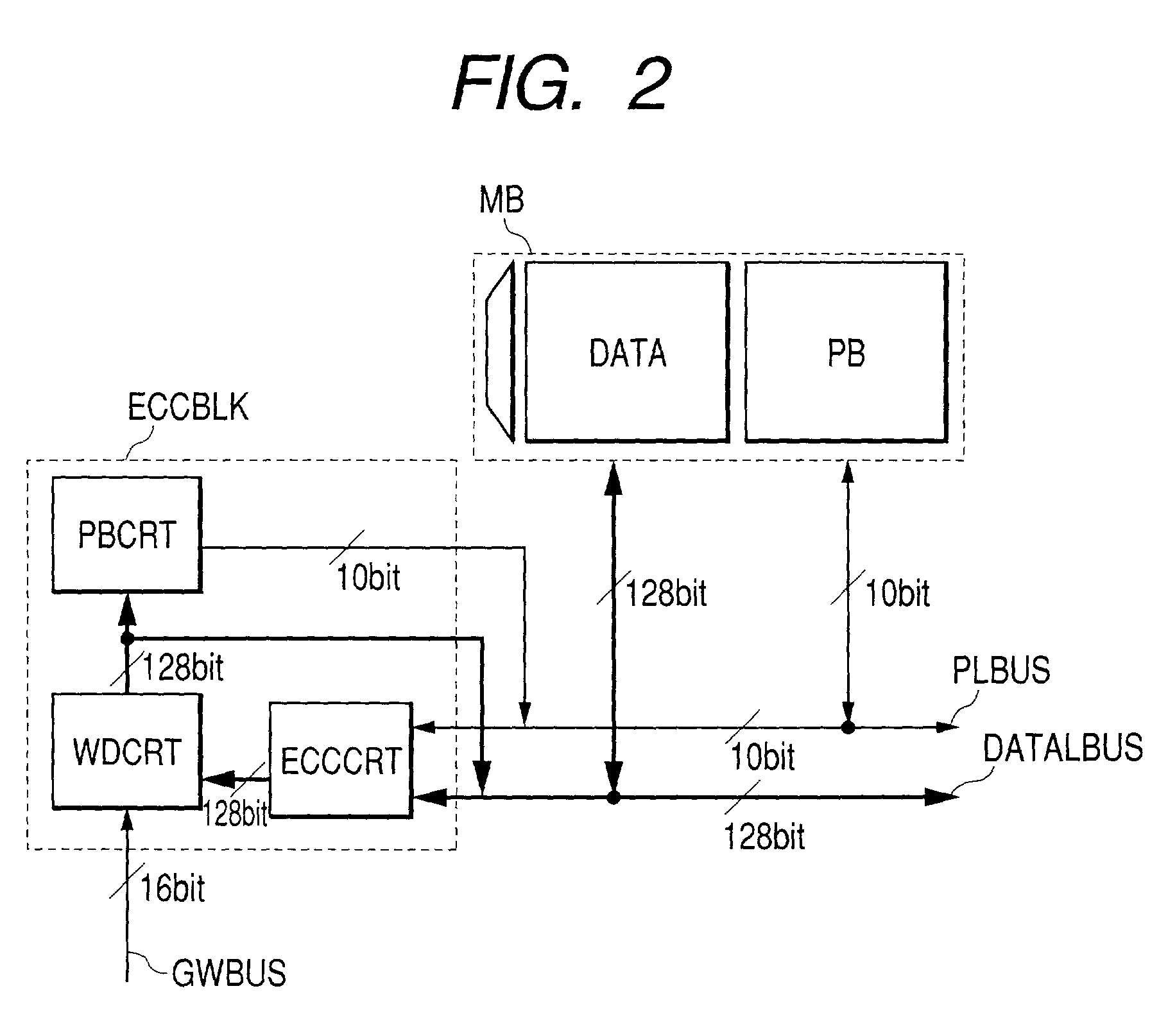

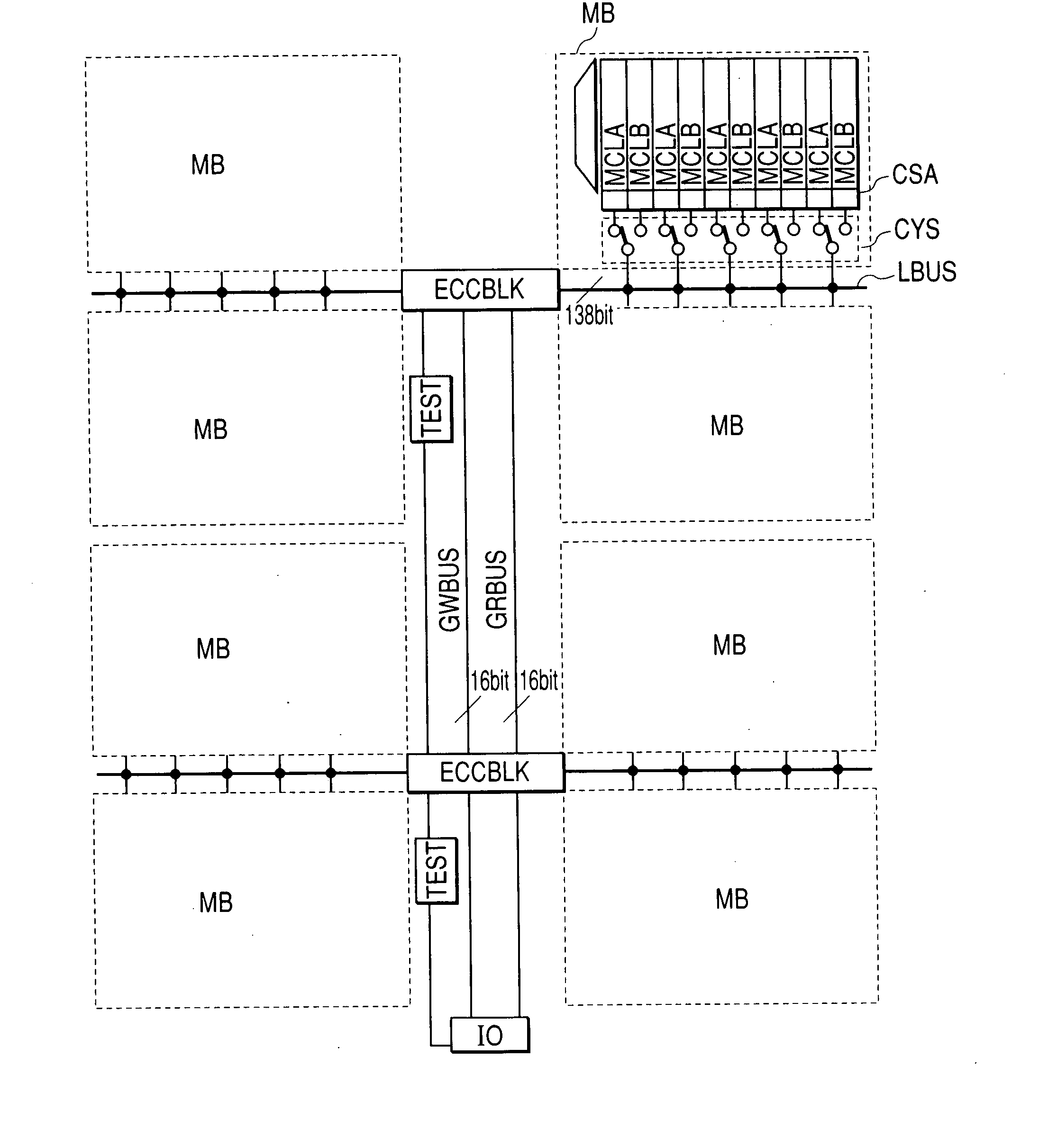

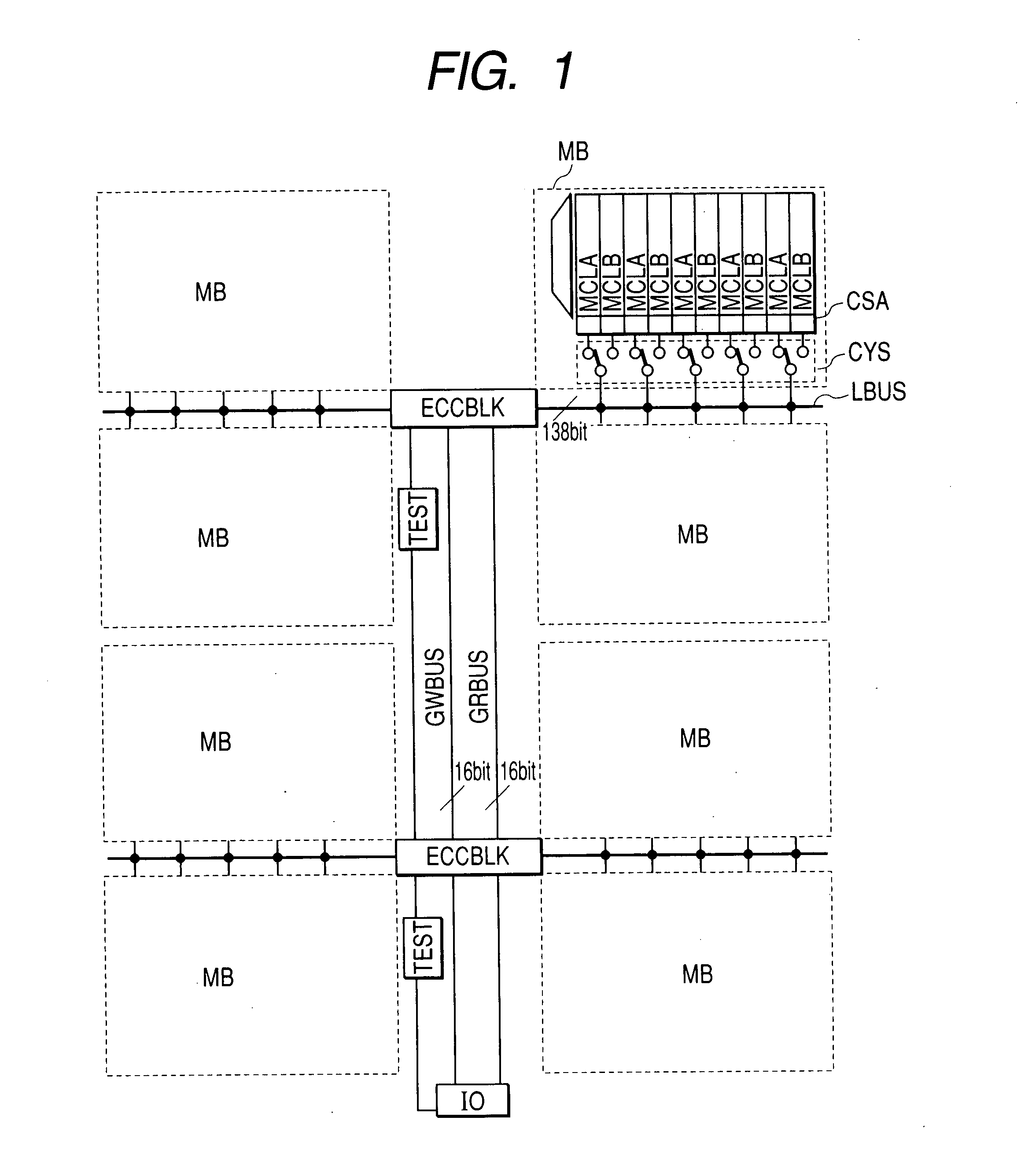

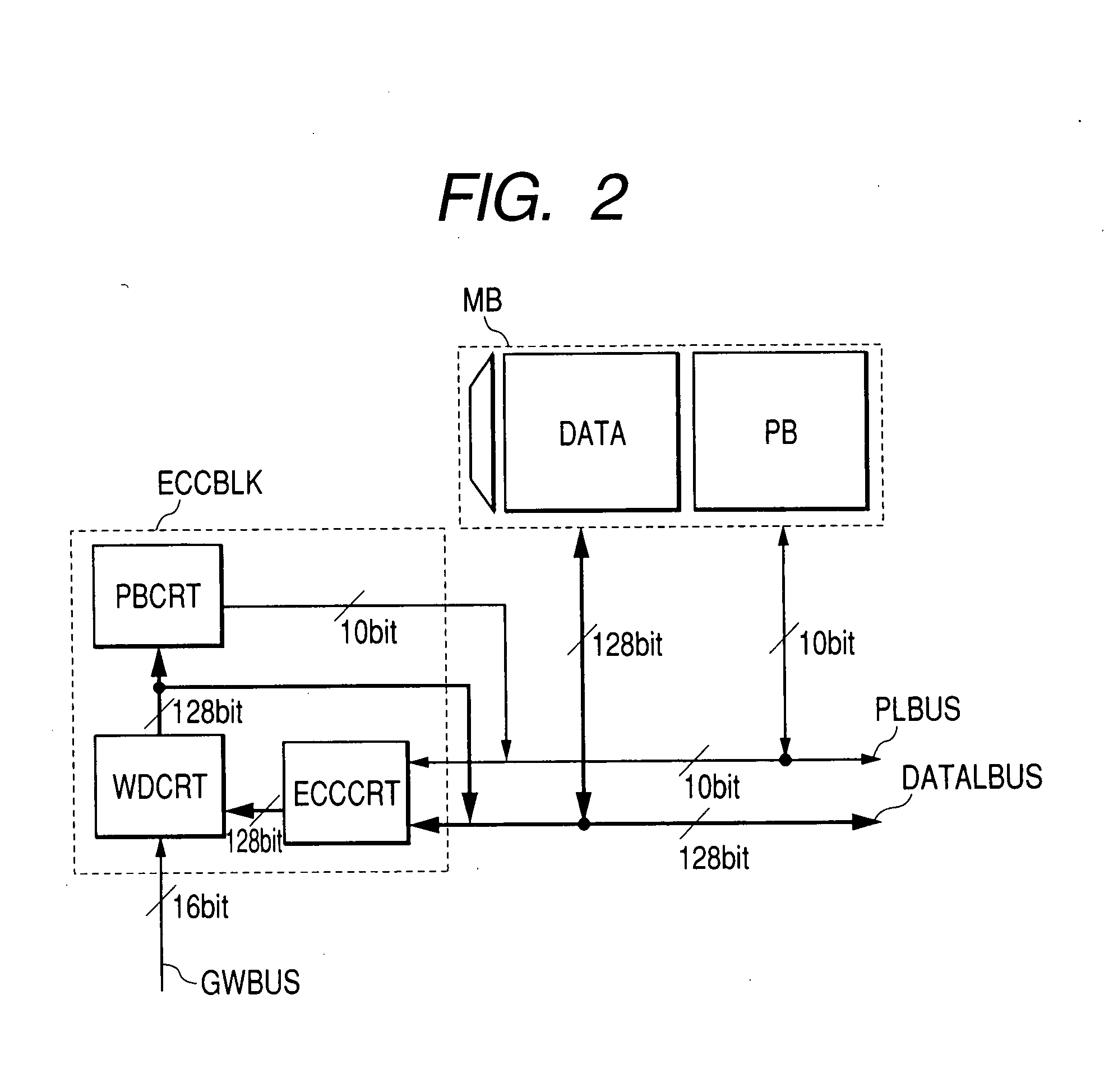

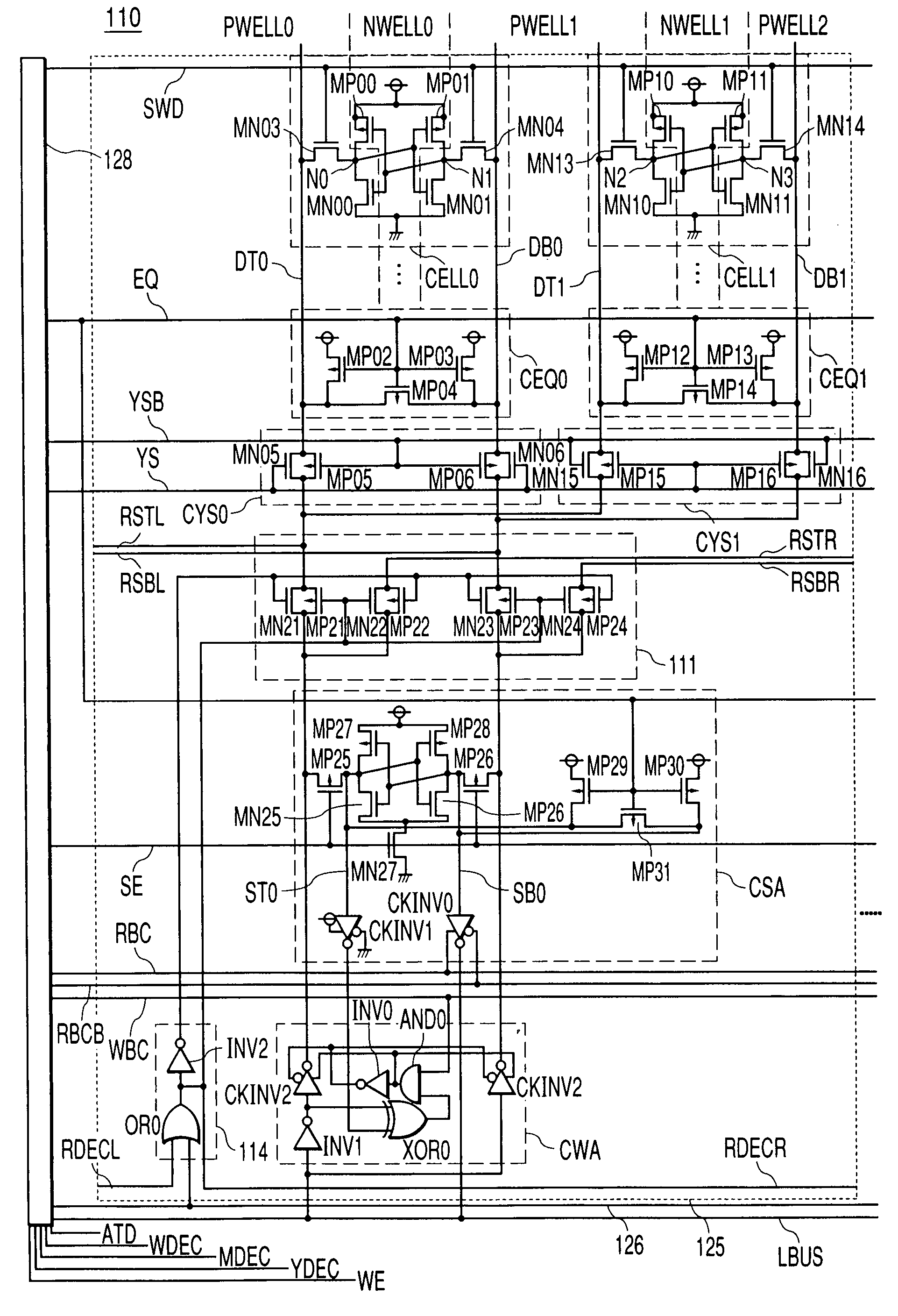

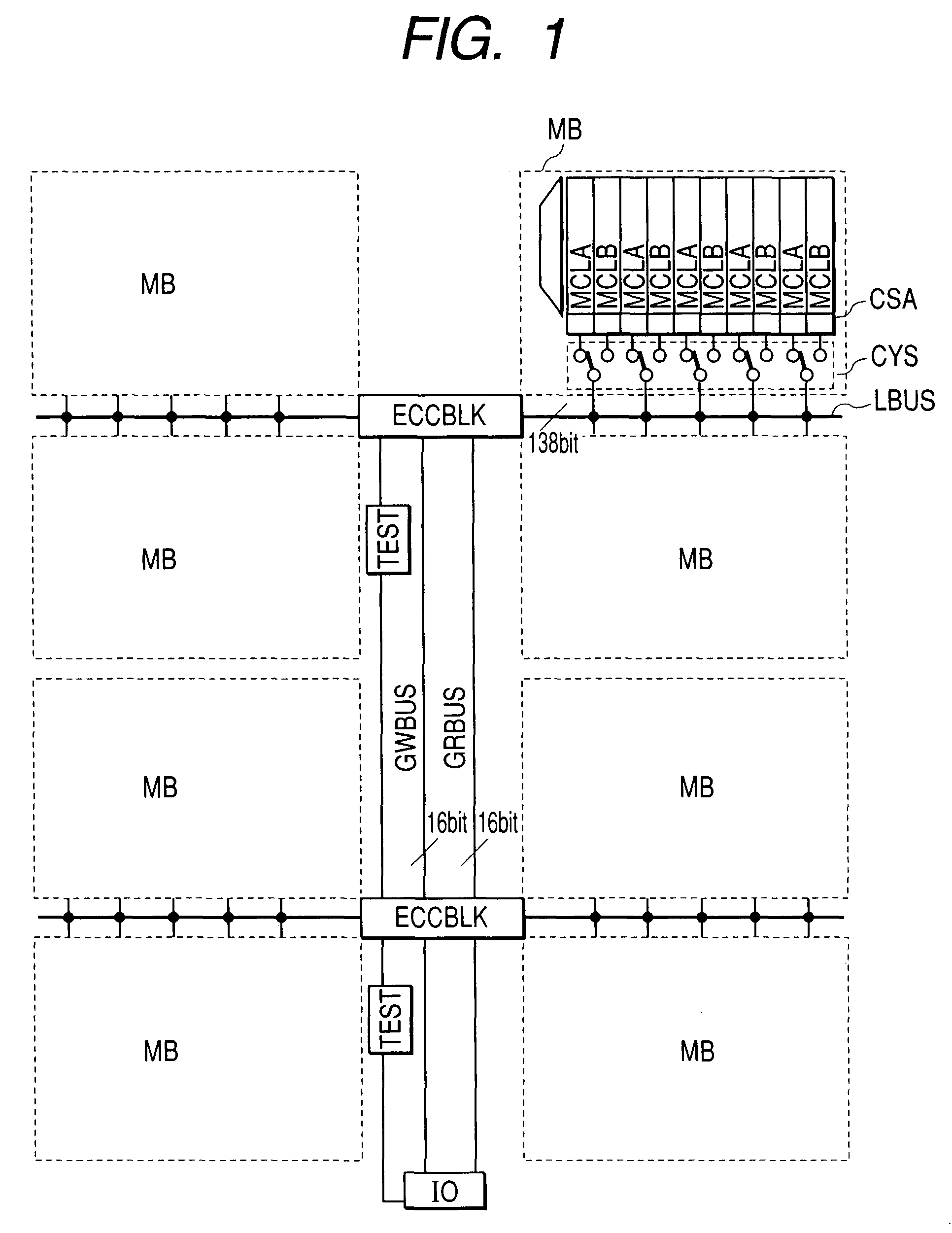

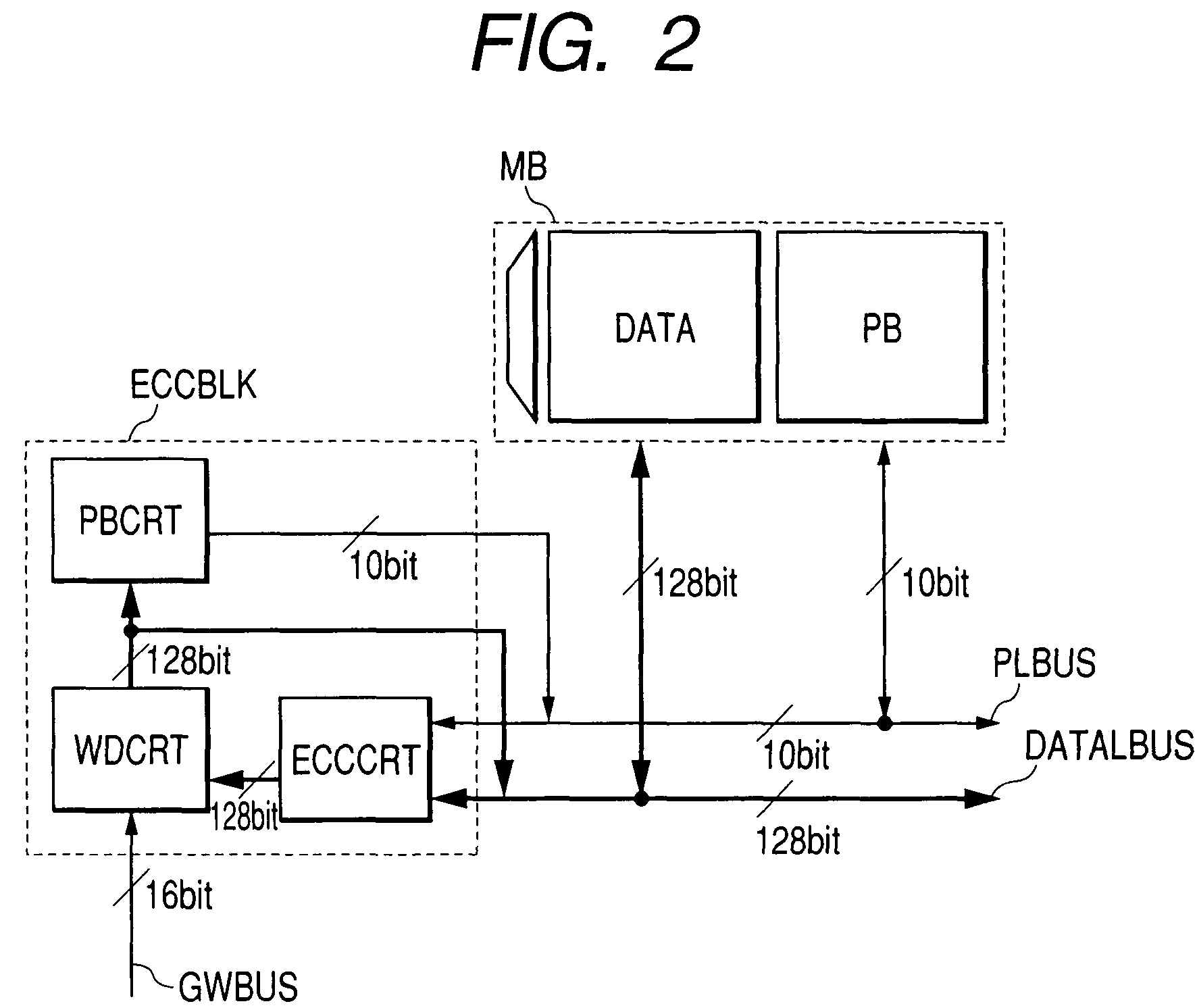

Semiconductor integrated circuit with memory redundancy circuit

A semiconductor integrated circuit with memory redundancy circuit to address the problems of increased area, power consumption and access time which is caused by using an ECC circuit for error correction. The circuit comprises: a plurality of memory mats; a local bus, parallel to word lines, which transfers read data and write data from memory cells; a global bus for writing, parallel to data lines, which transfers write data from an input pad IO; a global bus for reading, parallel to data lines, which transfers read data to an output pad IO; and at least one error correction circuit located at an intersection of the global buses and the local bus. Reading and writing may each be completed in a single cycle, and during a write operation, data which is different from data previously read is written. By this configuration, an increase in area and power consumption can be avoided and errors such as soft errors can be corrected.

Owner:RENESAS ELECTRONICS CORP

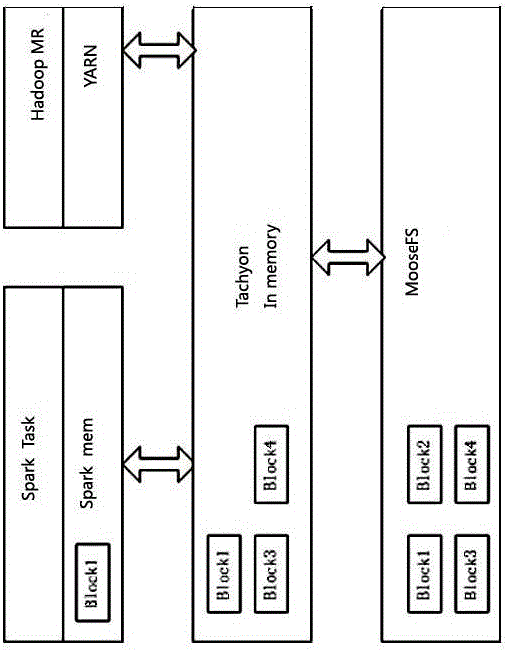

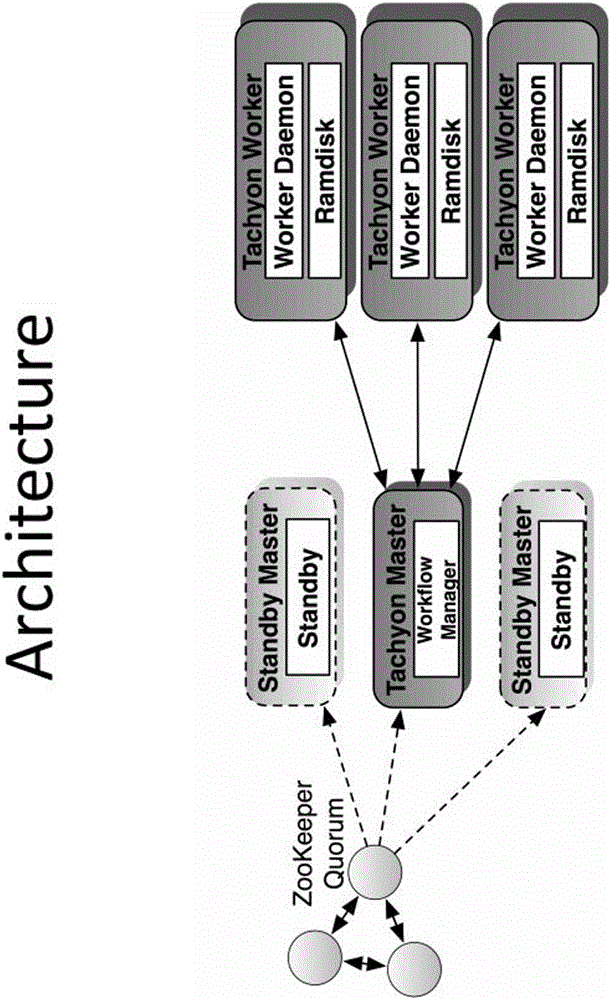

Method for moosefs to realize multilevel storage of files based on Tachyon

InactiveCN106547910AReach transfer rateEasy to manageSpecial data processing applicationsMemory systemsMap reduceDistributed memory

The invention provides a method for a moosefs to realize multilevel storage of files based on a Tachyon and belongs to the fields of cloud storage and big data. Through introducing the Tachyon memory distributed file system into the MooseFS file system, the files in the tachyon can be accessed in a cluster at the memory access speed, and the Tachyon is a middleware between a distributed file storage at the lowest level and various computing frames at the upper level. The main responsibilities are that the files which do not need to fall to a distributed disk file system fall into a distributed memory file system to realize memory sharing, so that the efficiency is improved. Meanwhile, the memory redundancy, the GC time and the like can be reduced. The method also abuts against map reduce and spark computing models of hadoop easily.

Owner:SHANDONG INSPUR COMML SYST CO LTD

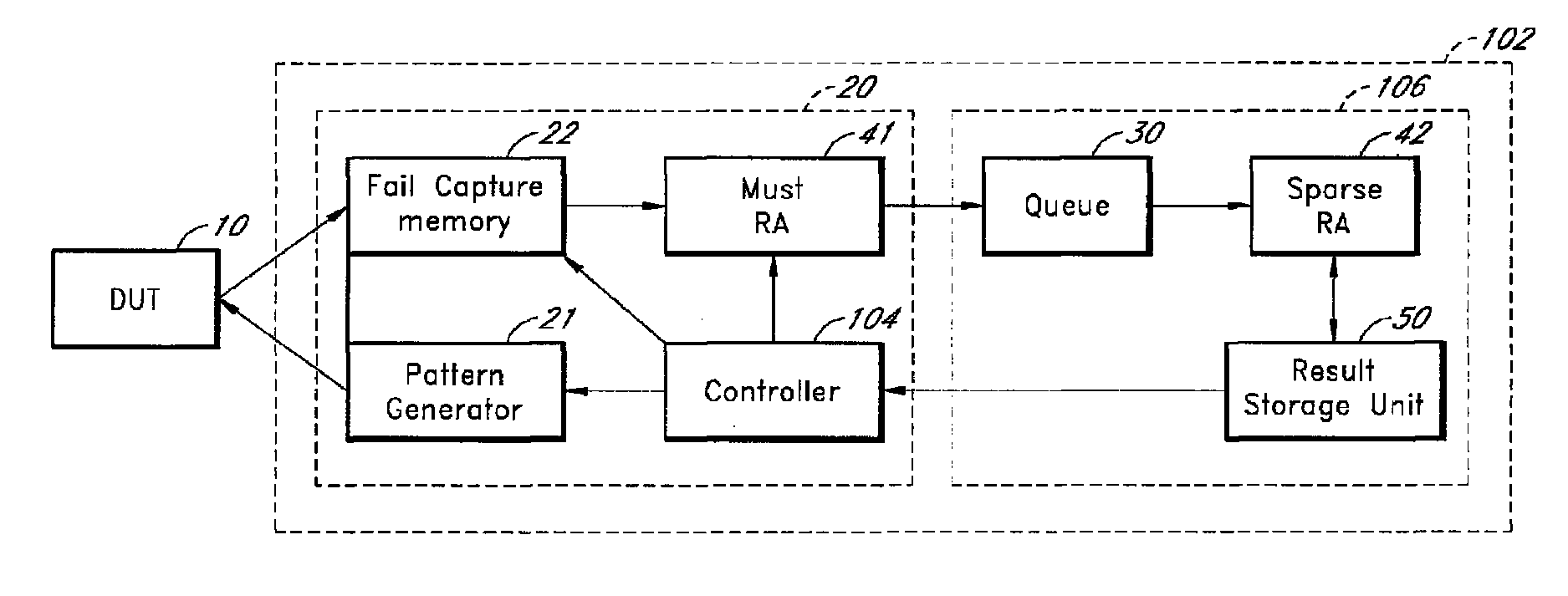

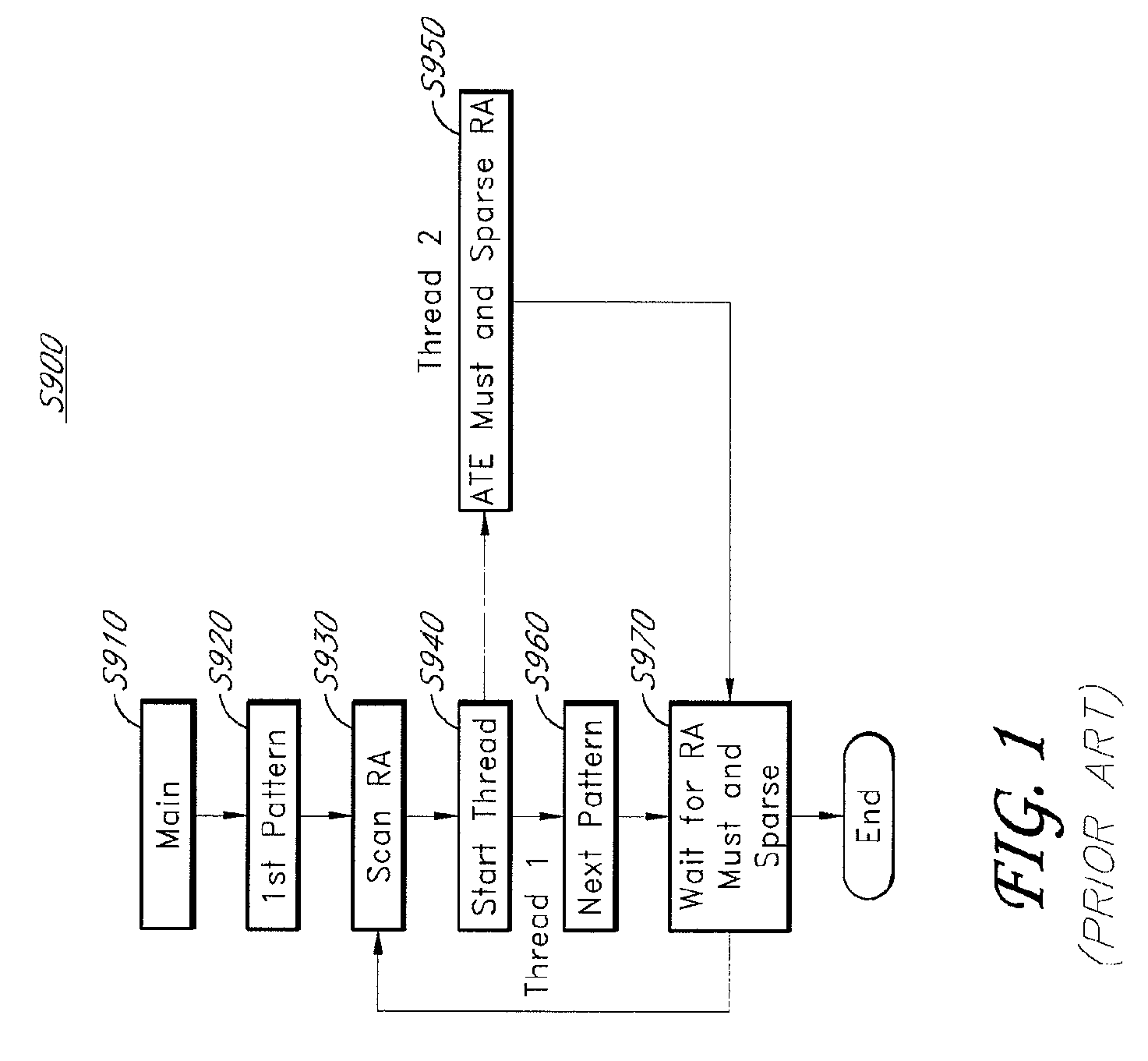

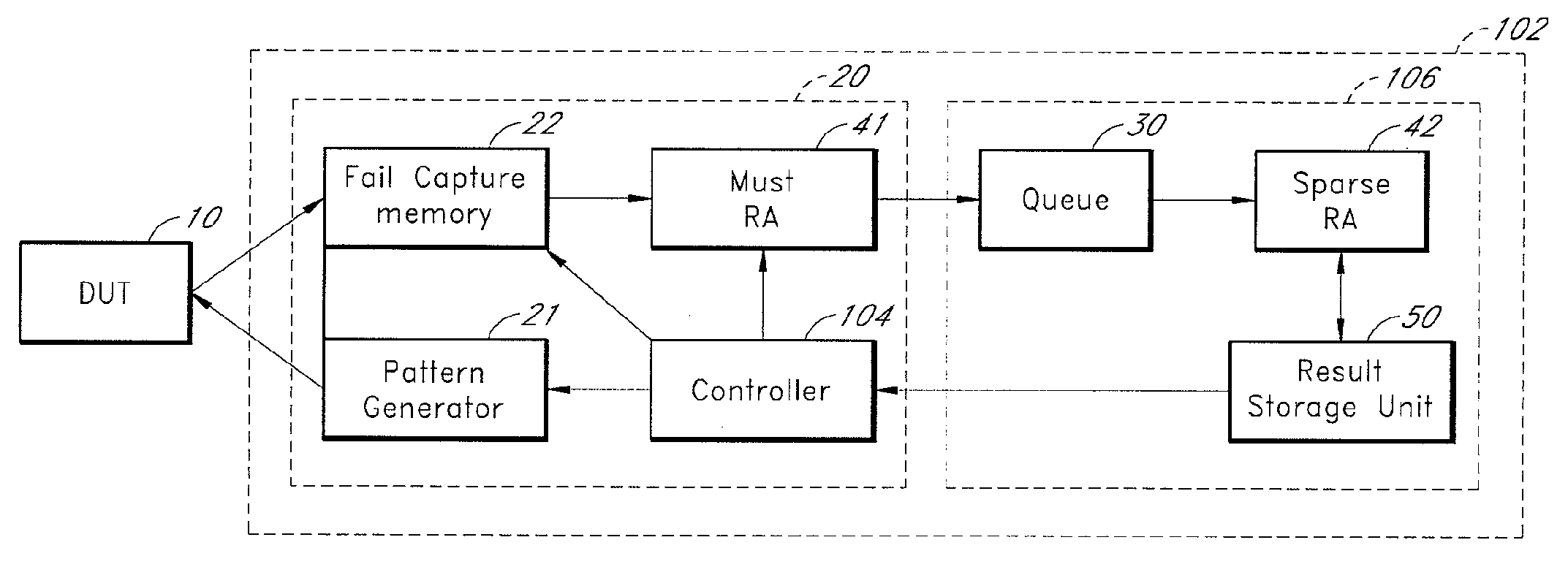

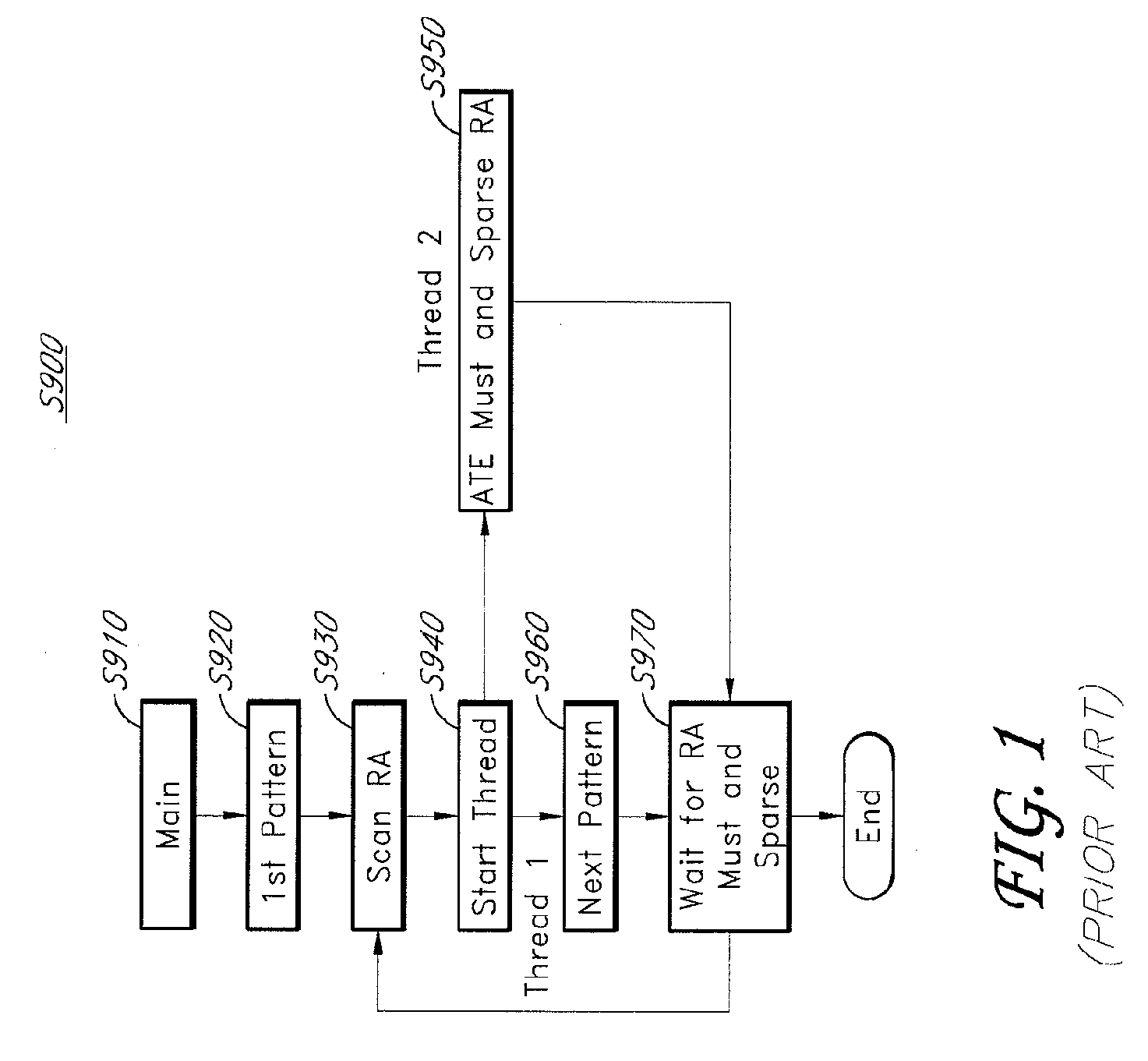

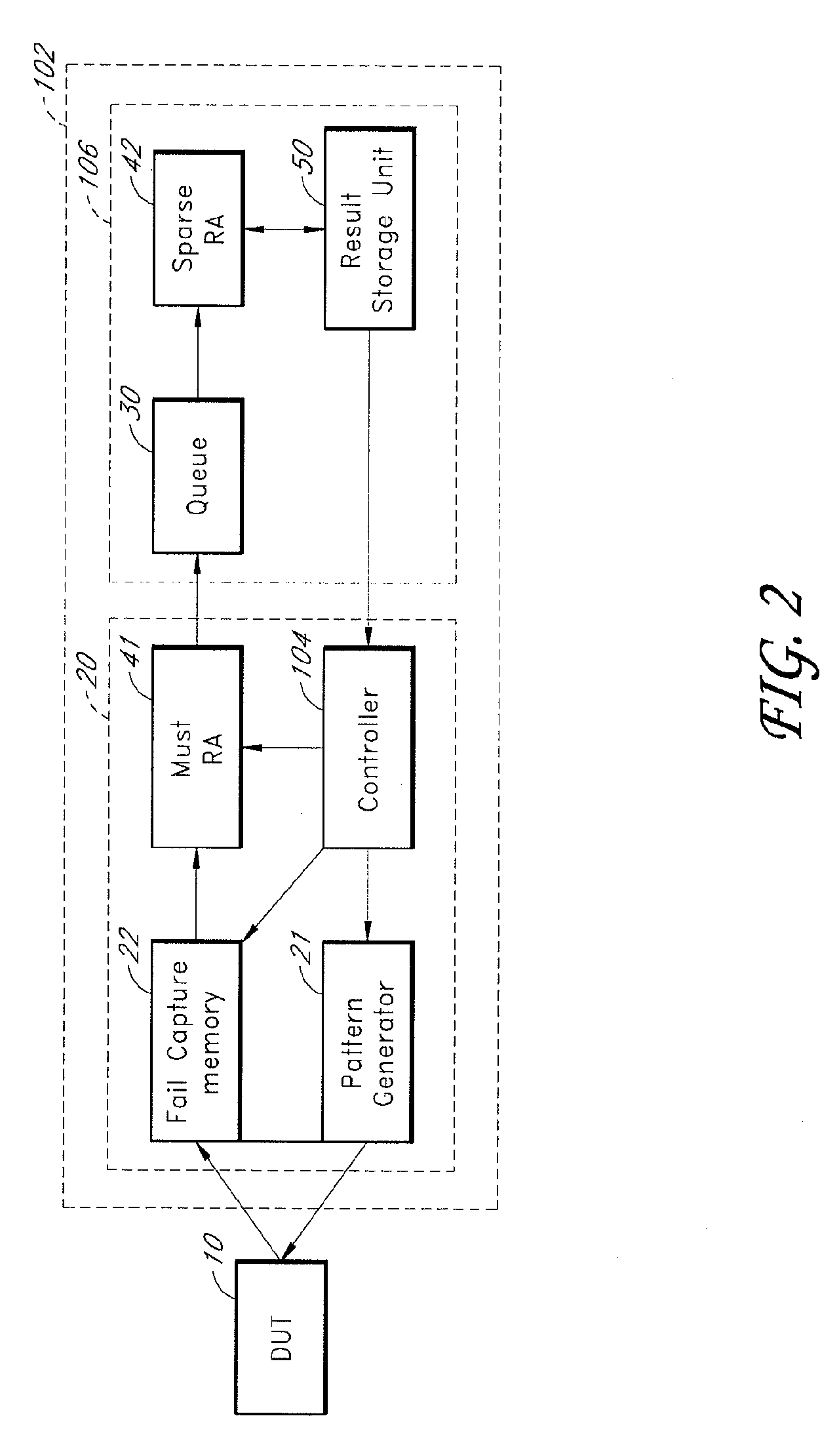

System and method for running test and redundancy analysis in parallel

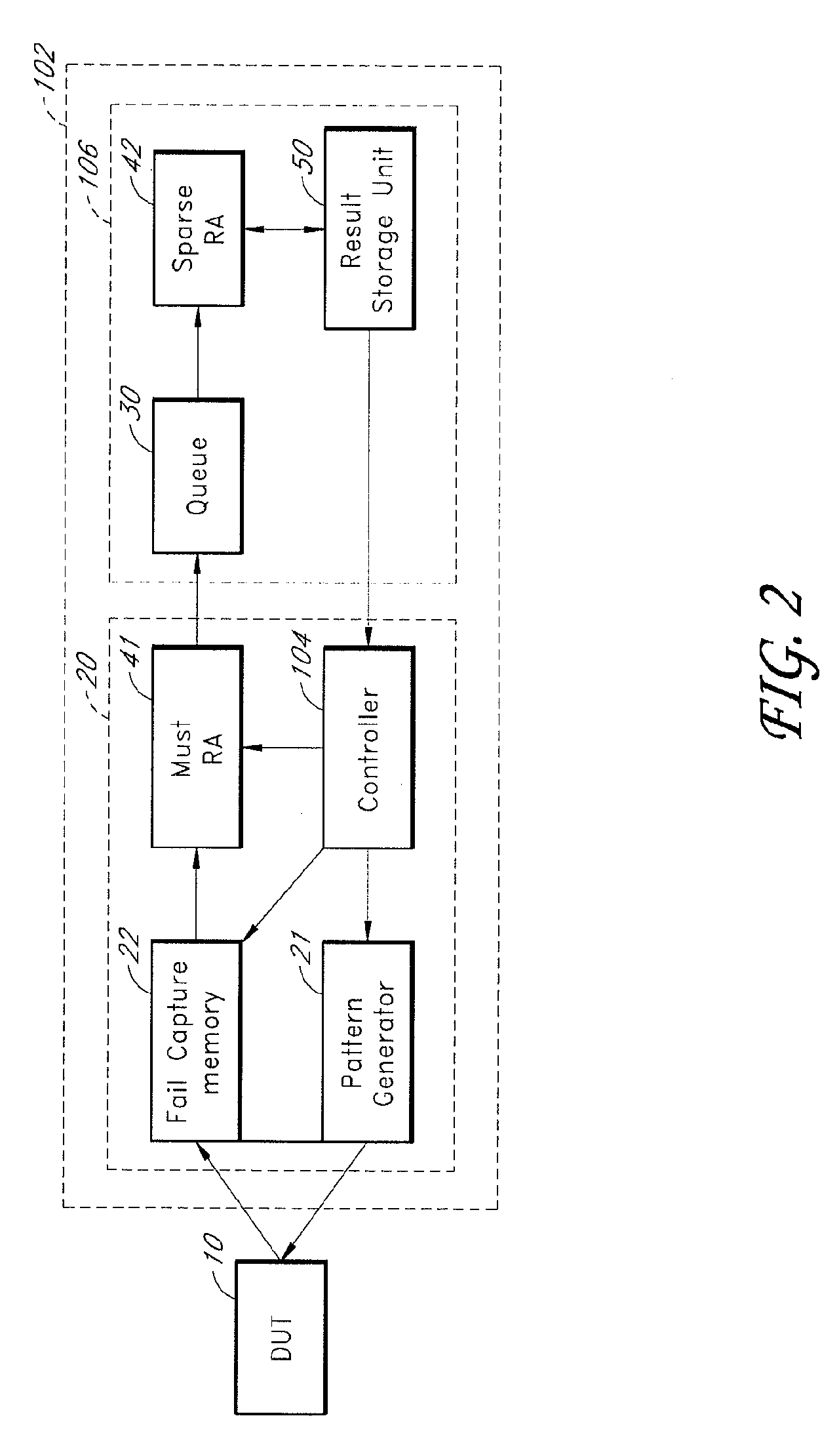

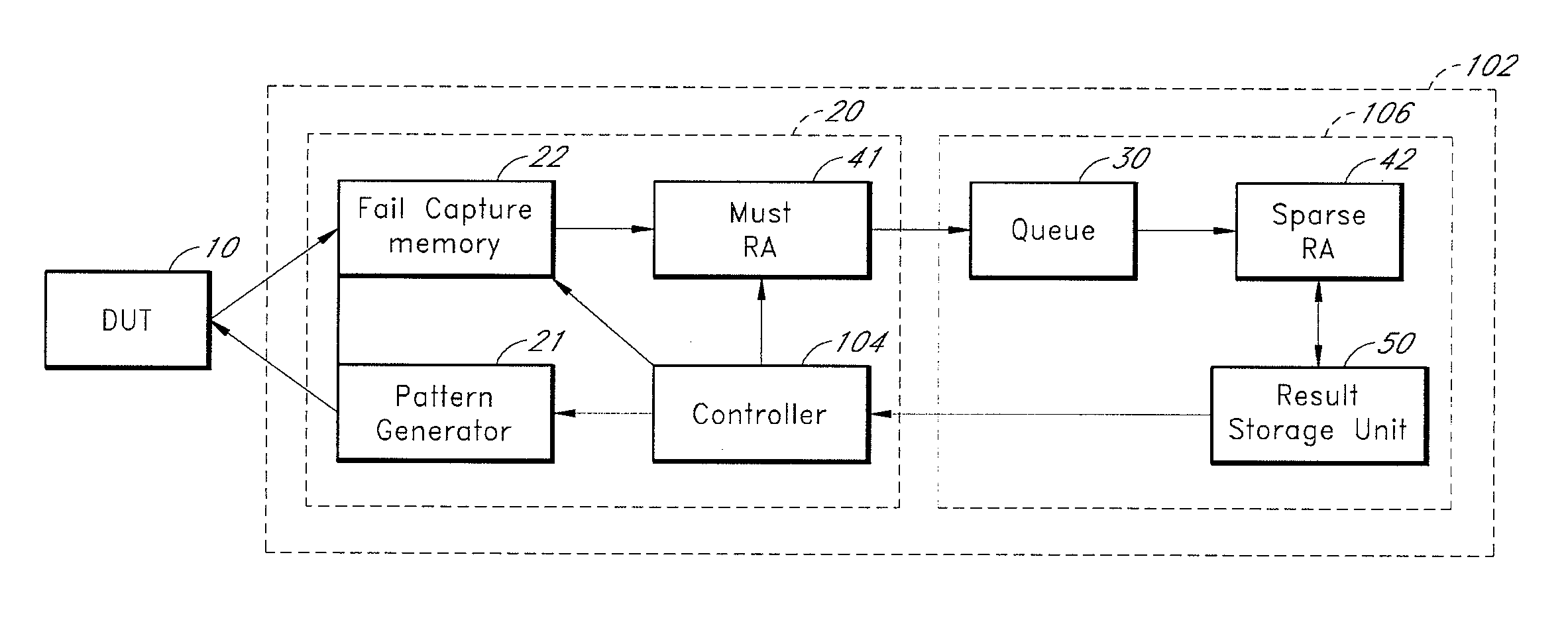

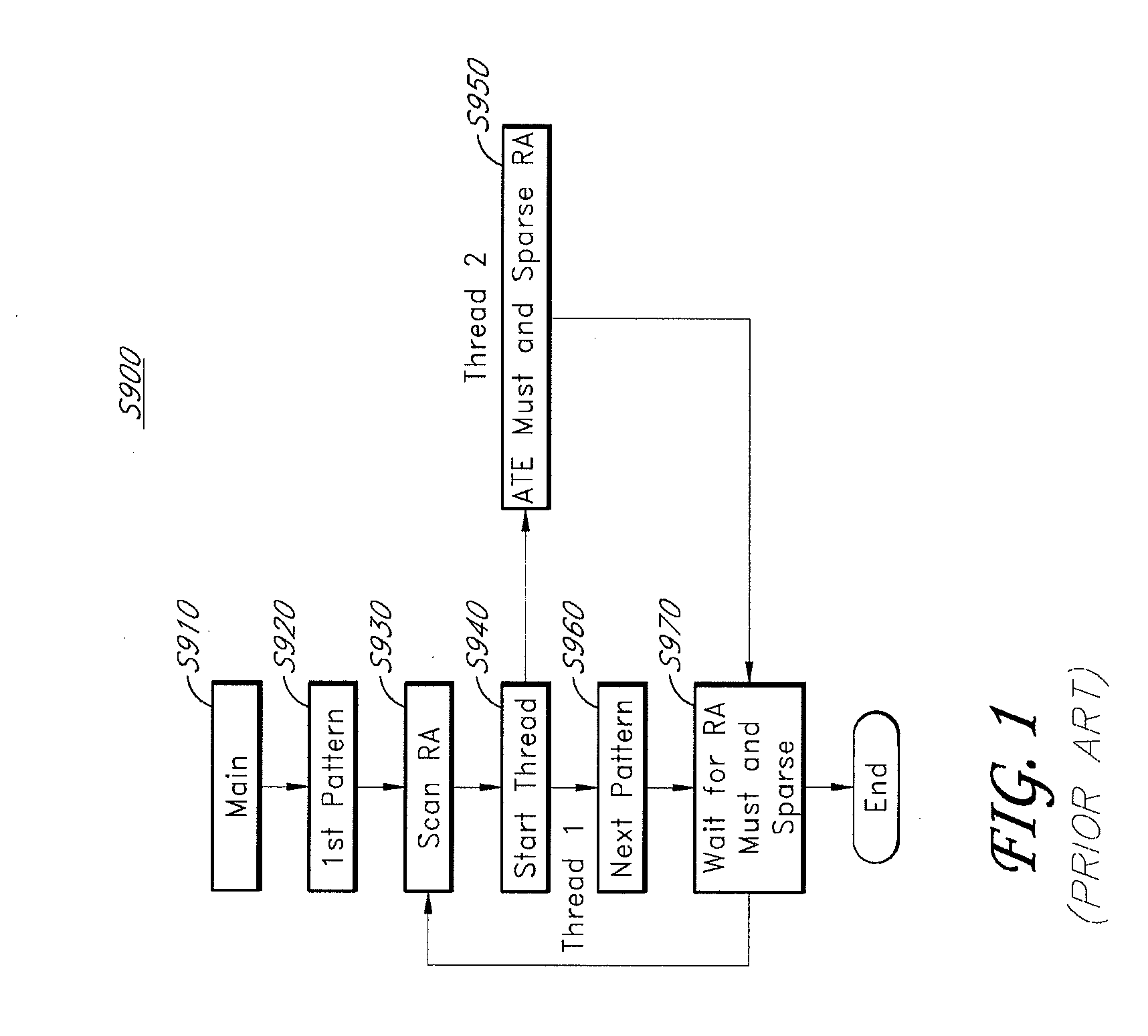

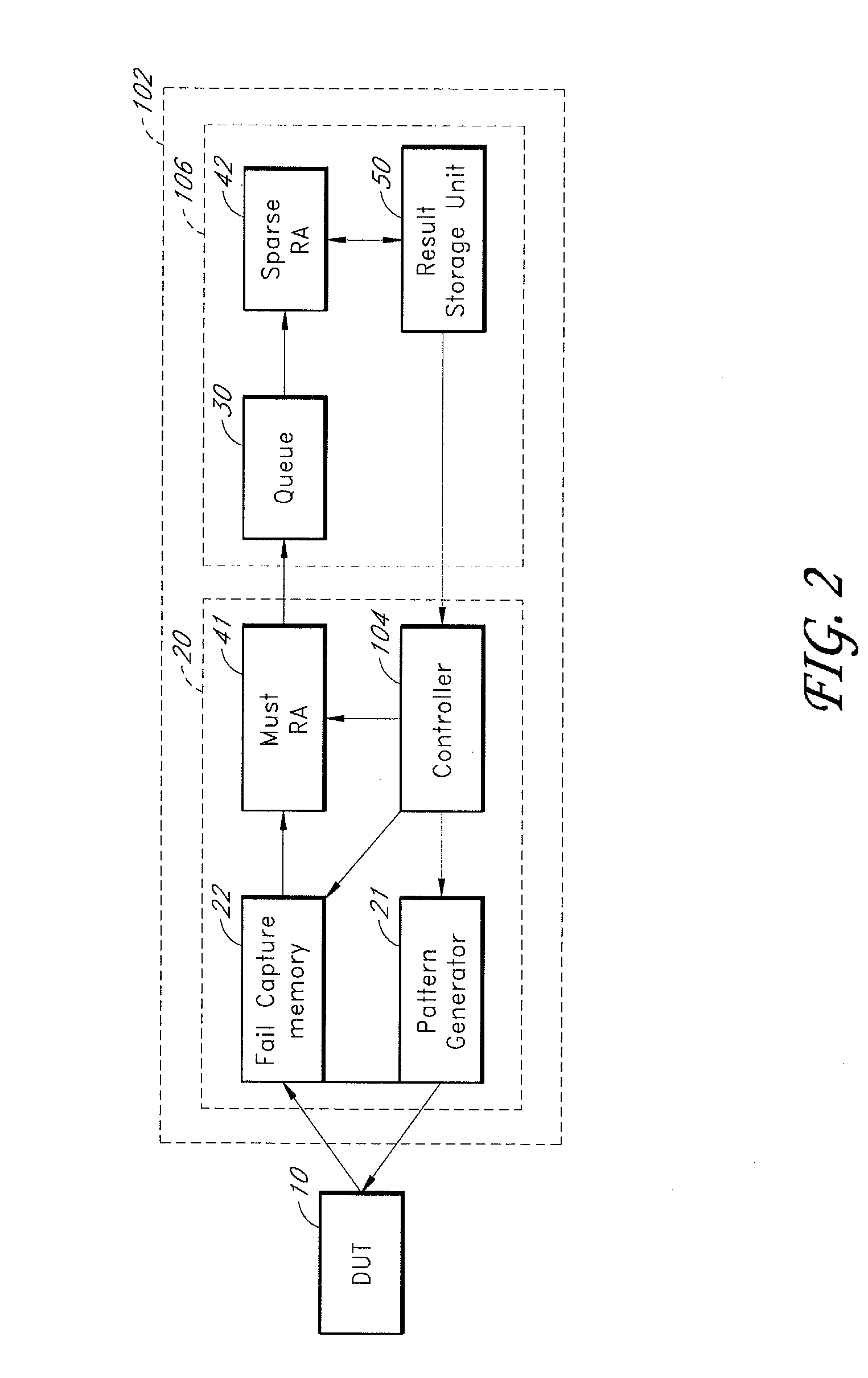

A memory redundancy analyzing apparatus having a tester, a queue, and a redundancy analyzer is provided. The tester includes testing portions for different types of fails, and each of the testing portions performs multiple tests on the memory locations and outputs fail information for at least a part of the memory device. The queue stores the fail information. The redundancy analyzer processes the fails using the fail information and produces a plurality of repair solutions. The types of fails include must fails and sparse fails. The fail information is transmitted to the queue, and the fail information includes at least a part of the fail information for the entire memory device. The tester can operate asynchronously from the redundancy analyzer.

Owner:MICRON TECH INC

Semiconductor memory cells with shared p-type well

A semiconductor integrated circuit with memory redundancy circuit to address the problems of increased area, power consumption and access time which is caused by using an ECC circuit for error correction. The circuit includes: a plurality of memory mats; a local bus, parallel to word lines, which transfers read data and write data from memory cells; a global bus for writing, parallel to data lines, which transfers write data from an input pad IO; a global bus for reading, parallel to data lines, which transfers read data to an output pad IO; and at least one error correction circuit located at an intersection of the global buses and the local bus. Reading and writing may each be completed in a single cycle, and during a write operation, data which is different from data previously read is written. By this configuration, an increase in area and power consumption can be avoided and errors such as soft errors can be corrected.

Owner:RENESAS ELECTRONICS CORP

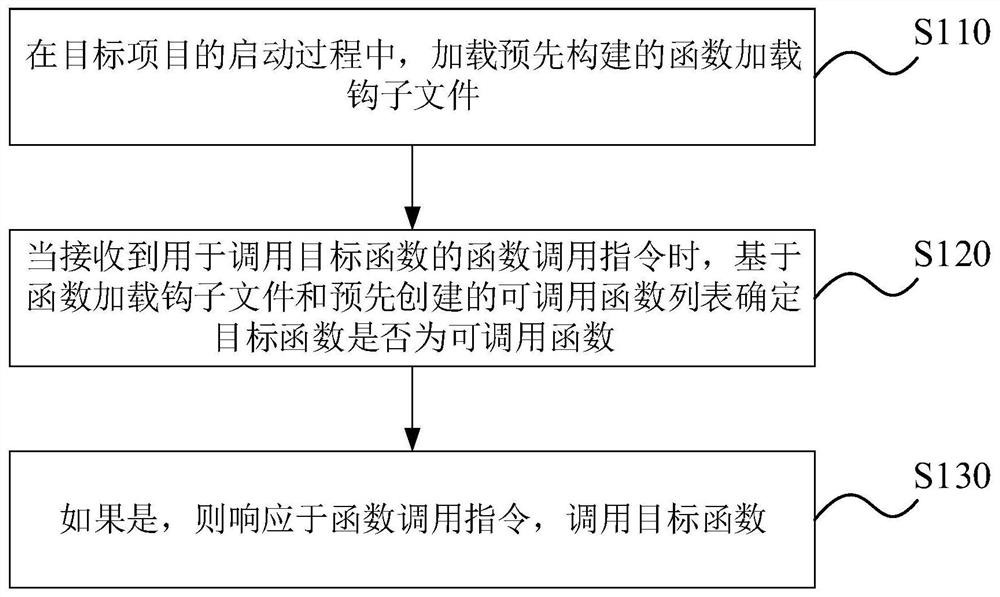

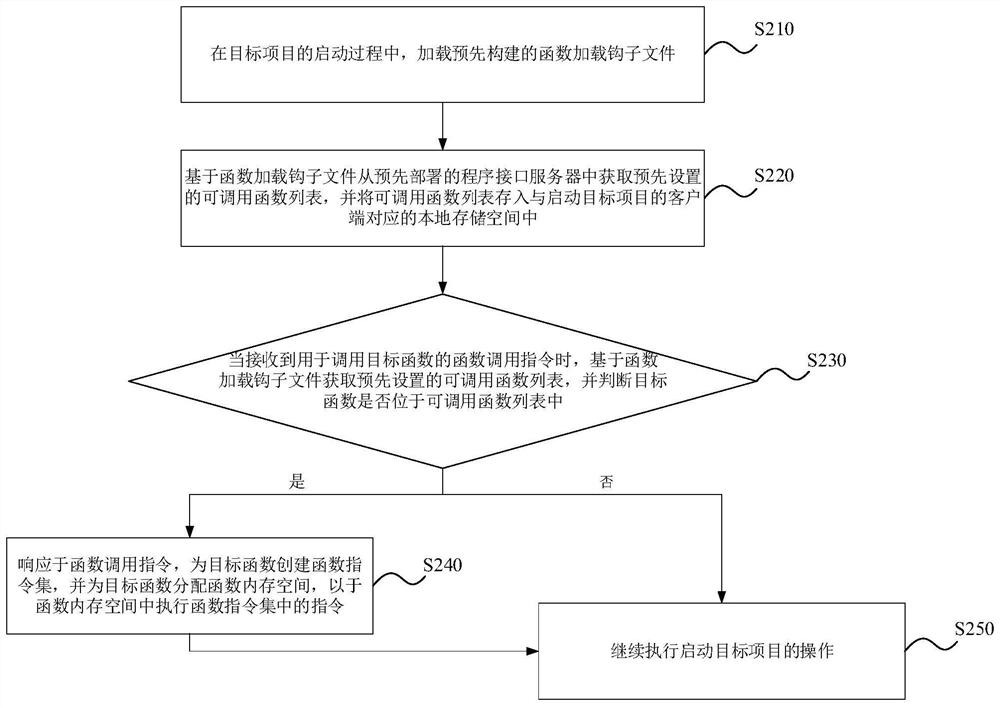

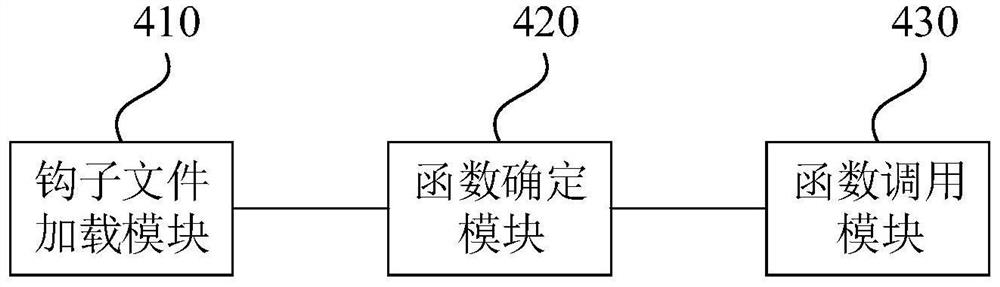

Function calling method and device, electronic equipment and storage medium

PendingCN113986402AOptimize the startup processImprove start-up efficiencyProgram loading/initiatingExecution paradigmsSoftware engineeringTerm memory

Embodiments of the invention disclose a function calling method and device, electronic equipment and a storage medium. The method comprises the following steps: loading a pre-constructed function loading hook file in a starting process of a target project; when a function calling instruction used for calling a target function is received, determining whether the target function is a callable function or not based on the function loading hook file and a pre-created callable function list; and if so, calling the target function in response to the function calling instruction. According to a technical scheme provided by the embodiments of the invention, the technical problems of memory redundancy, terminal jamming and the like caused by full-amount calling of the function can be avoided, and the effects of saving memory resources, improving project starting efficiency and improving user experience are achieved.

Owner:上海米哈游璃月科技有限公司

Memory redundancy programming

A method and apparatus is provided for performing a redundancy programming. The system of the present invention includes a device testing unit for performing a memory test. The system also includes a memory device operatively coupled to the device testing unit. The memory device includes an access transistor that includes a charge trapping area. A threshold voltage of the access transistor is modified upon trapping of charges in the charge trapping unit. The memory device also includes a memory element and a fuse associated with the memory element. The fuse is capable of entering an alternative state in response to modifying the threshold voltage of the access transistor. The state of the fuse may be used to program or de-program the memory element.

Owner:MICRON TECH INC

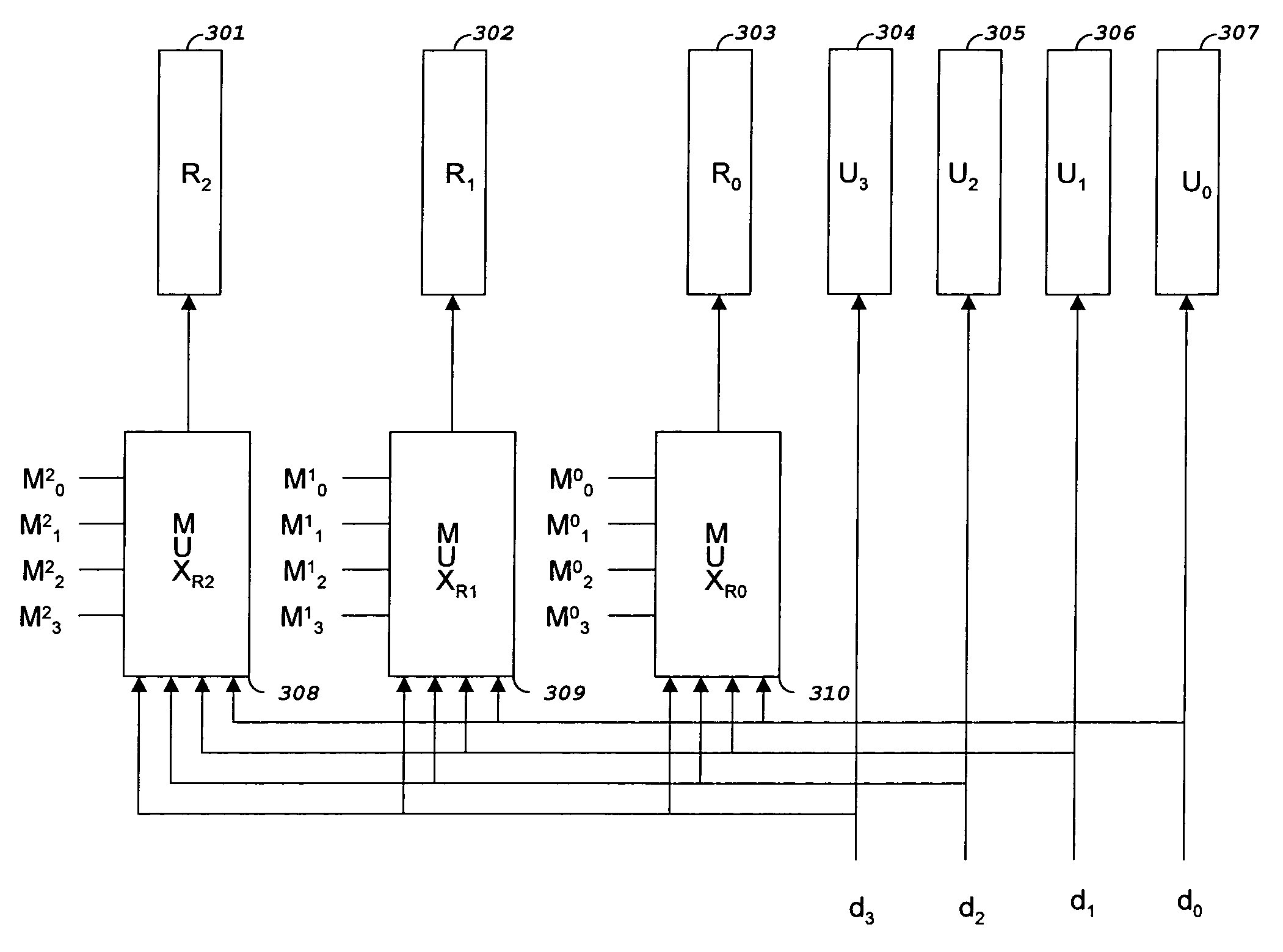

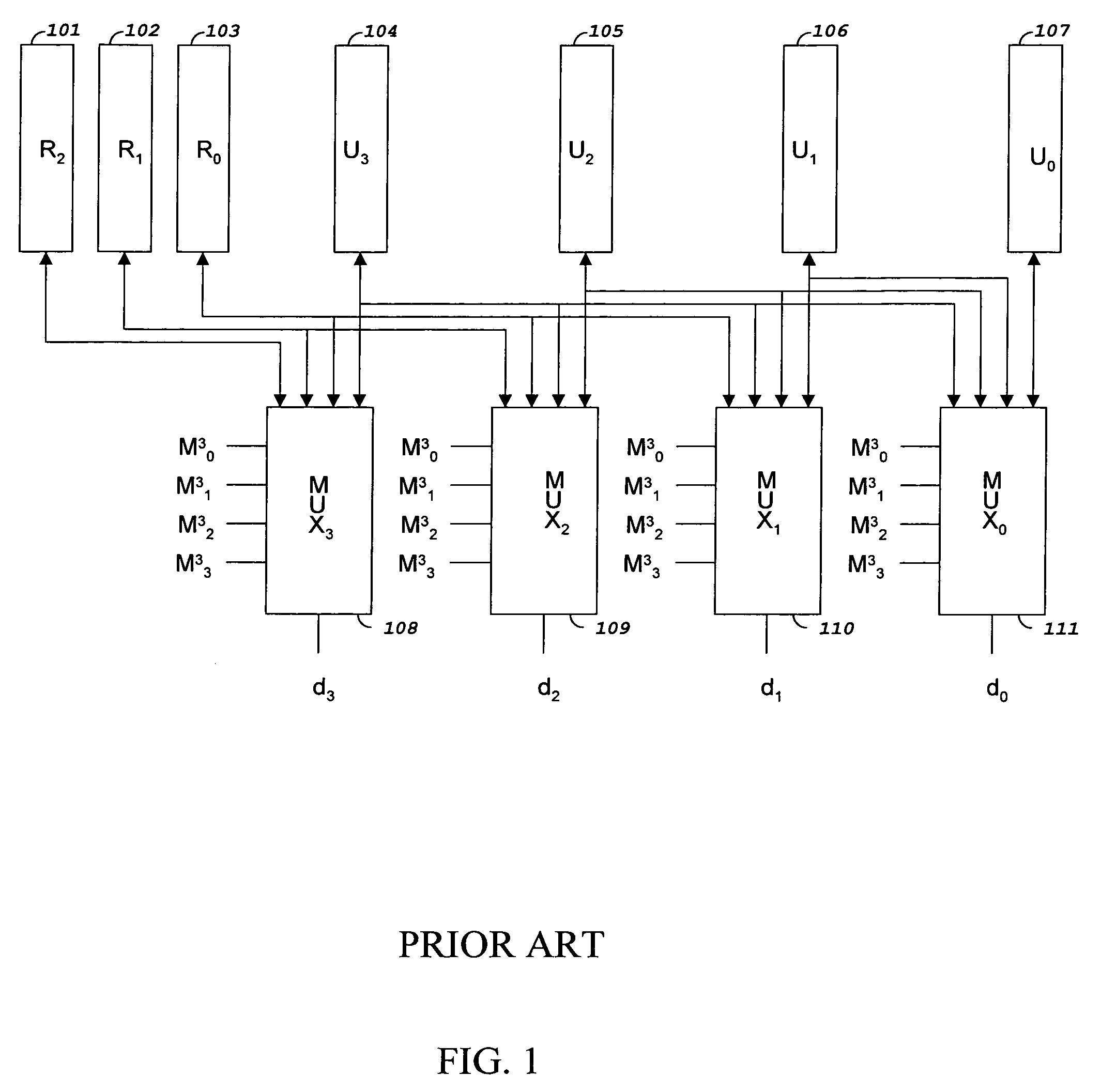

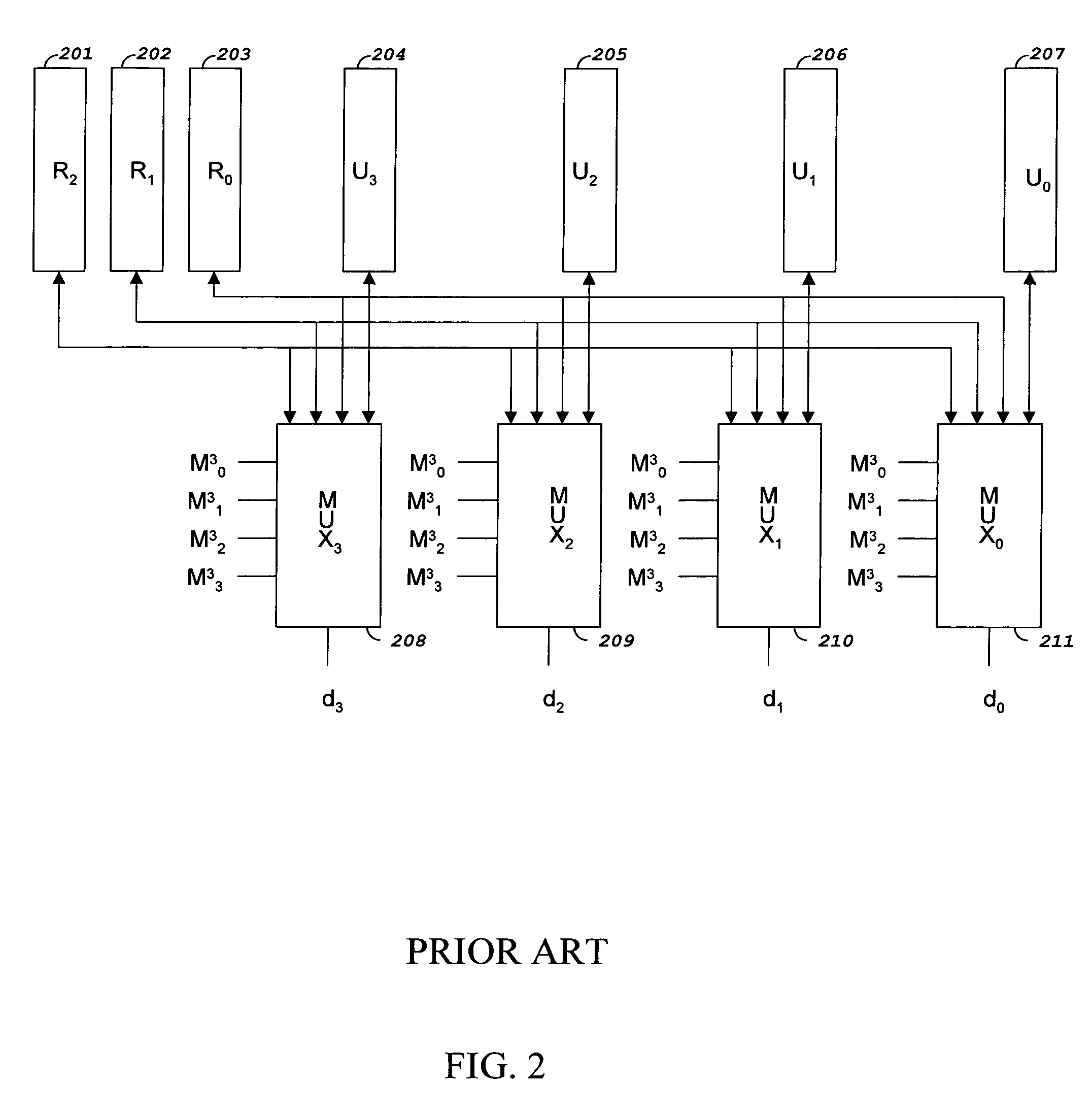

Apparatus for redundancy reconfiguration of faculty memories

A memory redundancy reconfiguration for N base blocks associated with k redundant blocks. The data will be written into both base blocks and defect-free redundant blocks if the base blocks are defective; k multiplexers MUXRi each having N input signals (d0 to dN−1) capable of being connected to k input signals of the redundant blocks; N multiplexers MUXi each having k+1 input signals from k redundant blocks (R0 to Rk−1) and one base block (Ni), capable of being connected to N output signals (qi); and logic means associated with each multiplexer, to convert the input signals of the multiplexer to its output signal.

Owner:SYNTEST TECH

System and method for running test and redundancy analysis in parallel

ActiveUS20090265588A1Static storageRedundant hardware error correctionAsynchronous operationComputer science

A memory redundancy analyzing apparatus having a tester, a queue, and a redundancy analyzer is provided. The tester includes testing portions for different types of fails, and each of the testing portions performs multiple tests on the memory locations and outputs fail information for at least a part of the memory device. The queue stores the fail information. The redundancy analyzer processes the fails using the fail information and produces a plurality of repair solutions. The types of fails include must fails and sparse fails. The fail information is transmitted to the queue, and the fail information includes at least a part of the fail information for the entire memory device. The tester can operate asynchronously from the redundancy analyzer.

Owner:MICRON TECH INC