Patents

Literature

336 results about "Programmable circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

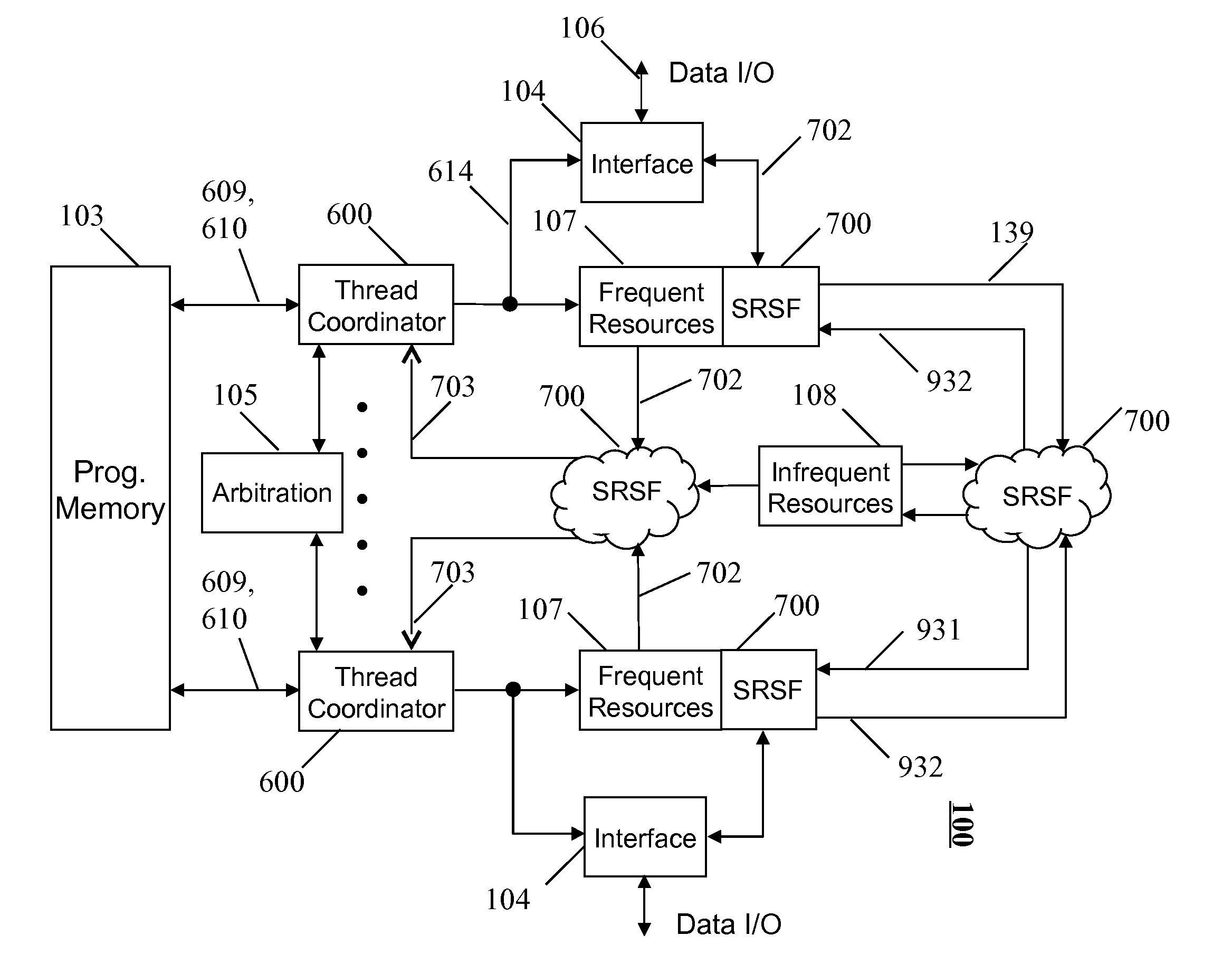

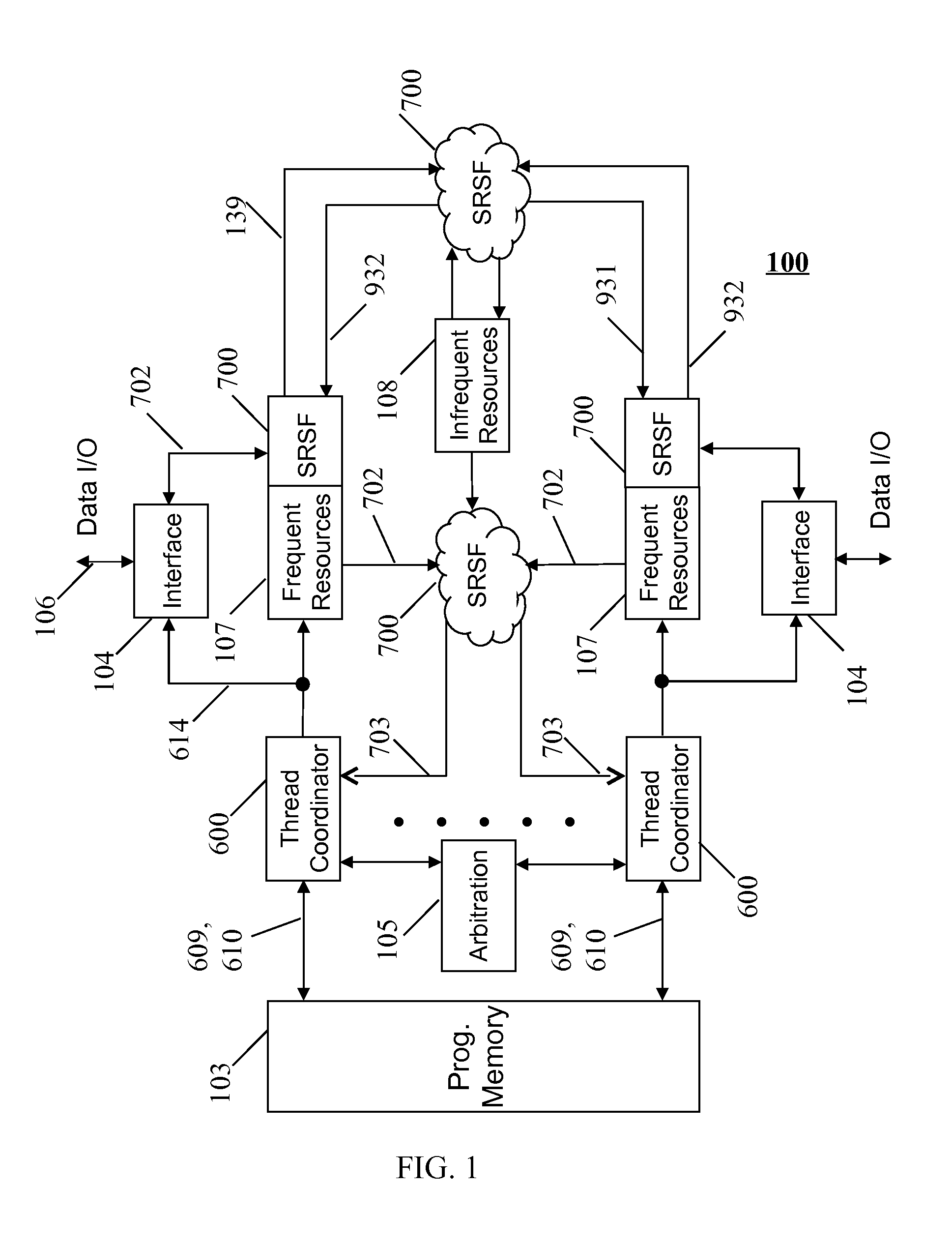

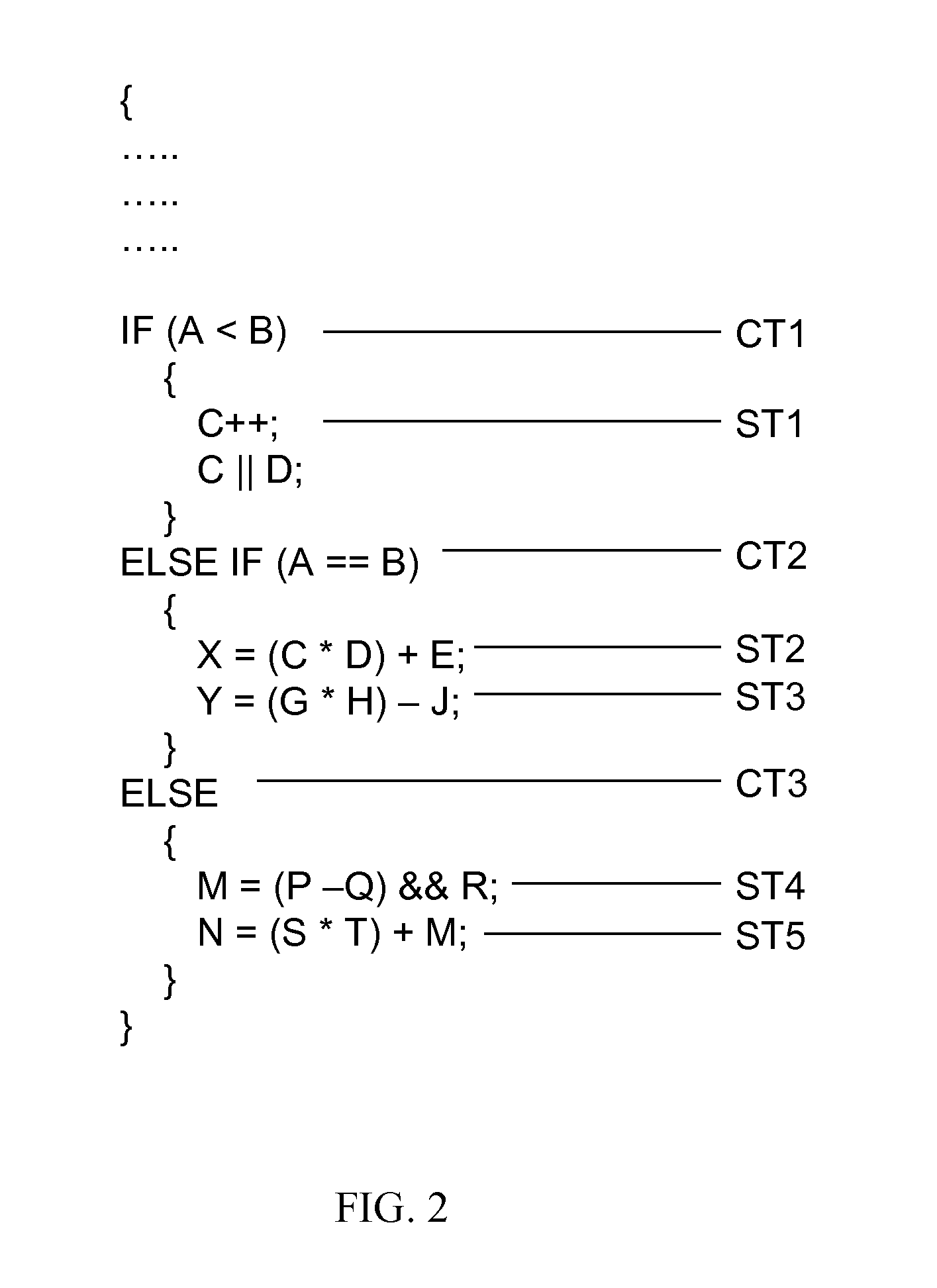

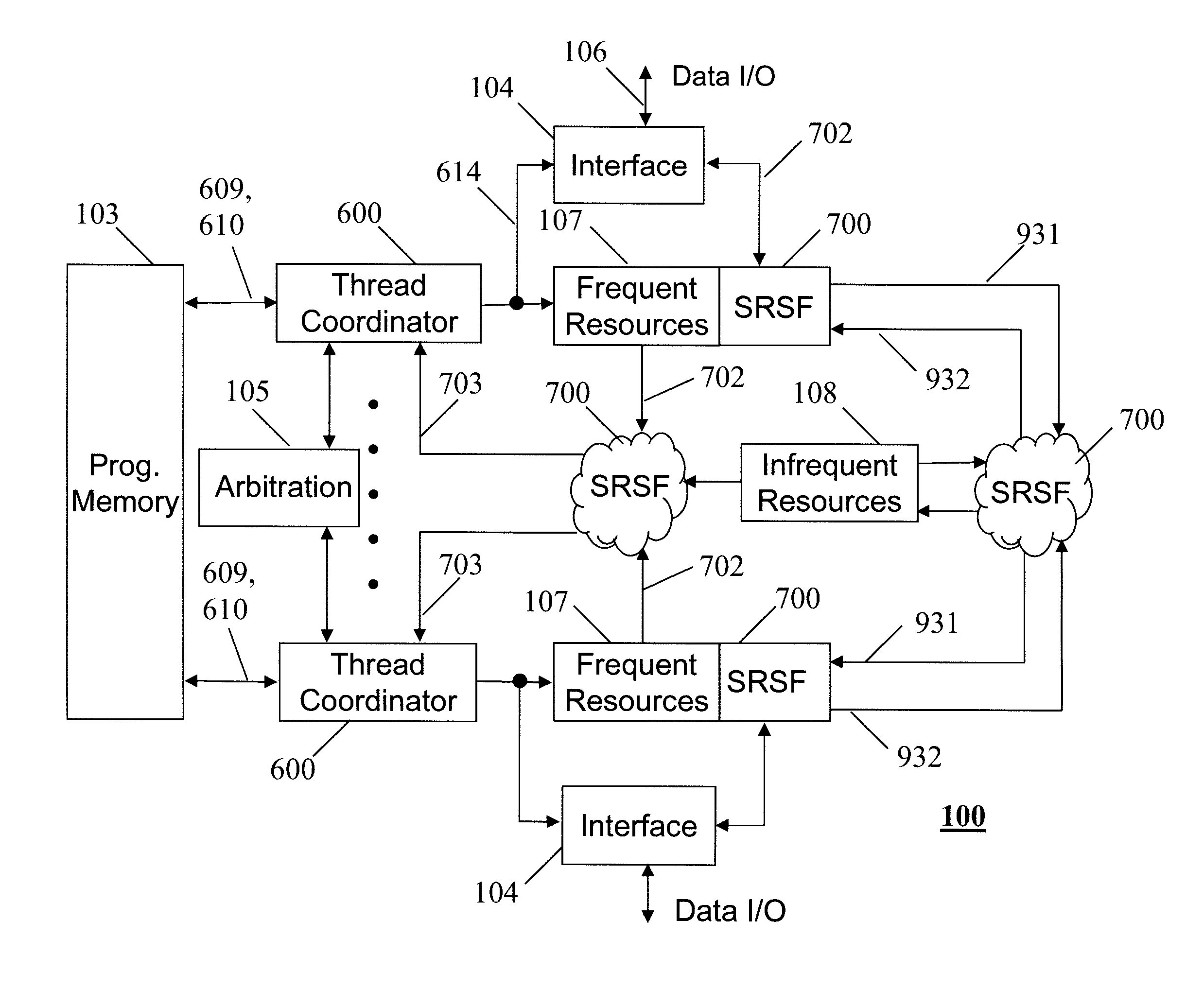

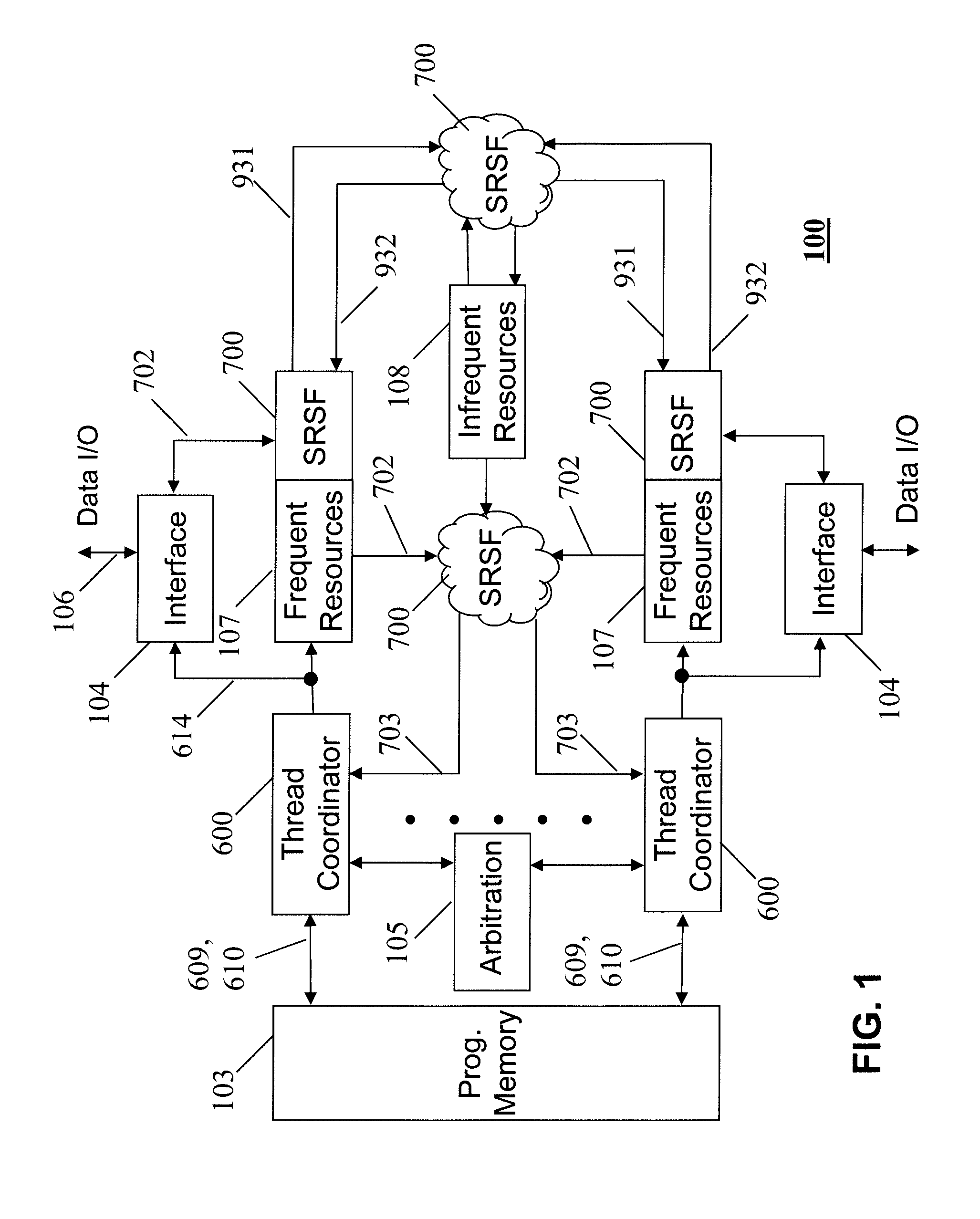

Shared resource multi-thread processor array

ActiveUS20120089812A1Dataflow computersProgram initiation/switchingProgrammable circuitsSwitched fabric

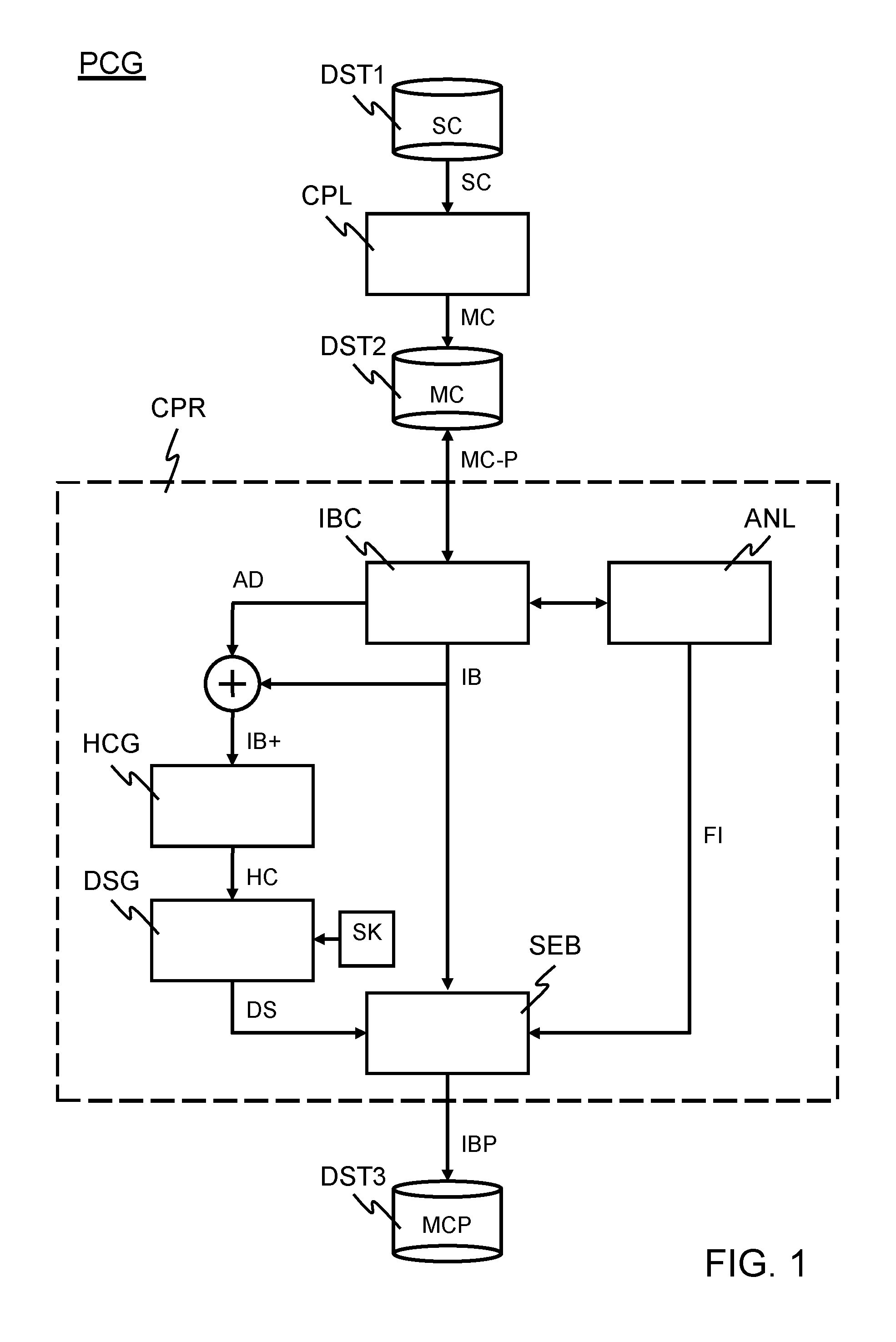

A shared resource multi-thread processor array wherein an array of heterogeneous function blocks are interconnected via a self-routing switch fabric, in which the individual function blocks have an associated switch port address. Each switch output port comprises a FIFO style memory that implements a plurality of separate queues. Thread queue empty flags are grouped using programmable circuit means to form self-synchronised threads. Data from different threads are passed to the various addressable function blocks in a predefined sequence in order to implement the desired function. The separate port queues allows data from different threads to share the same hardware resources and the reconfiguration of switch fabric addresses further enables the formation of different data-paths allowing the array to be configured for use in various applications.

Owner:SMITH GRAEME ROY

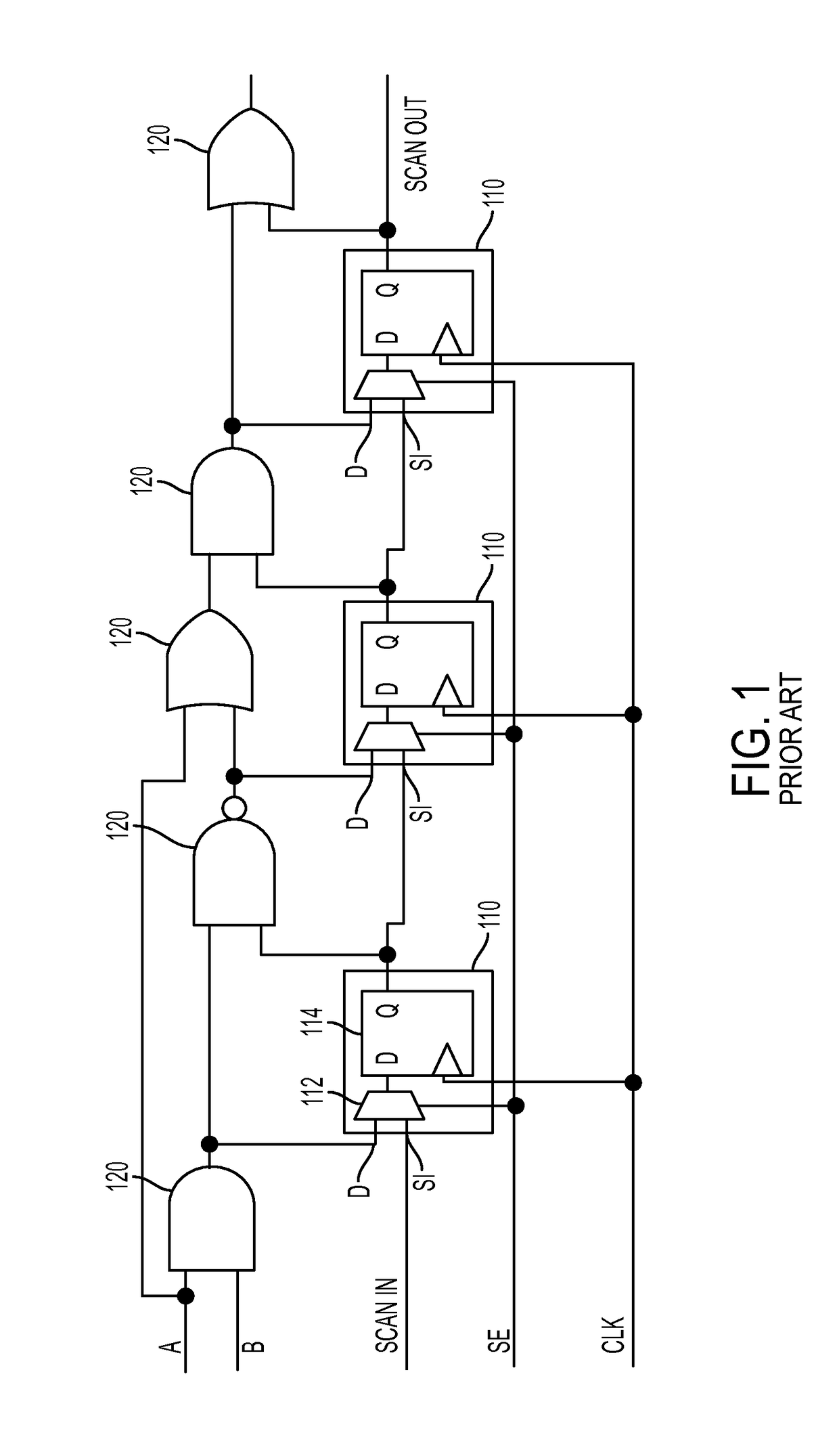

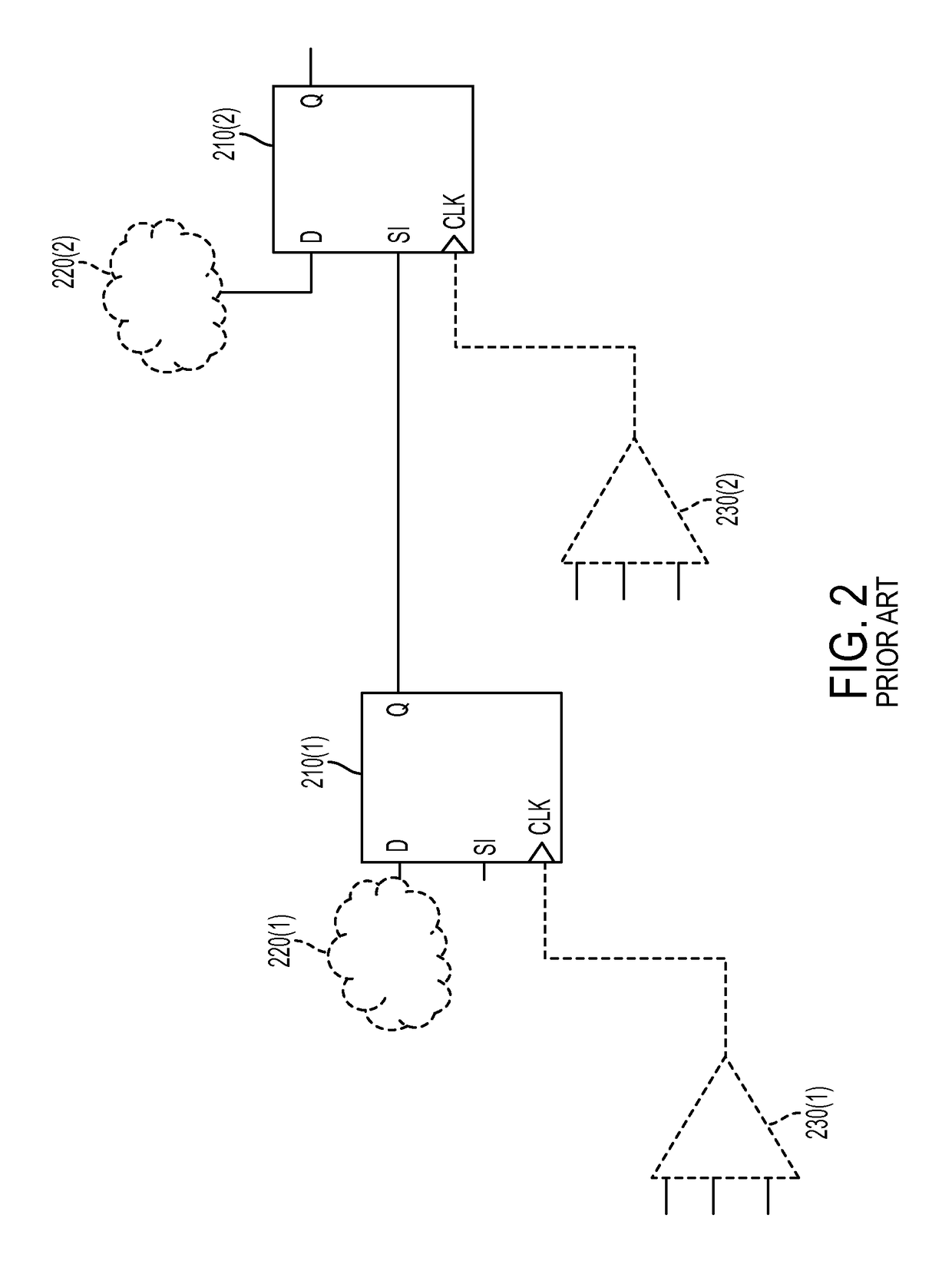

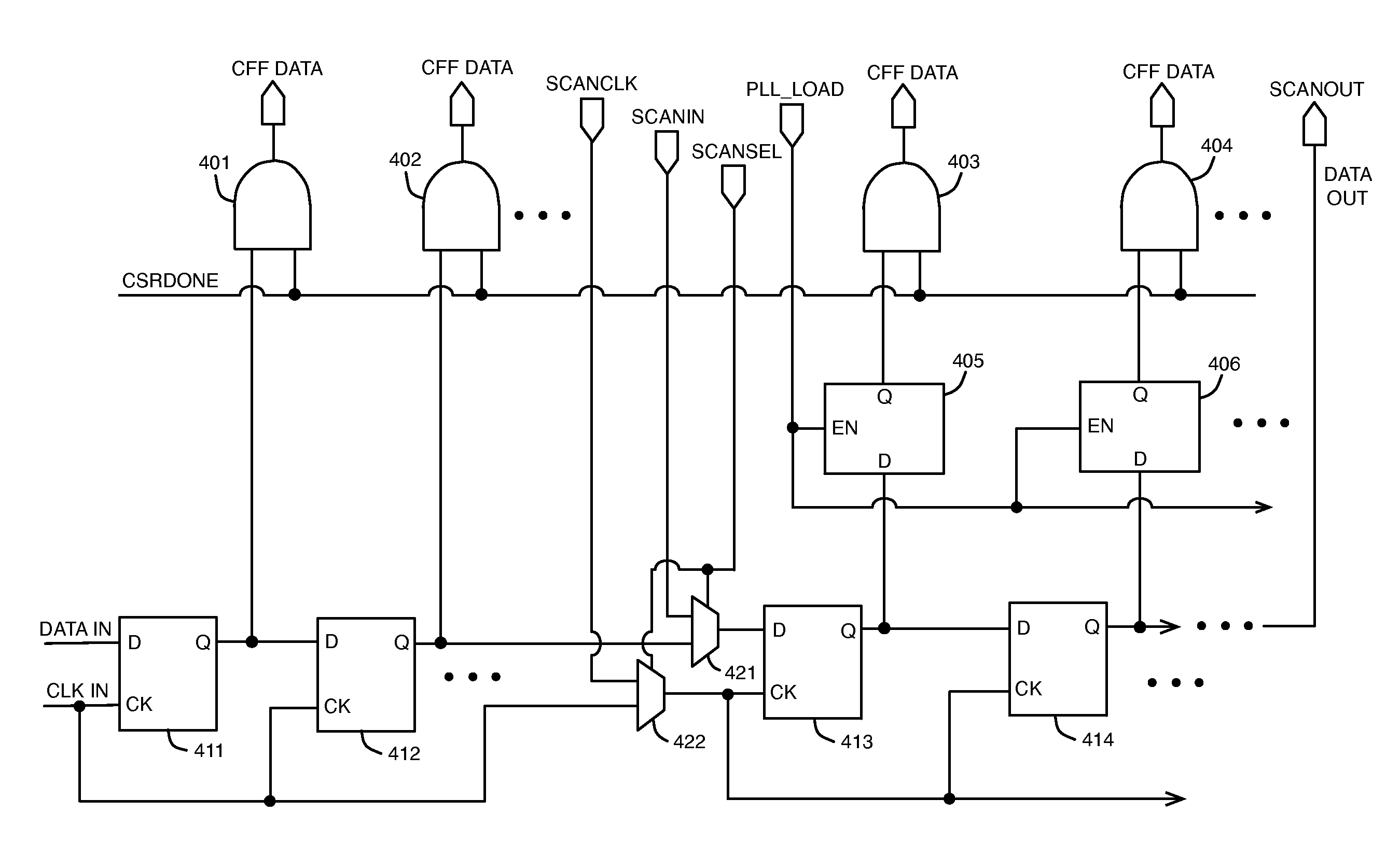

Programmable circuits for correcting scan-test circuitry defects in integrated circuit designs

ActiveUS9618579B2Digital circuit testingDetecting faulty computer hardwareComputer hardwareComputer architecture

In certain embodiments, an integrated circuit has scan-test circuitry that performs scan testing on circuitry under scan test (CUST) within the IC, where the scan-test circuitry is susceptible to a defect. In order to enable the defect to be corrected after it occurs, the scan-test circuitry includes a set of programmable circuitry connected to provide a signal to other circuitry (e.g., a scan chain) within the scan-test circuitry, where the set of programmable circuitry includes one or more configurable memory cells connected to control the programming of the set of programmable circuitry. The memory cell(s) can be configured to program the set of programmable circuitry to enable the scan testing to be performed without modification. The memory cell(s) can also be configured to program the set of programmable circuitry to modify the scan testing to correct the defect in the scan-test circuitry.

Owner:LATTICE SEMICON CORP

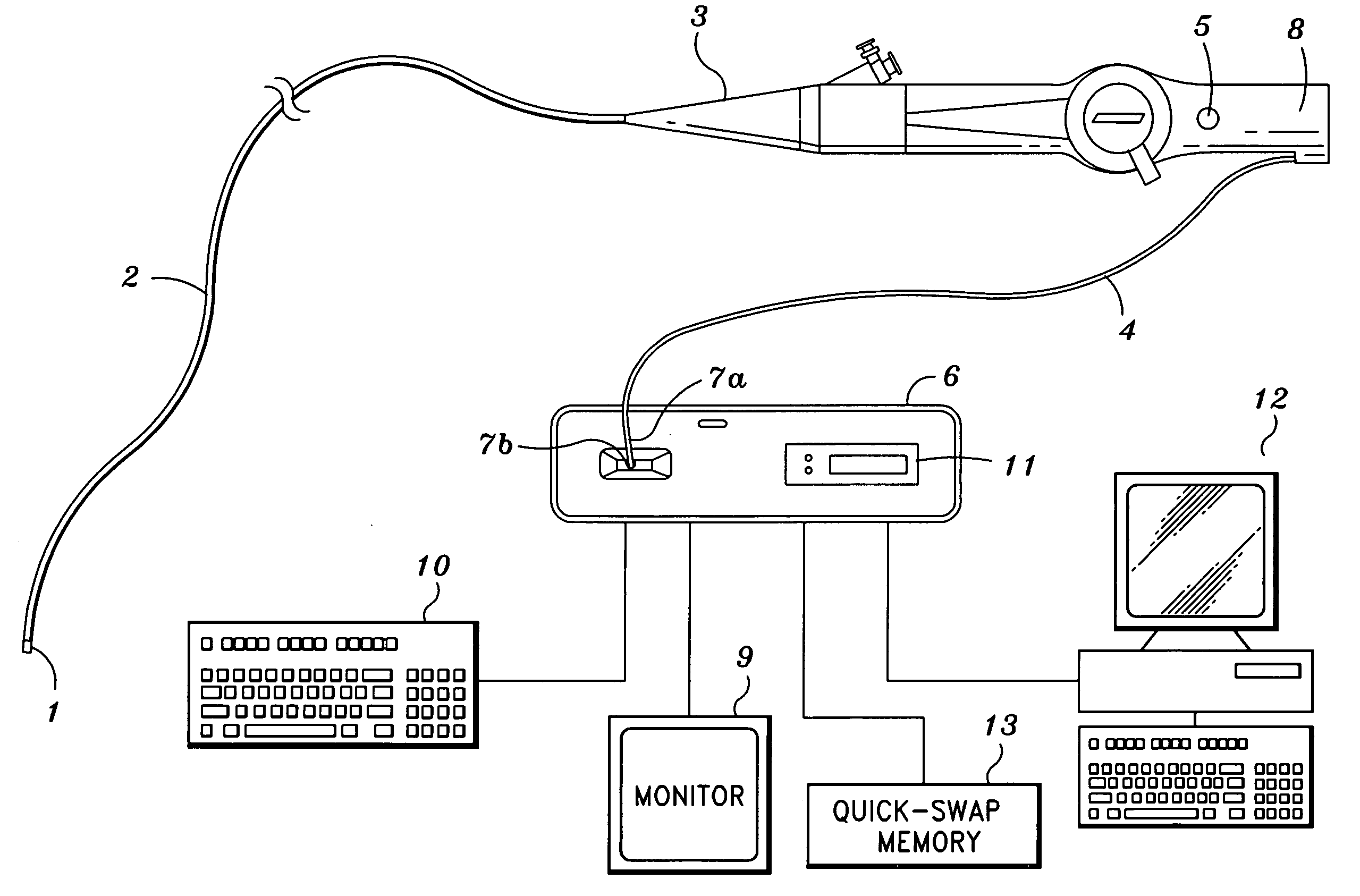

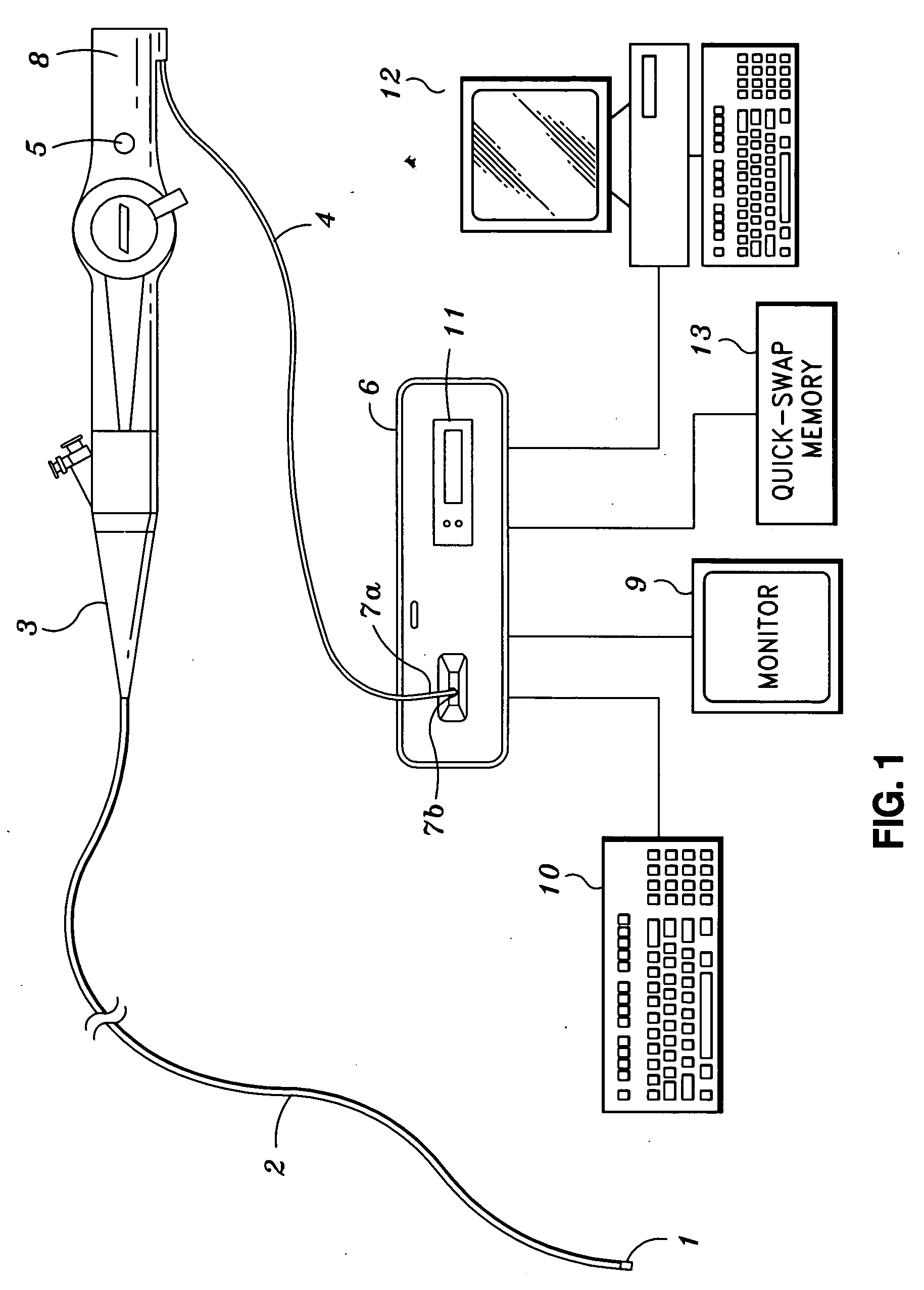

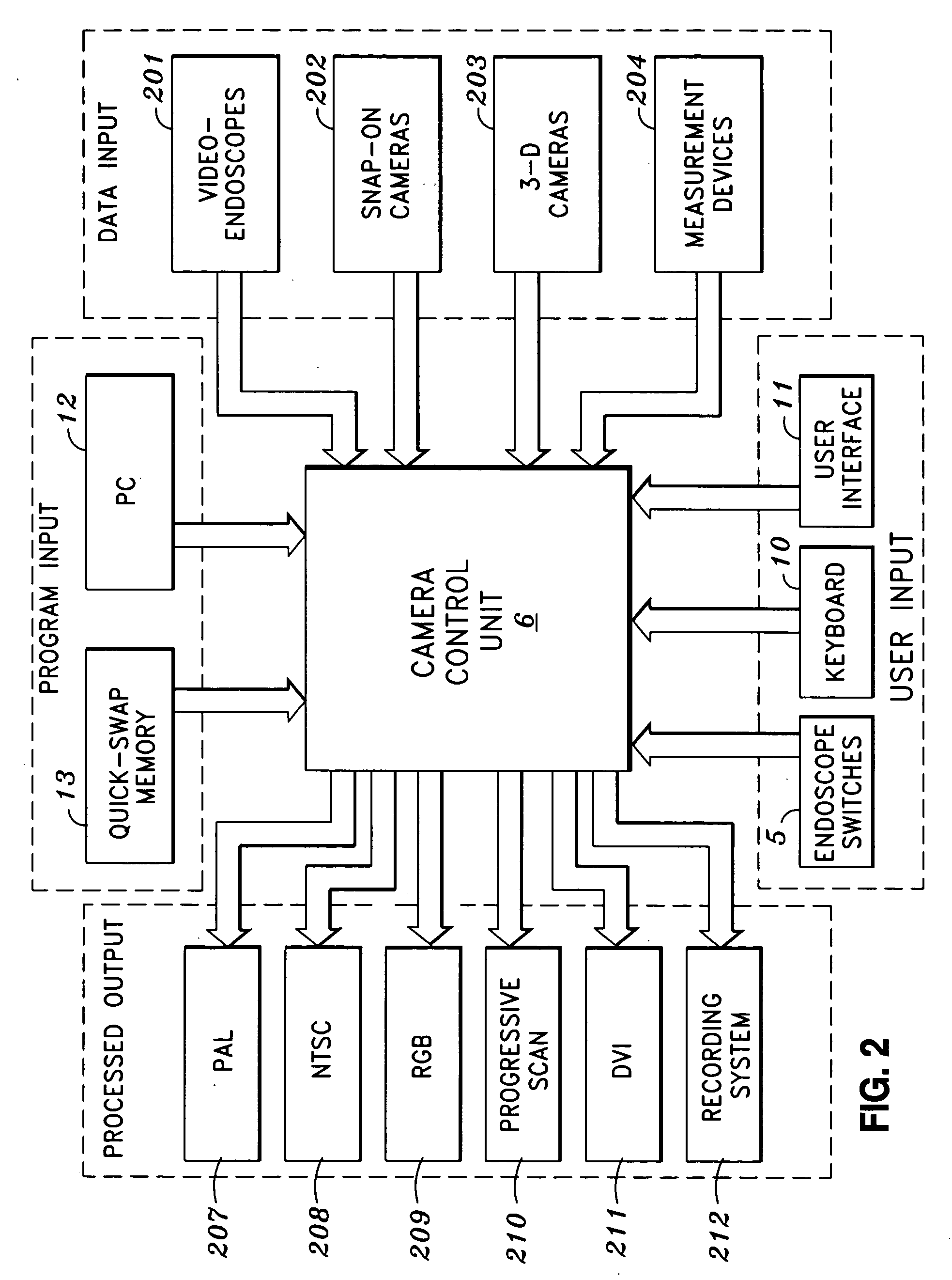

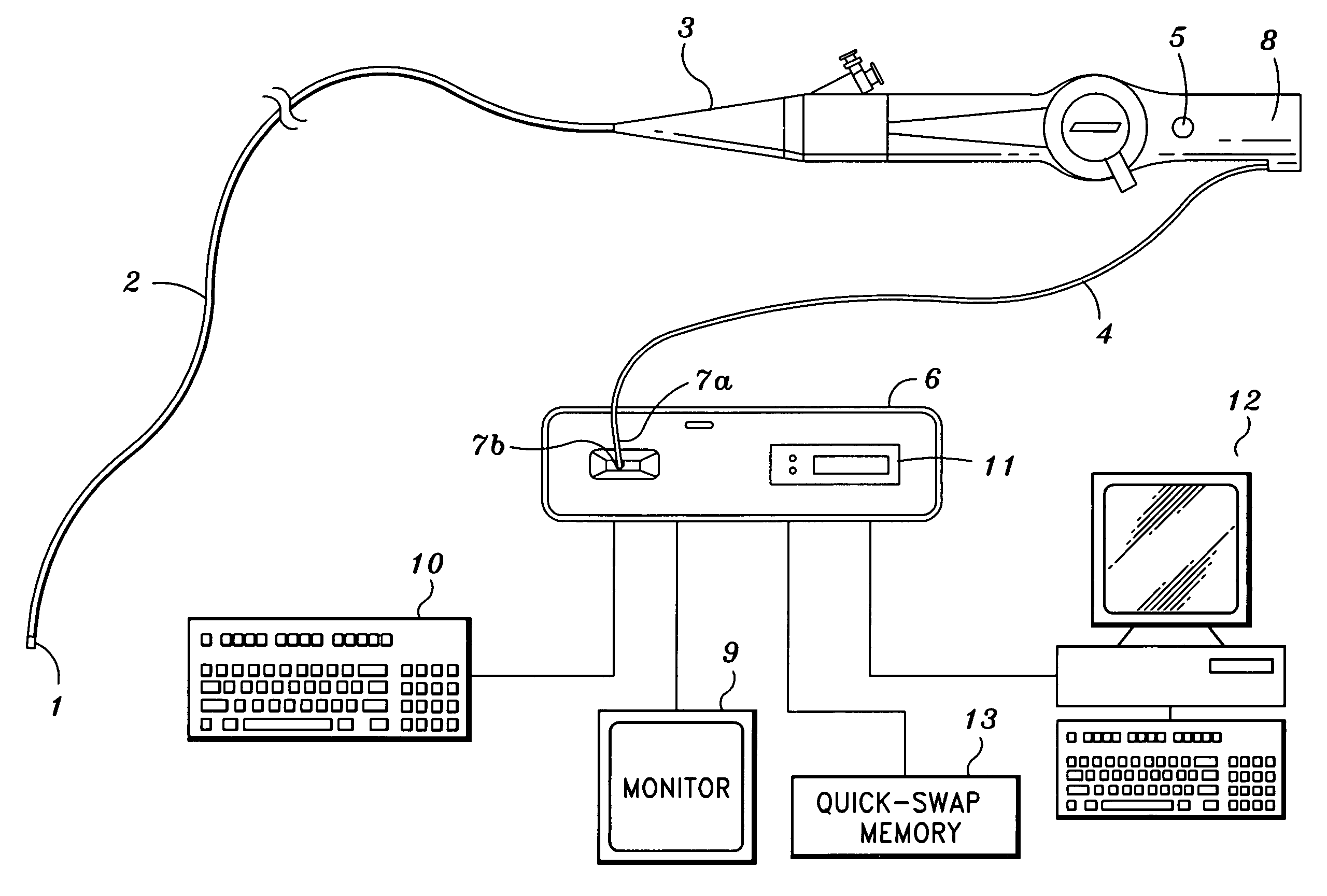

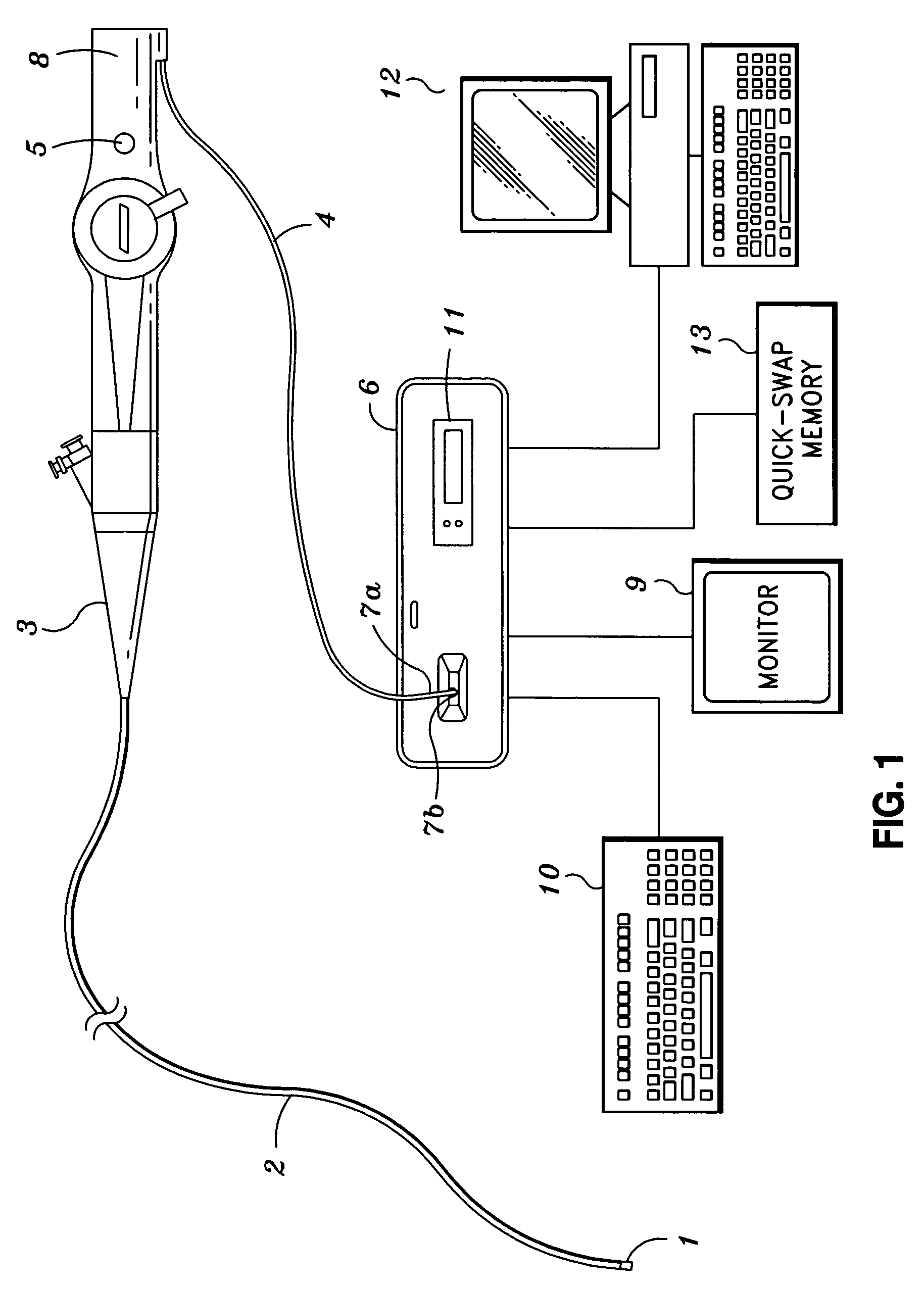

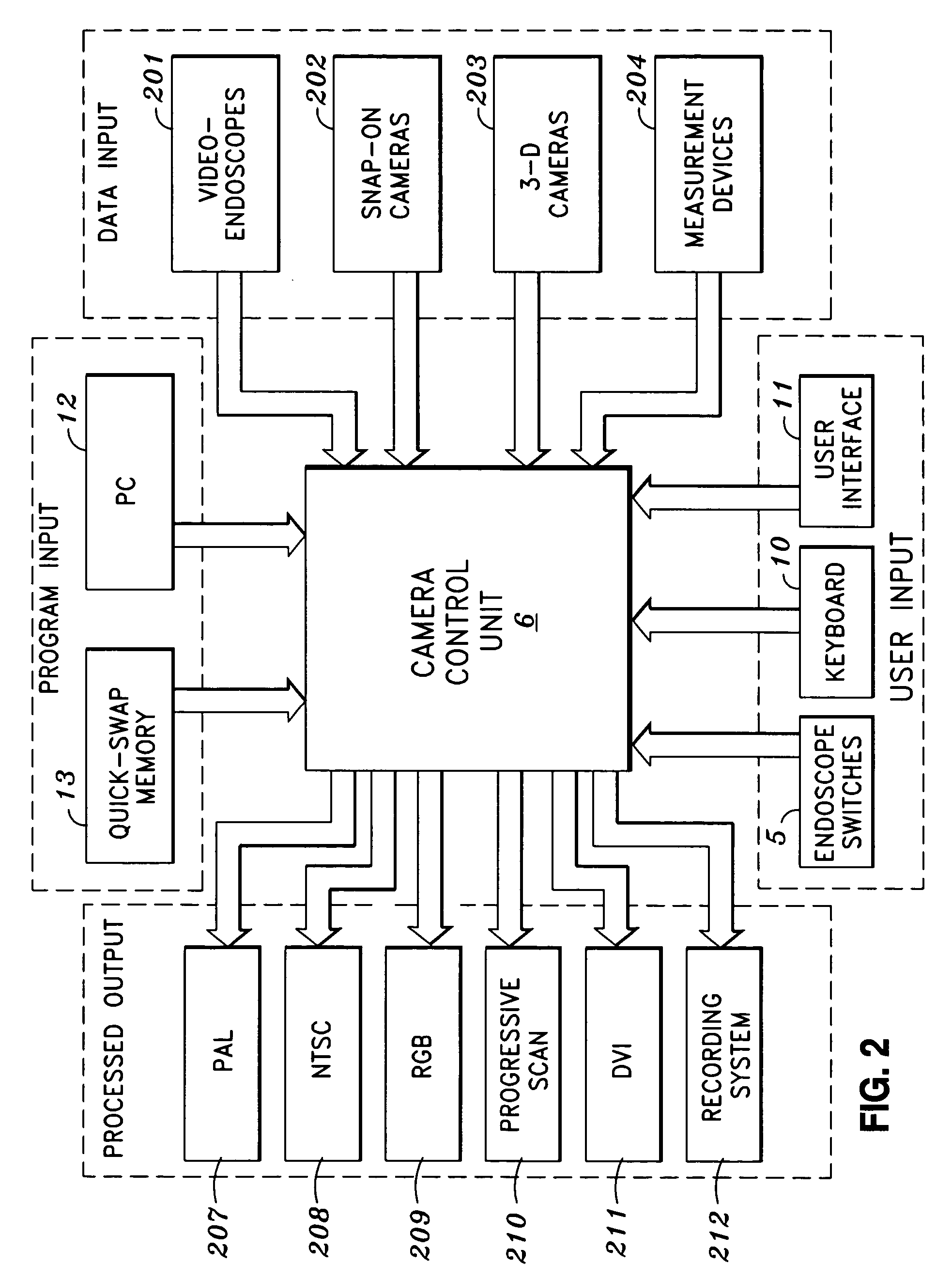

Endoscopy device supporting multiple input devices

The present invention provides a remote-head imaging system with a camera control unit capable of supporting multiple input devices. The camera control unit detects an input device to which it is connected and changes the camera control unit's internal functionality accordingly. Such changes includes altering clock timing, changing video output parameters, and changing image processing software. In addition, a user is able to select different sets of software program instructions and hardware configuration information based on the head that is attached. The remote-head imaging system utilizes field-programmable circuitry, such as field-programmable gate arrays (FPGA), in order to facilitate the change in configuration.

Owner:GYRUS ACMI INC (D B A OLYMPUS SURGICAL TECH AMERICA)

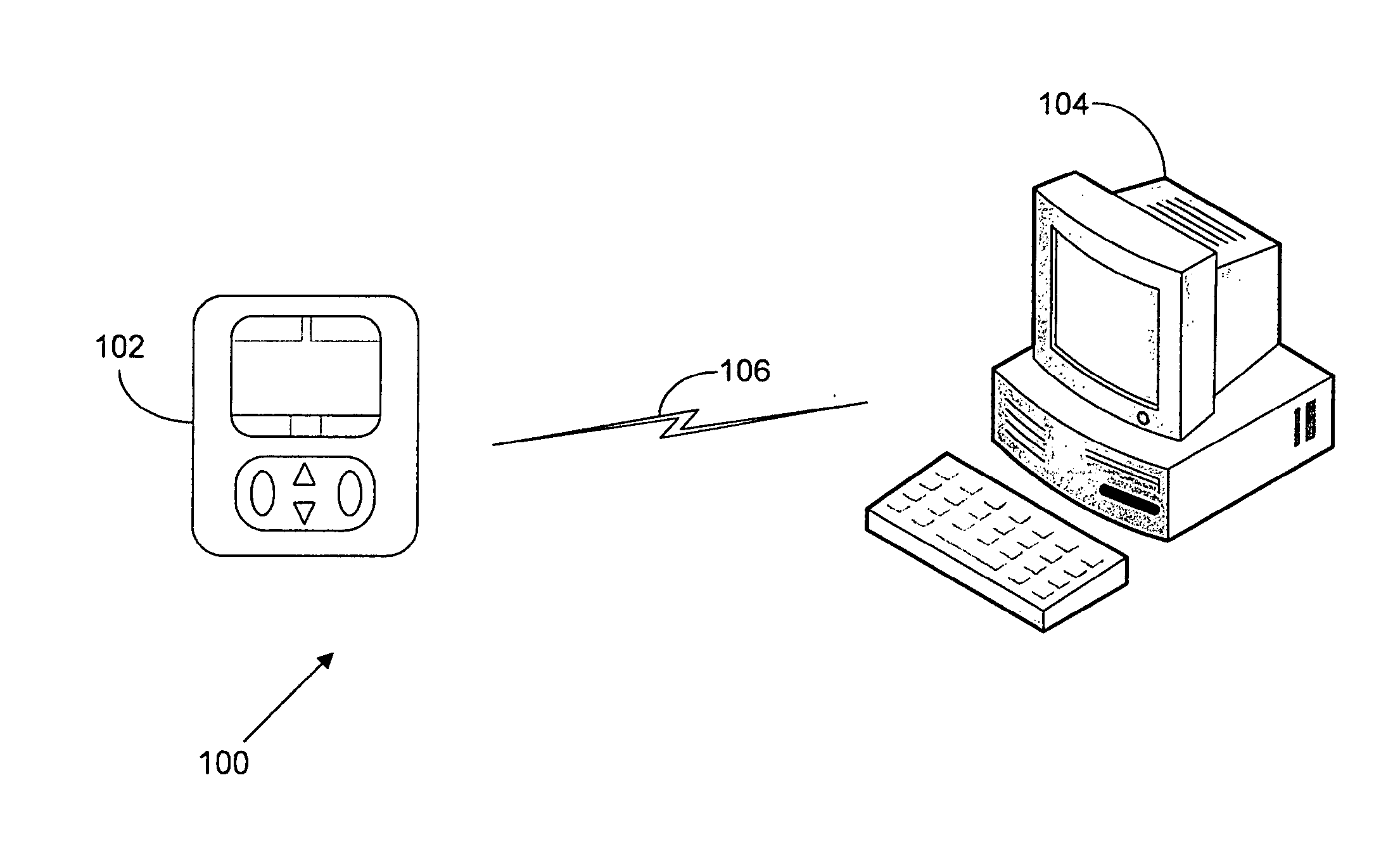

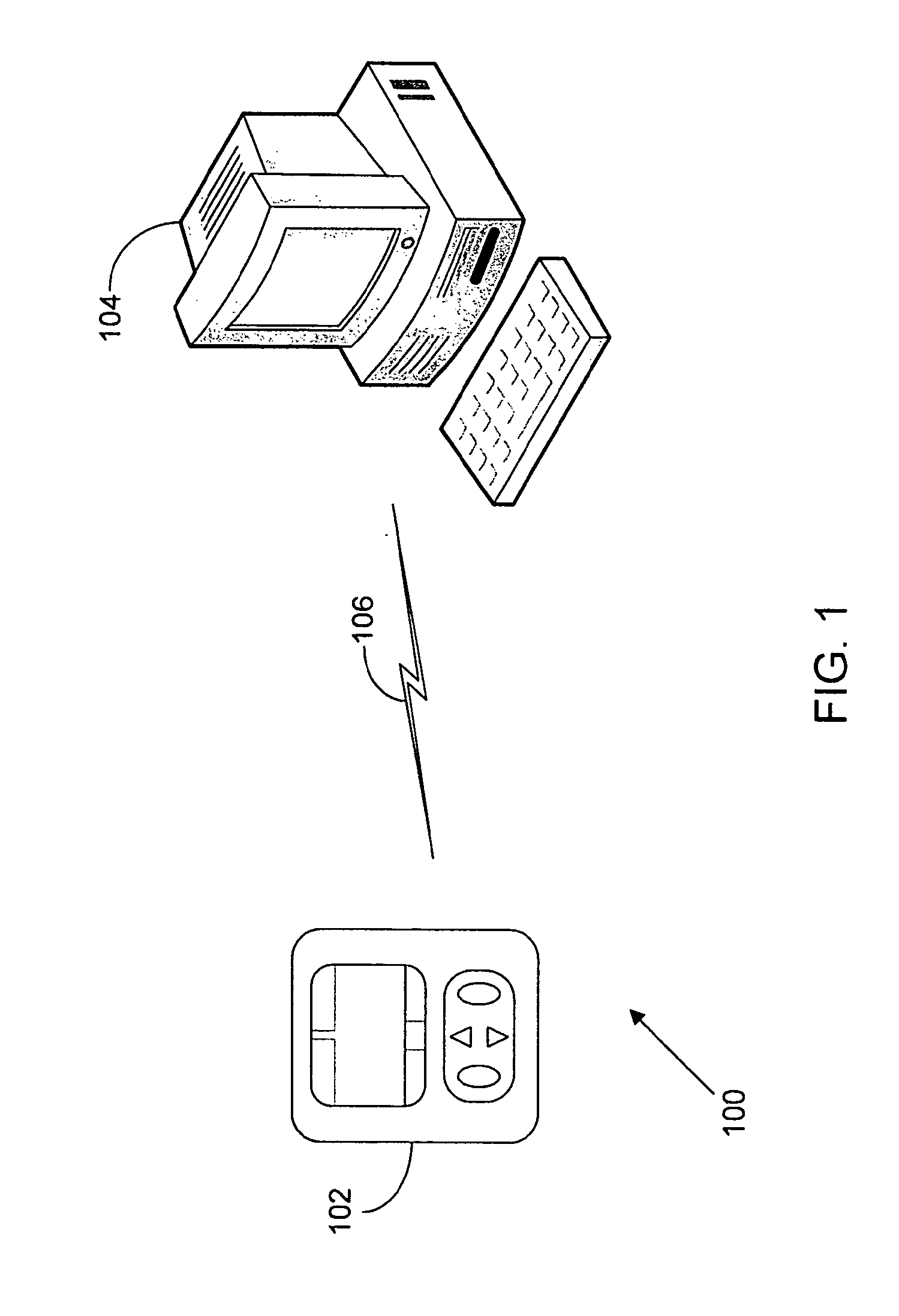

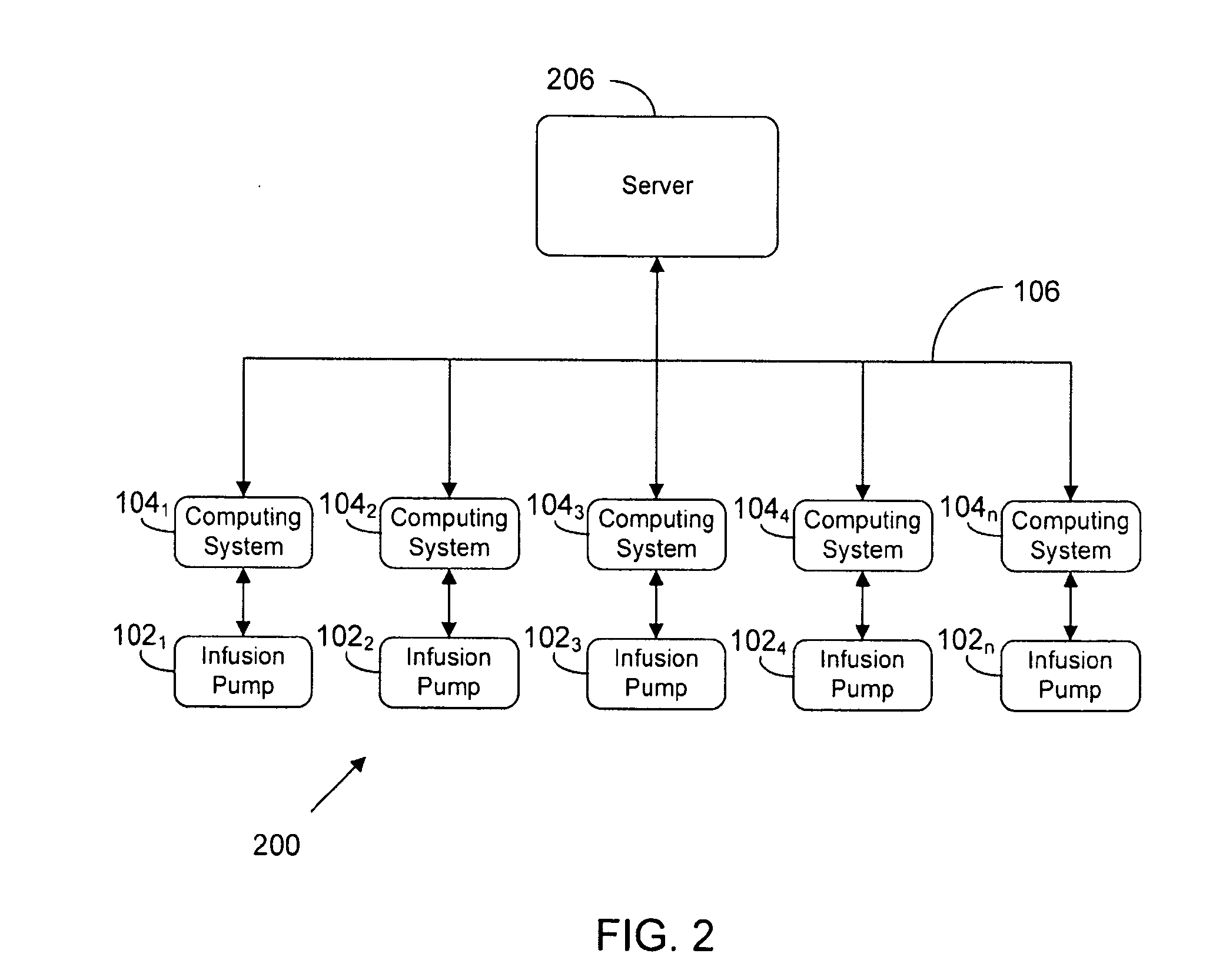

Interface for medical infusion pump

ActiveUS20120172802A1Frequency-division multiplex detailsDrug and medicationsElectricityProgrammable circuits

An apparatus for indicating a change in operation of a medical infusion pump. The apparatus includes a memory configured to store an original pump parameter and a current pump parameter. The apparatus further includes a programmable circuit in electrical communication with the memory, the programmable circuit programmed to display the original pump parameter and the current pump parameter. A method indicates a change in operation of a medical infusion pump.

Owner:SMITHS MEDICAL ASD INC

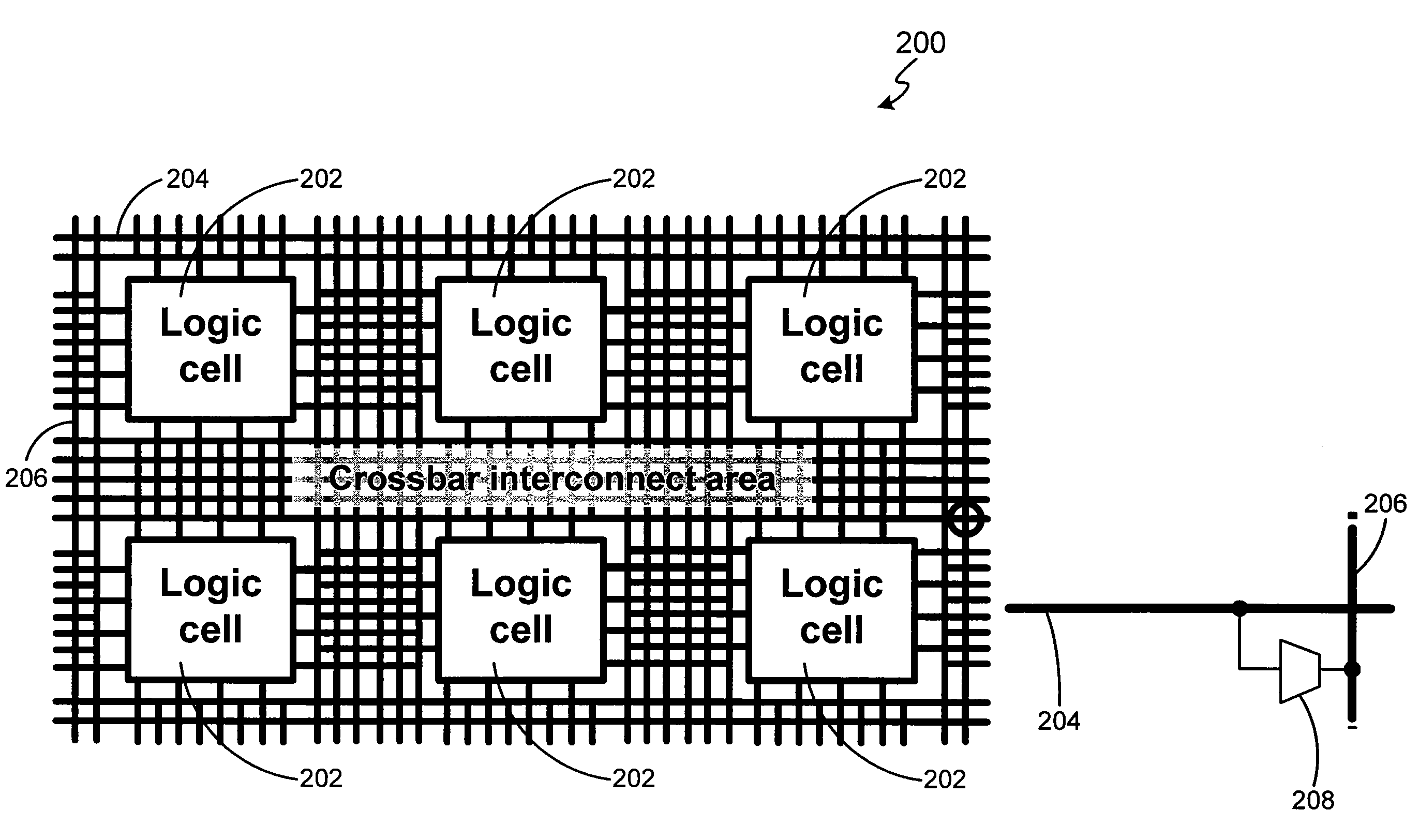

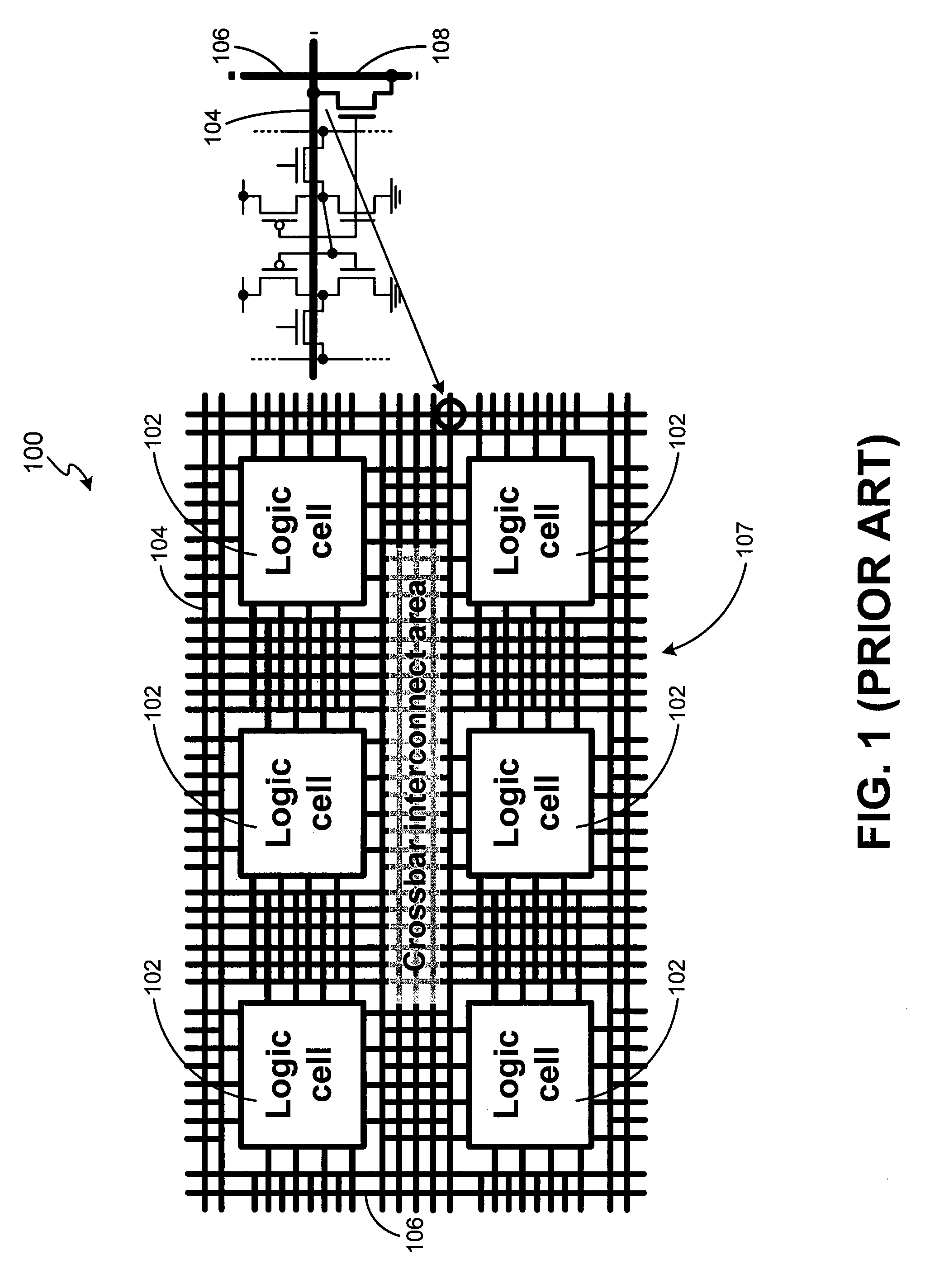

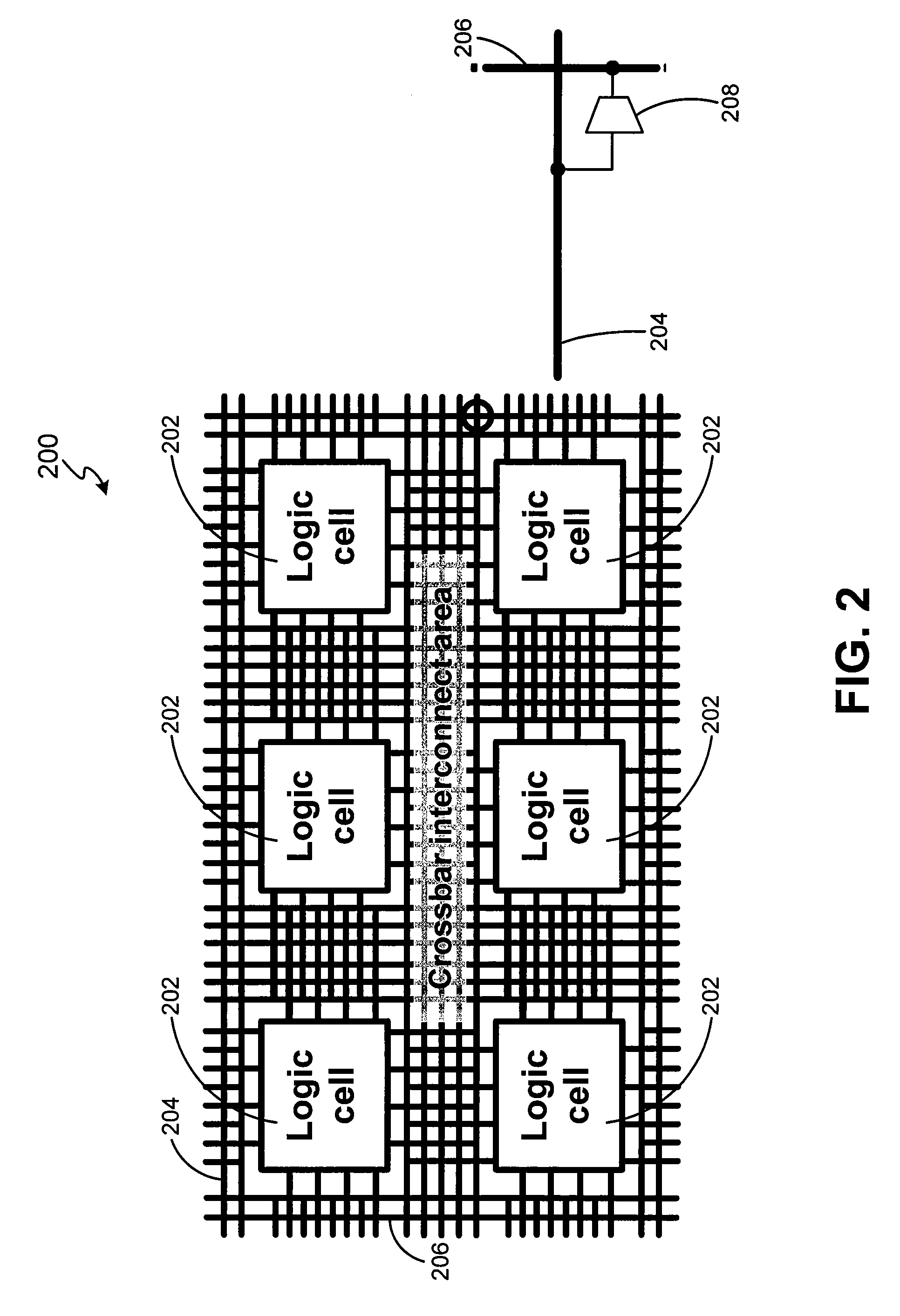

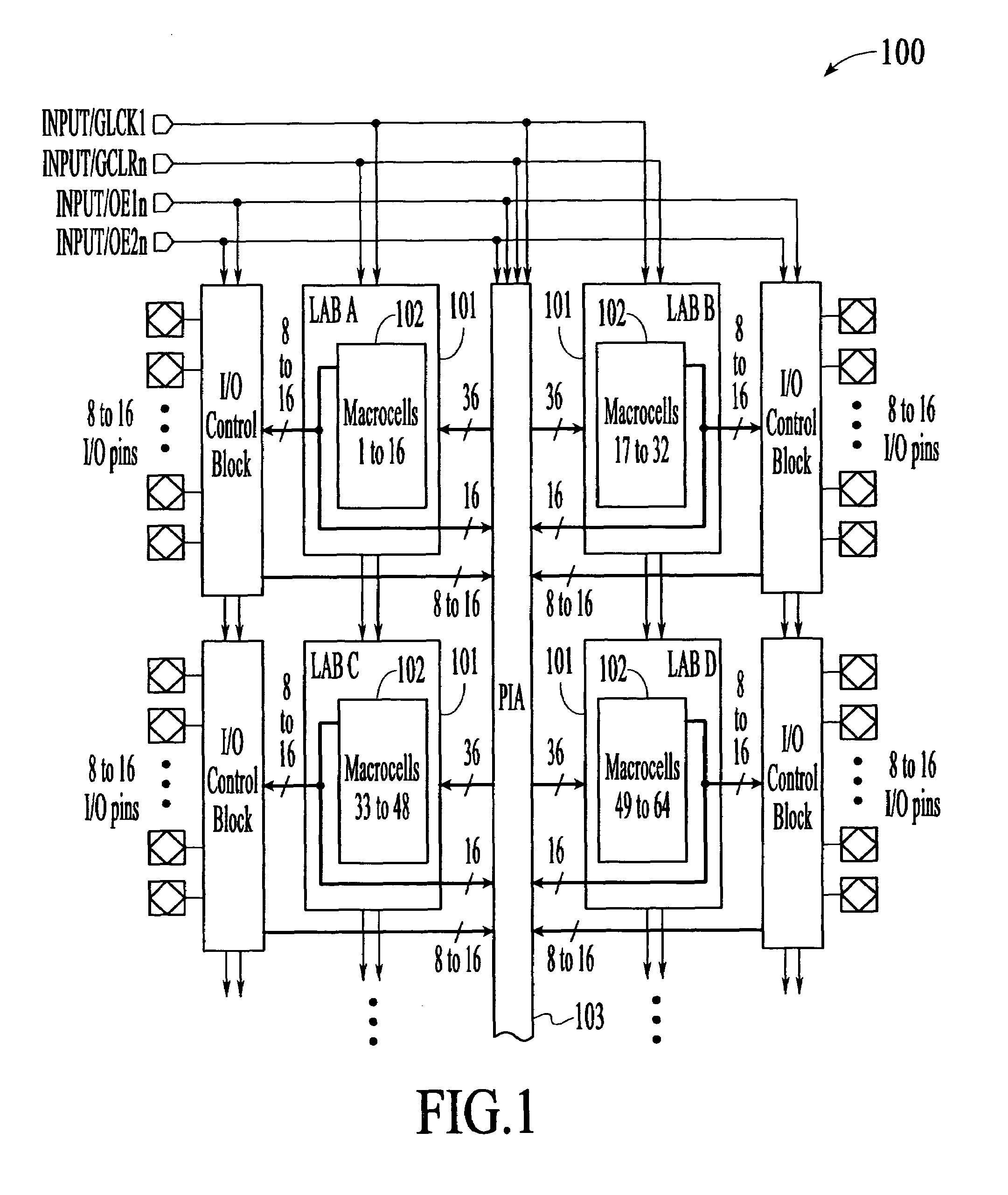

Programmable logic circuit and method of using same

ActiveUS7402847B2Semiconductor/solid-state device detailsSolid-state devicesProgrammable logic deviceLogic cell

A programmable logic circuit, including programmable memory element, suitable for microprocessor applications, and a method of using the circuit are disclosed. The programmable circuit includes at least one logic cell, columns and rows of wires coupled to the logic cell, and a programmable memory element located at the intersection of two wires. The programmable element acts as a switch and as memory for the logic circuit.

Owner:AXON TECH

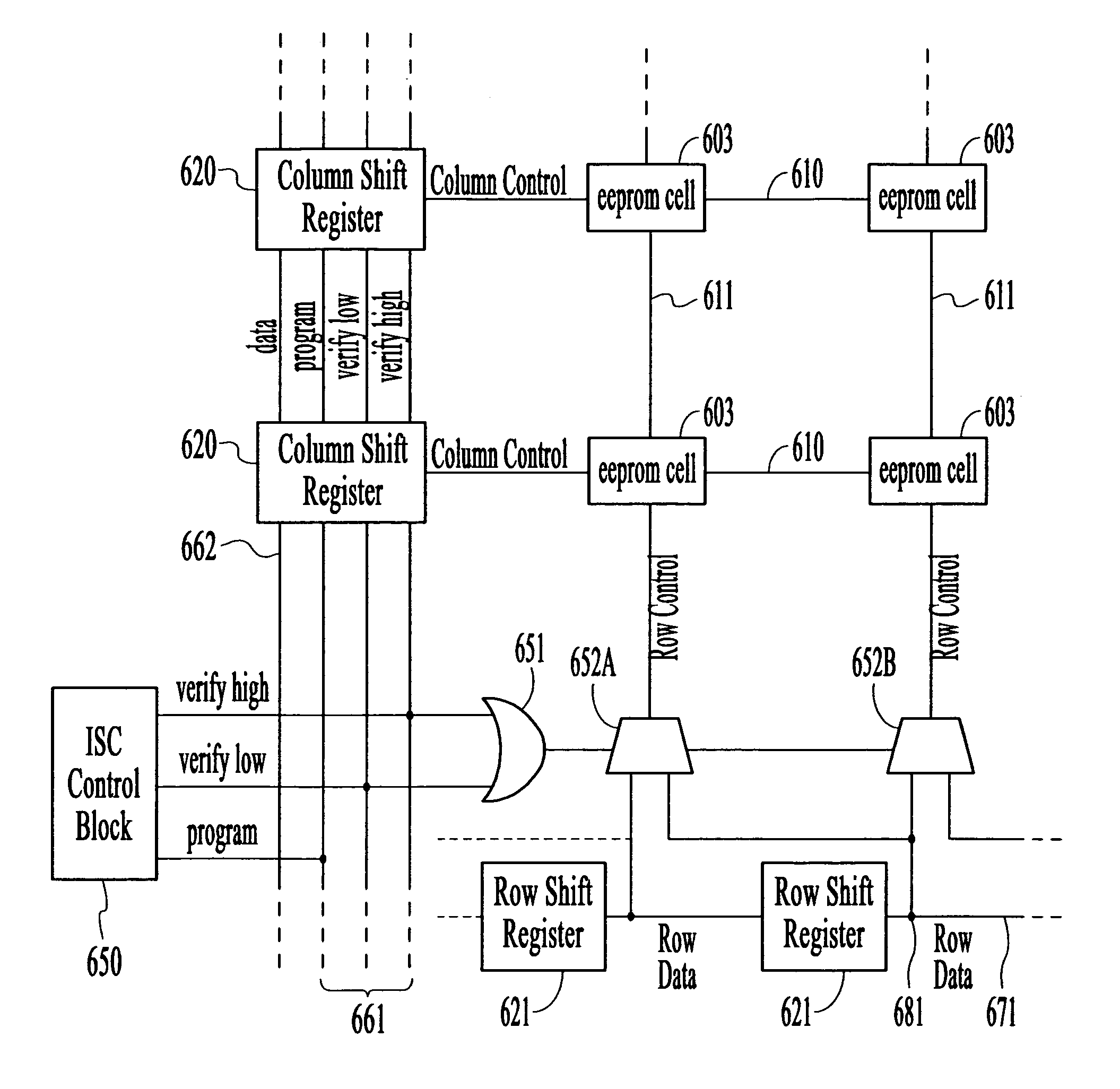

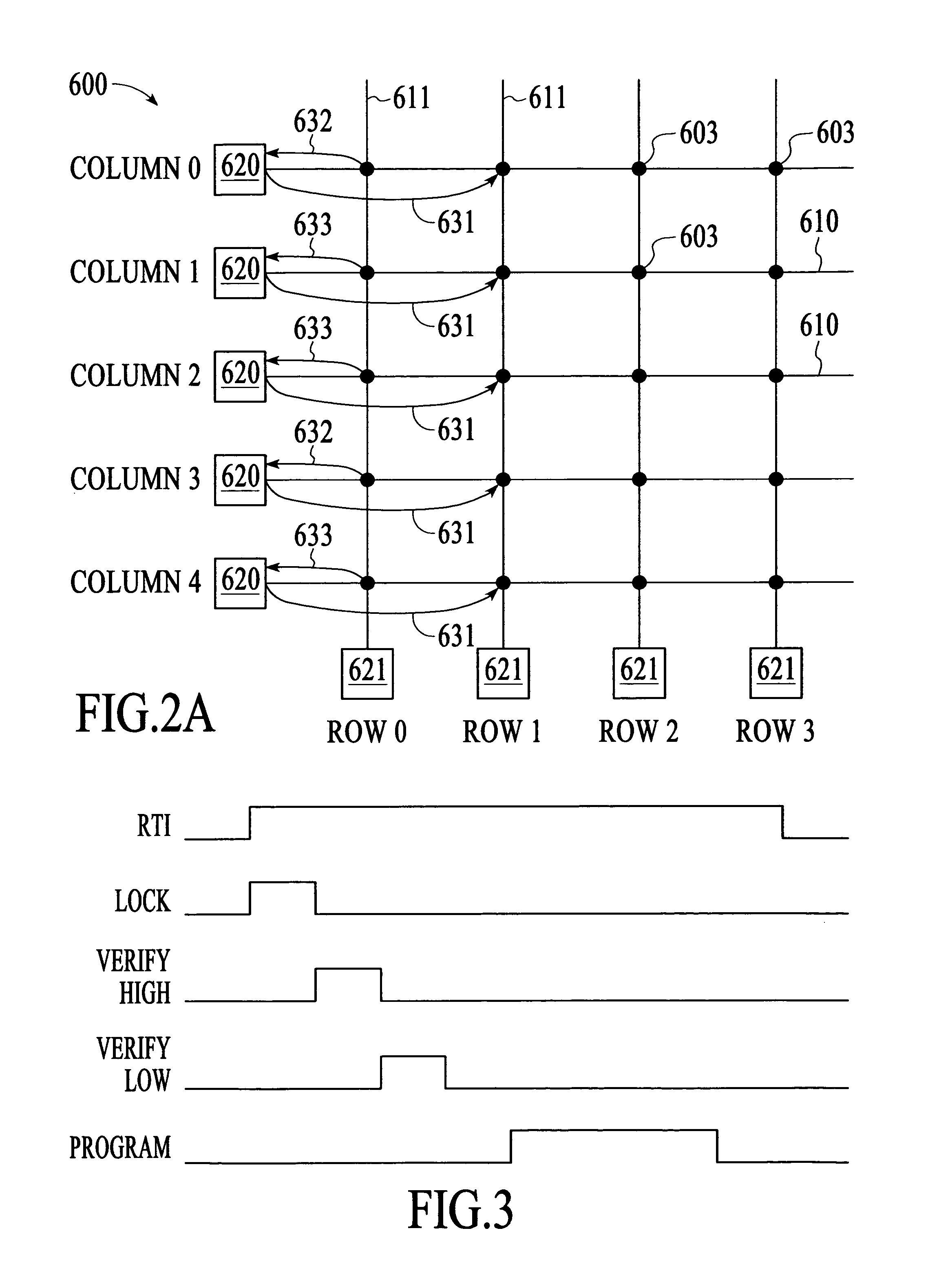

Techniques for programming and verifying data in a programmable circuit

InactiveUS7058880B1Reduce in quantityReduce countError preventionTransmission systemsShift registerParallel computing

The present invention includes techniques for programming and verifying data in a programmable circuit. Programmable circuits such as PLDs may include a plurality of rows and columns of memory cells. Data is programmed into memory elements associated with the rows and columns. Subsequently, the programmed data may be extracted for verification. A first word line may be selected by first word line address bits in row shift registers. Data programmed into the first word line is loaded into column shift registers for verification during one or more verify steps. During a program step, data is programmed into memory elements in a second word line that is selected by the first word line address bits. The present invention also provides a technique for shifting program data bits into the column shift registers at the same time that verify data bits are shifted out of the column shift registers.

Owner:ALTERA CORP

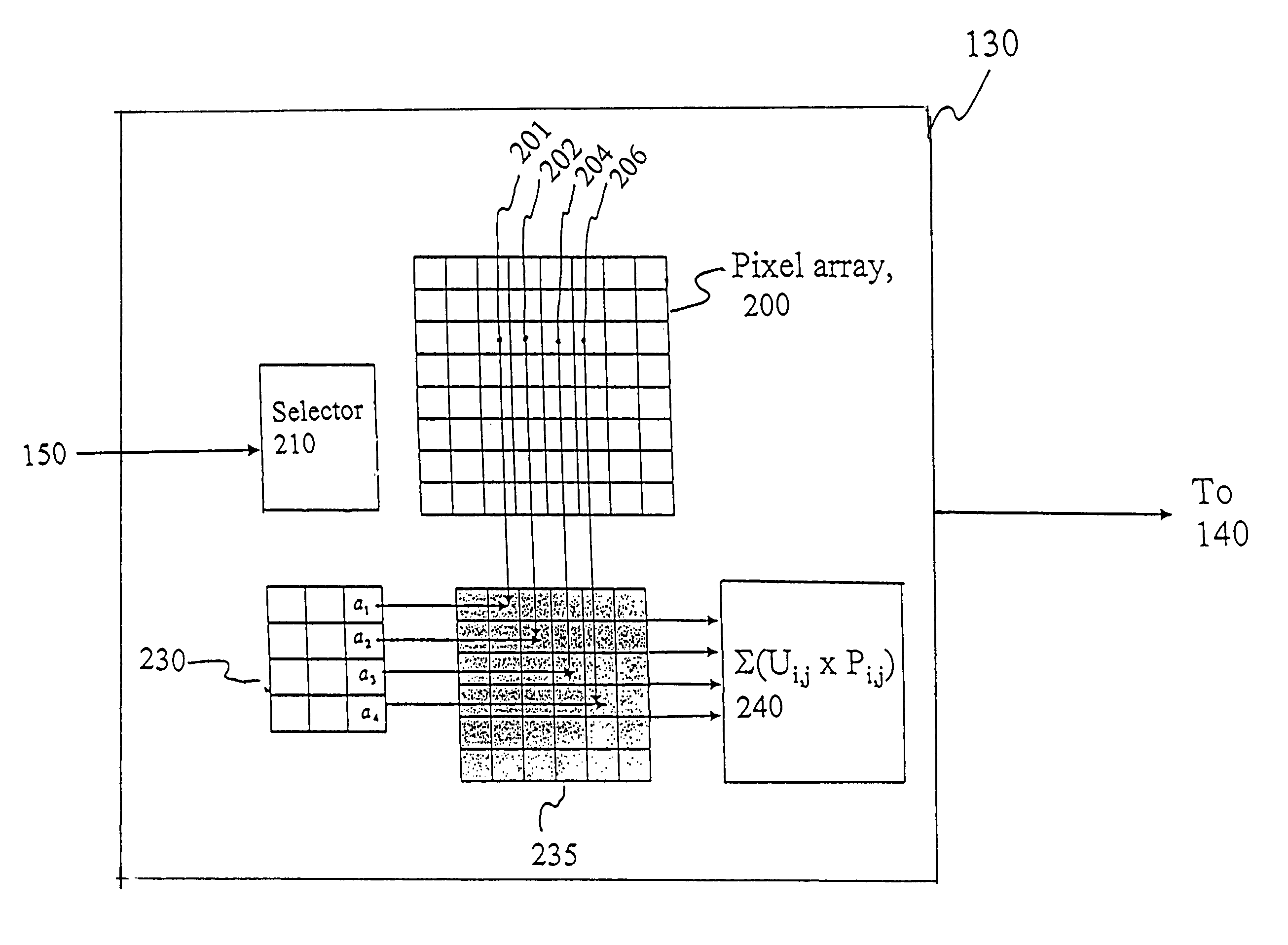

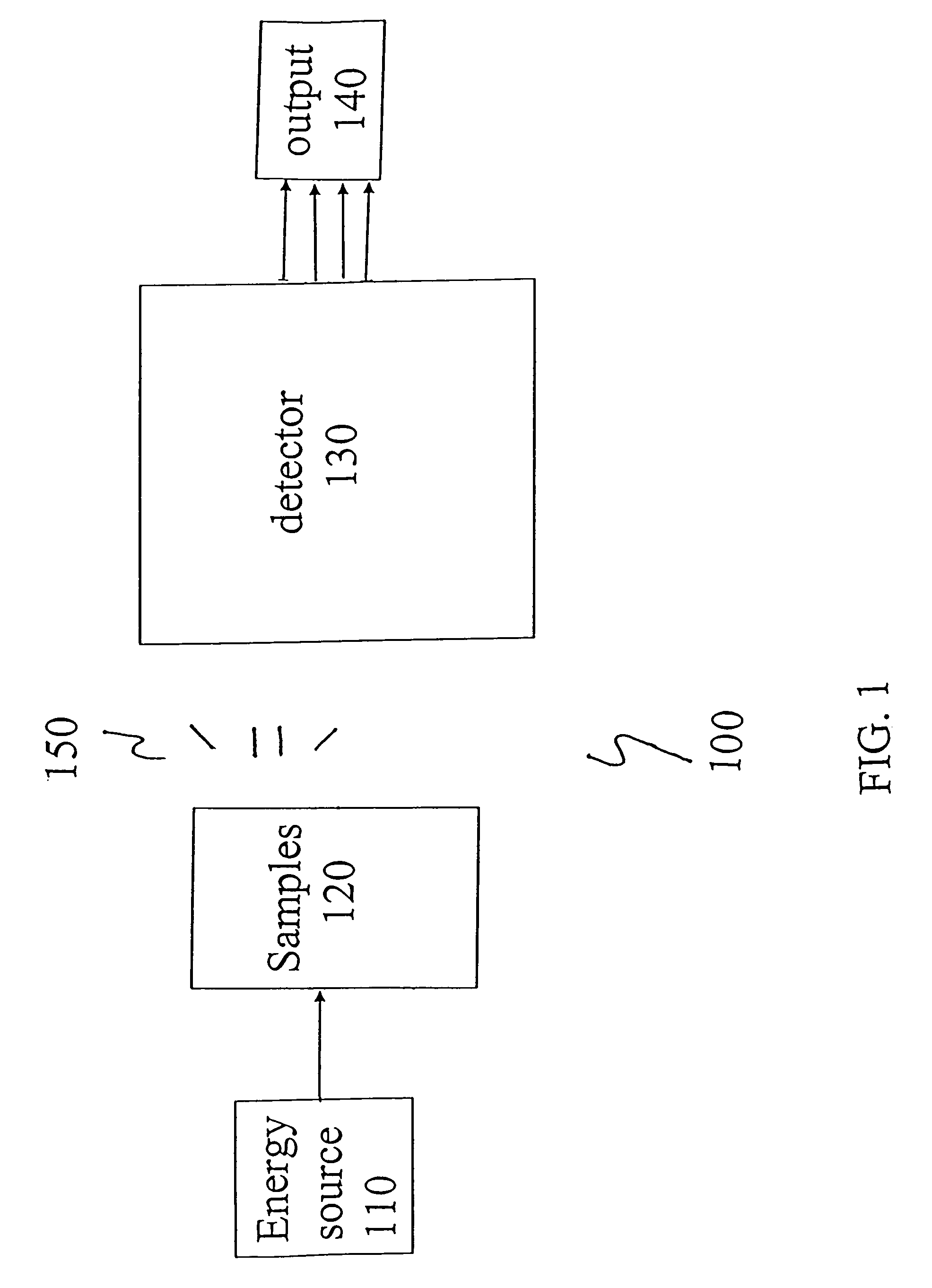

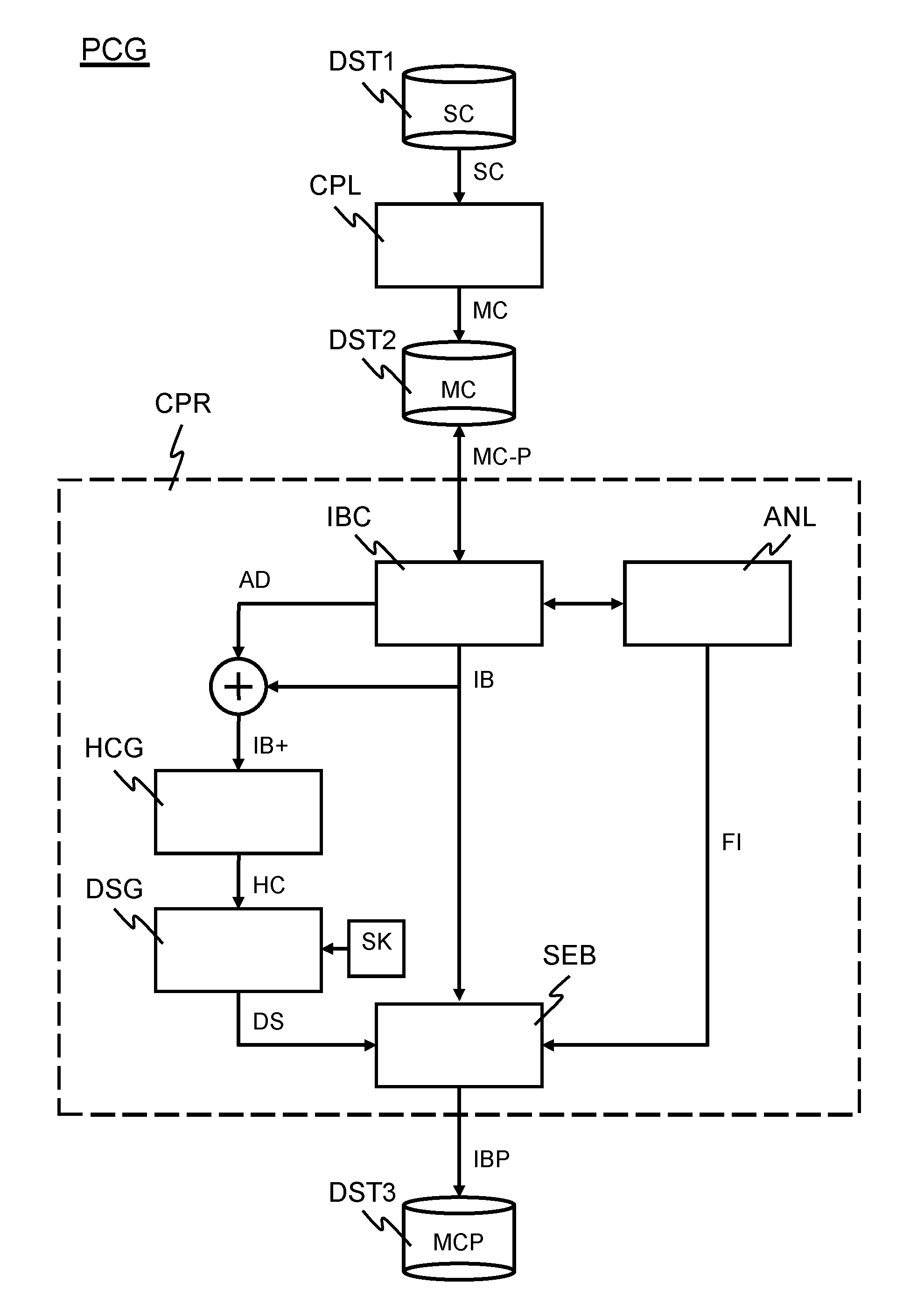

High throughput reconfigurable data analysis system

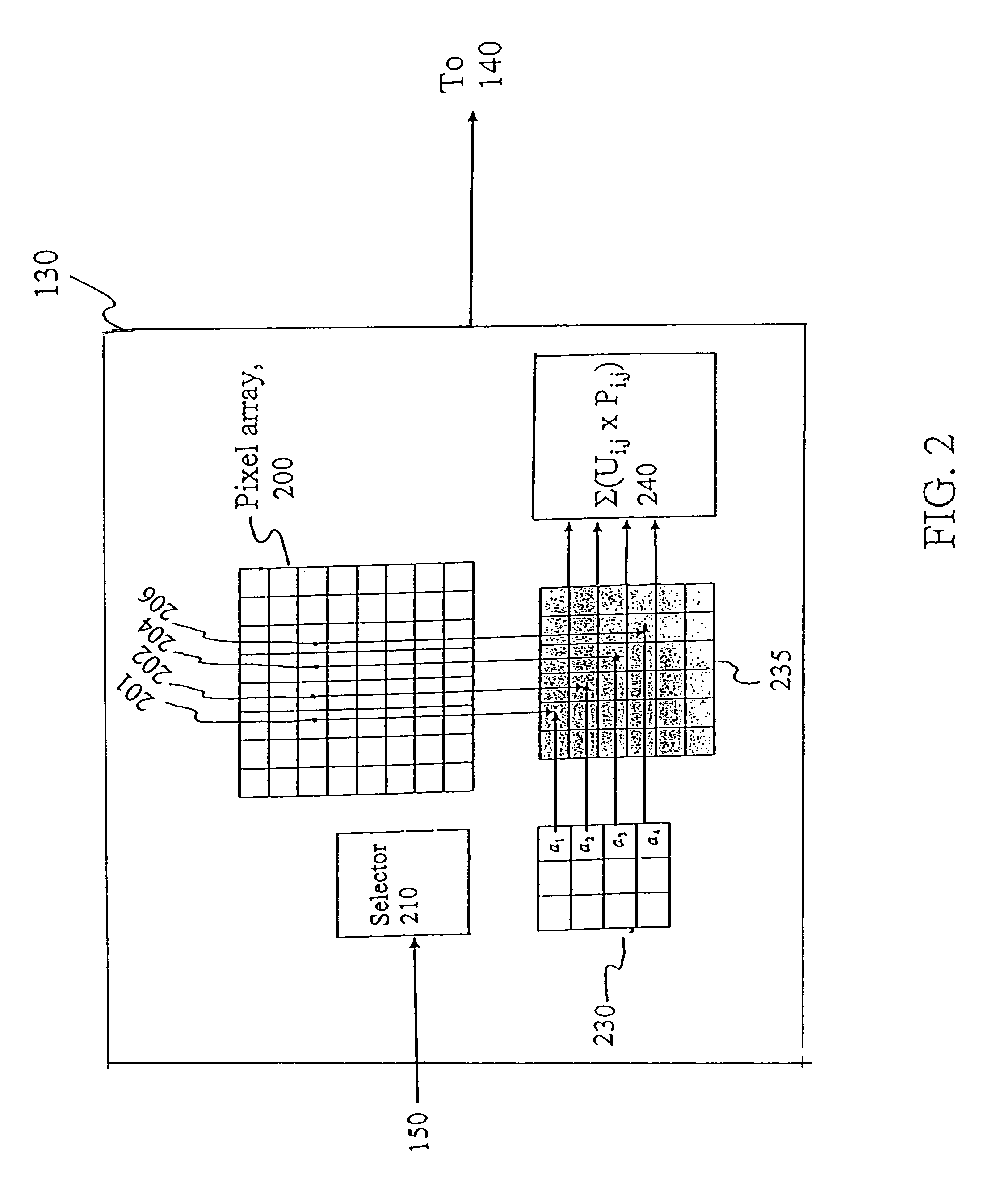

InactiveUS7471831B2Rapid and programmable analysisTelevision system detailsElectric signal transmission systemsProgrammable circuitsData analysis system

The present invention relates to a system and method for performing rapid and programmable analysis of data. The present invention relates to a reconfigurable detector comprising at least one array of a plurality of pixels, where each of the plurality of pixels can be selected to receive and read-out an input. The pixel array is divided into at least one pixel group for conducting a common predefined analysis. Each of the pixels has a programmable circuitry programmed with a dynamically configurable user-defined function to modify the input. The present detector also comprises a summing circuit designed to sum the modified input.

Owner:CALIFORNIA INST OF TECH

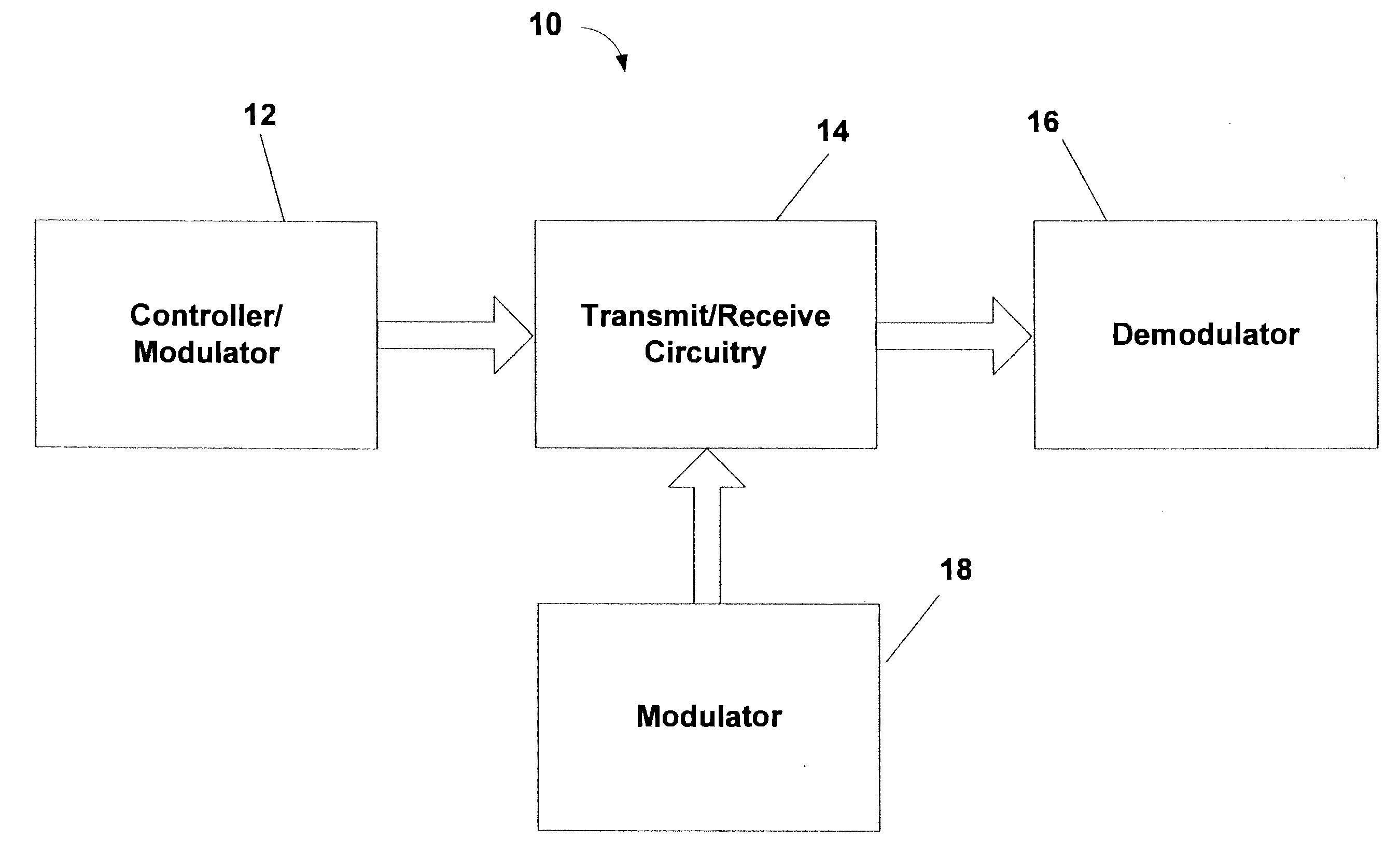

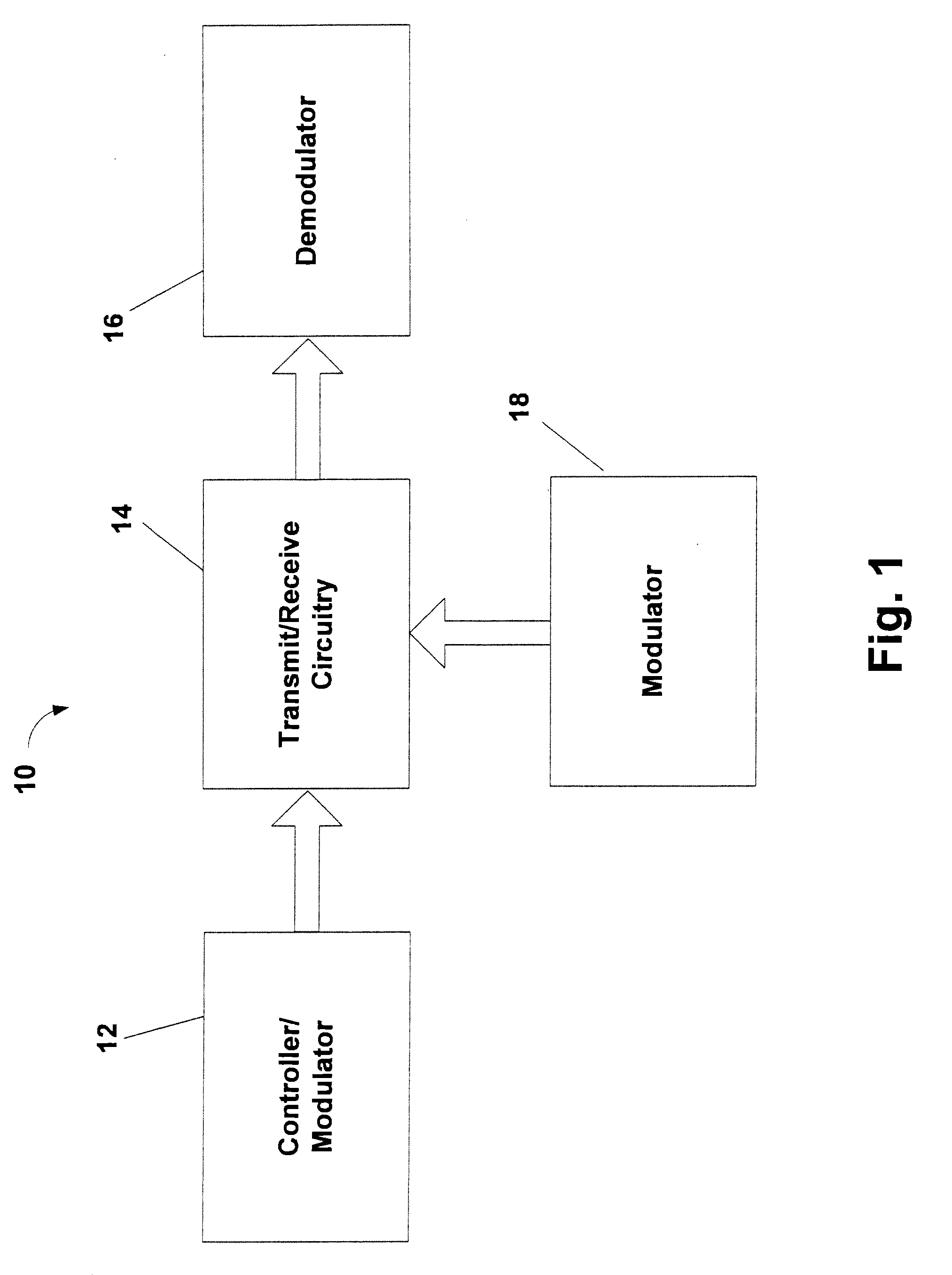

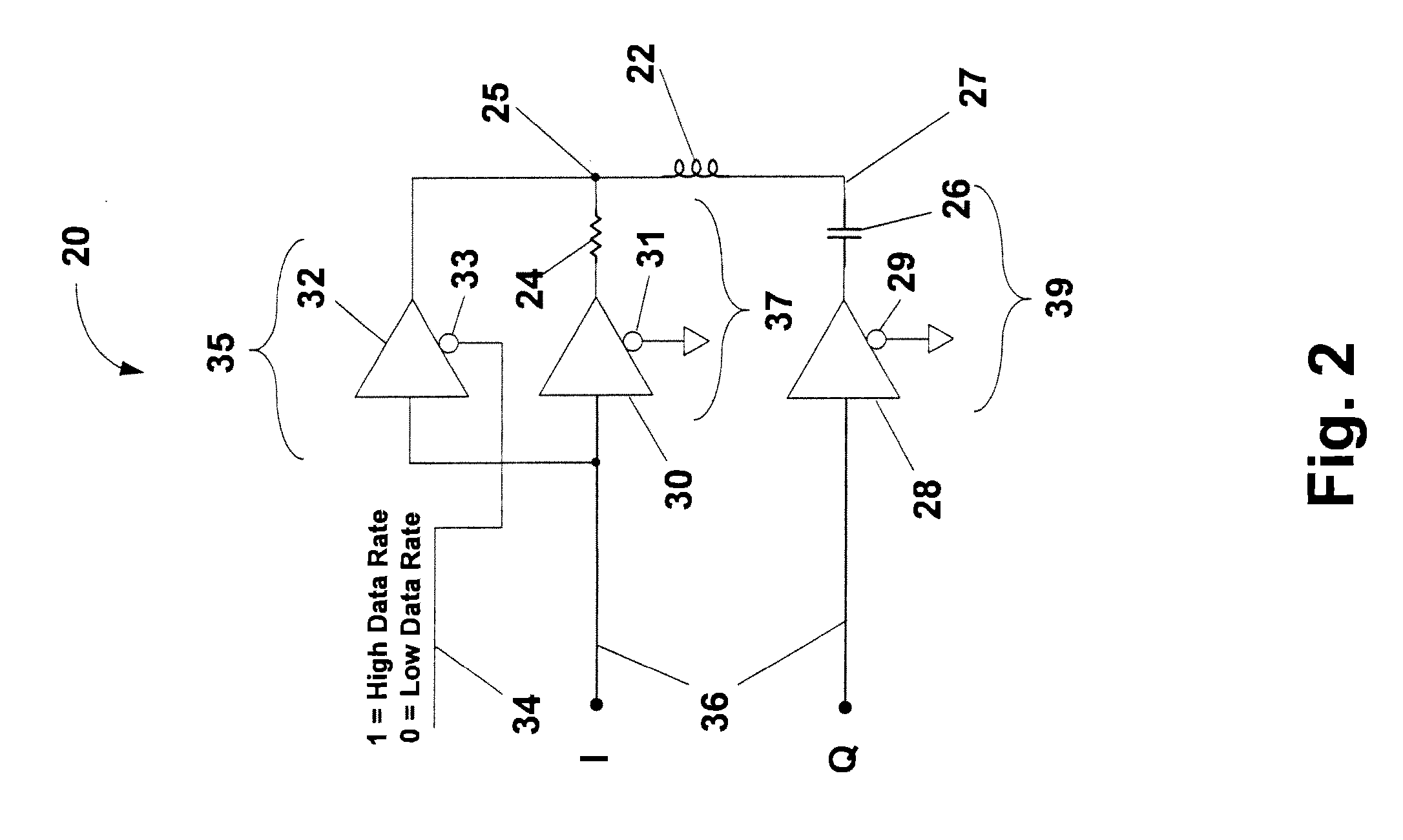

Telemetry system and method with variable parameters

ActiveUS20080055111A1High bandwidthElectric signal transmission systemsElectrotherapyCapacitanceHigh bandwidth

A programmable telemetry circuit that may be programmed for high bandwidth, low Q; low bandwidth, high Q; or for other parameters. The programmable telemetry circuit may include a first coil; a high impedance path having a first node connected to a first node of the first coil; a low impedance path having a first node connected to the first node of the first coil; a capacitive path having a first node connected to a second node of the first coil; and an input path for coupling signals into the high impedance path, the low impedance path, and the capacitive path. The low impedance path may be connected in parallel with the high impedance path. The capacitive path may form a circuitous path with the high impedance path and the low impedance path. The programmable circuit may be programmed to select the high impedance path or the low impedance path.

Owner:MEDTRONIC MIMIMED INC

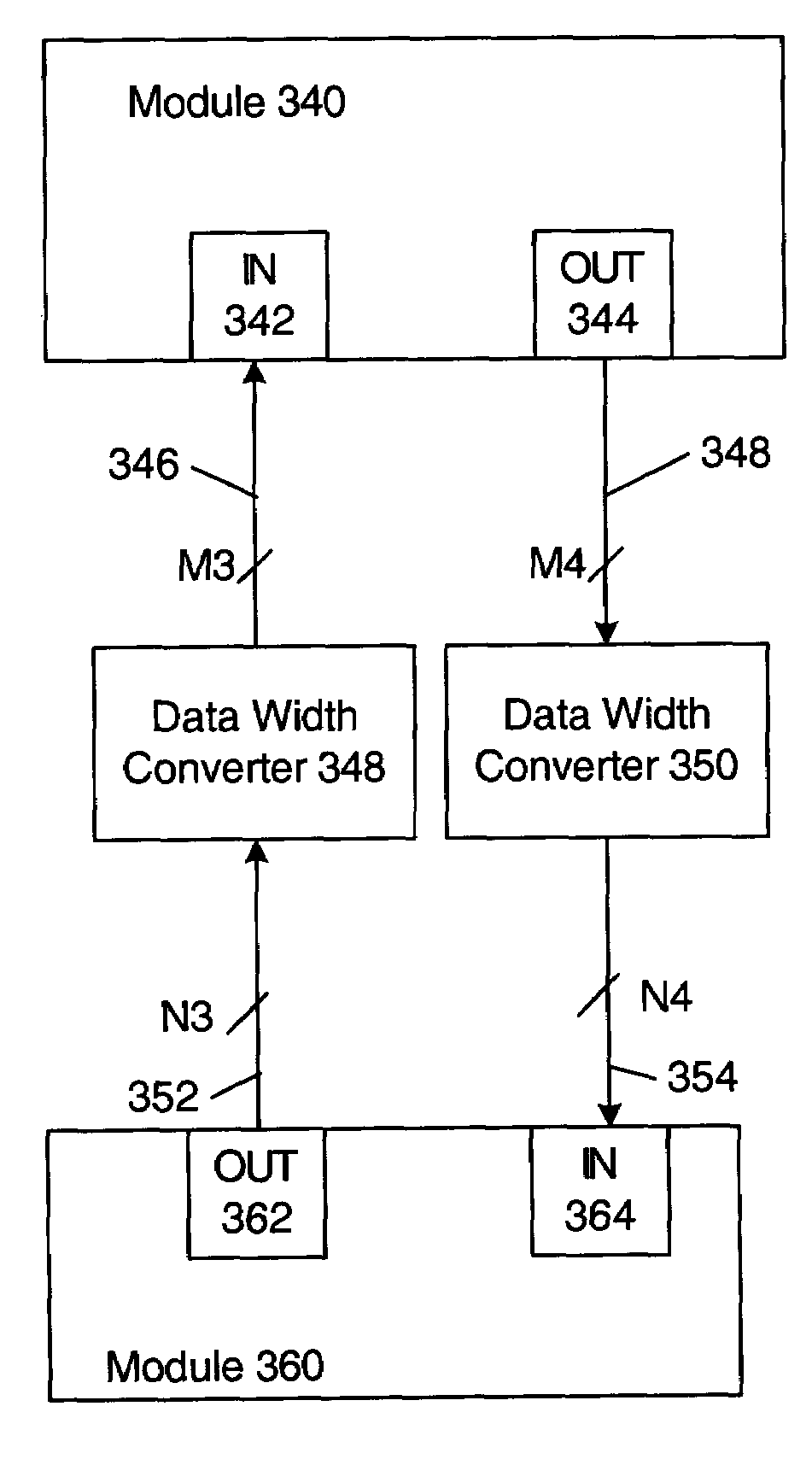

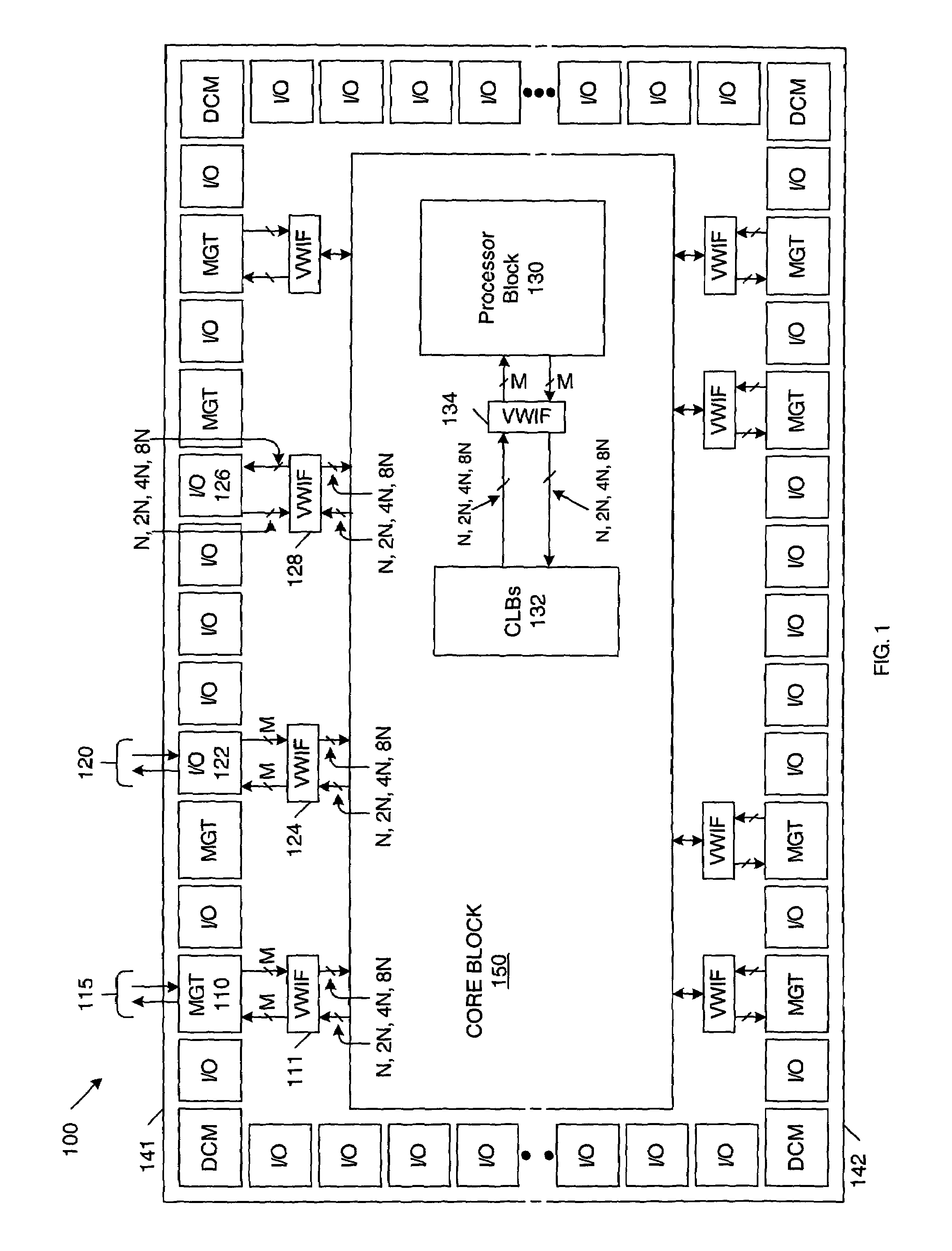

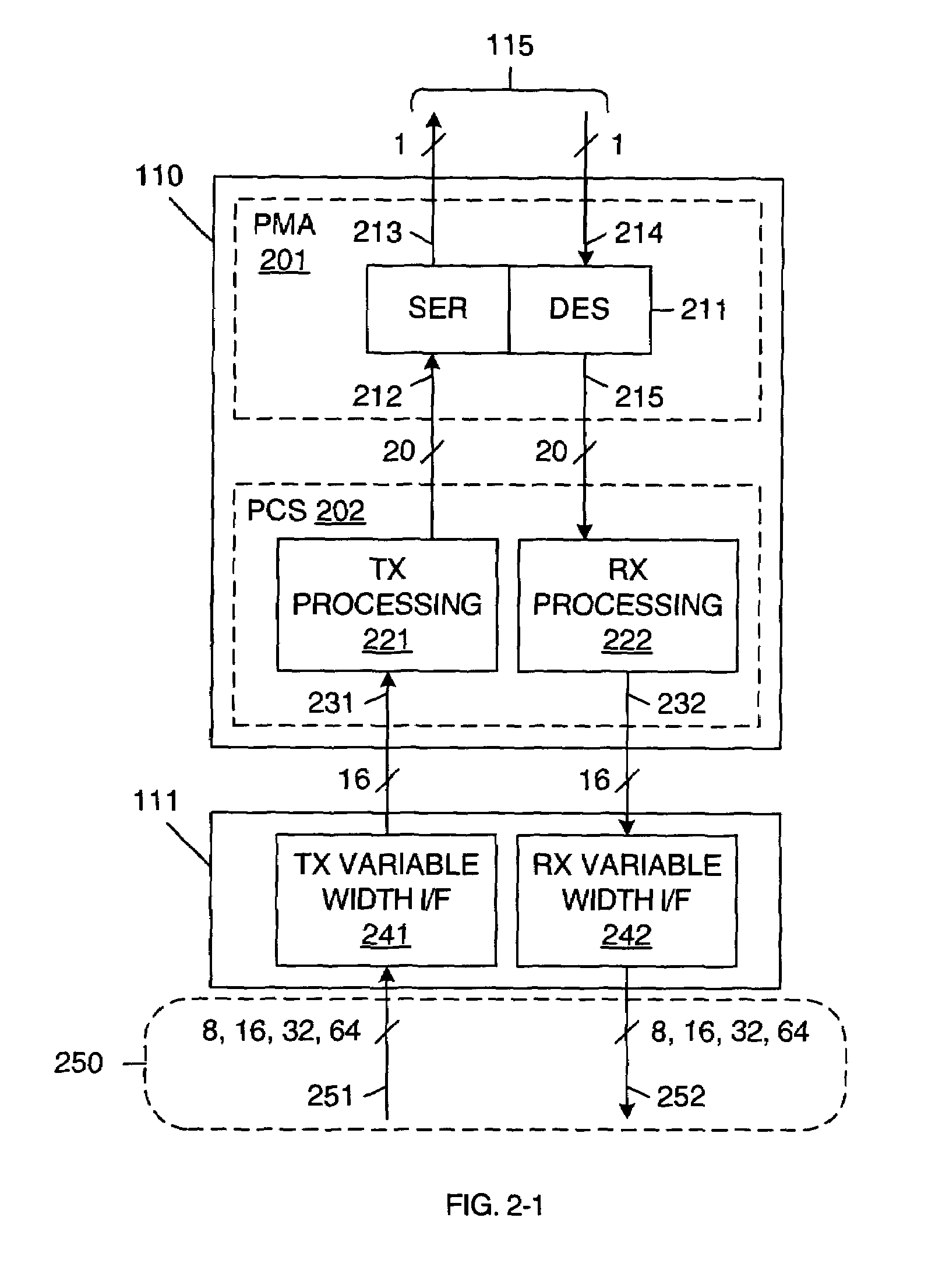

Variable data width converter

InactiveUS6970013B1Solid-state devicesLogic circuits using elementary logic circuit componentsProgrammable circuitsIntegrated circuit

An integrated circuit (IC) with programmable circuitry having programmable functions and programmable interconnections. The IC further includes: a first module having an output with a first fixed data width or first variable data width; a second module having an input with a second fixed data width or a second variable data width; and a data width converter receiving data from the output of the first module and sending the data to the input of the second module, the data width converter configured to convert data from the first fixed data width or first variable data width to the second fixed data width or the second variable data width.

Owner:XILINX INC

Endoscopy device supporting multiple input devices

The present invention provides a remote-head imaging system with a camera control unit capable of supporting multiple input devices. The camera control unit detects an input device to which it is connected and changes the camera control unit's internal functionality accordingly. Such changes includes altering clock timing, changing video output parameters, and changing image processing software. In addition, a user is able to select different sets of software program instructions and hardware configuration information based on the head that is attached. The remote-head imaging system utilizes field-programmable circuitry, such as field-programmable gate arrays (FPGA), in order to facilitate the change in configuration.

Owner:GYRUS ACMI INC (D B A OLYMPUS SURGICAL TECH AMERICA)

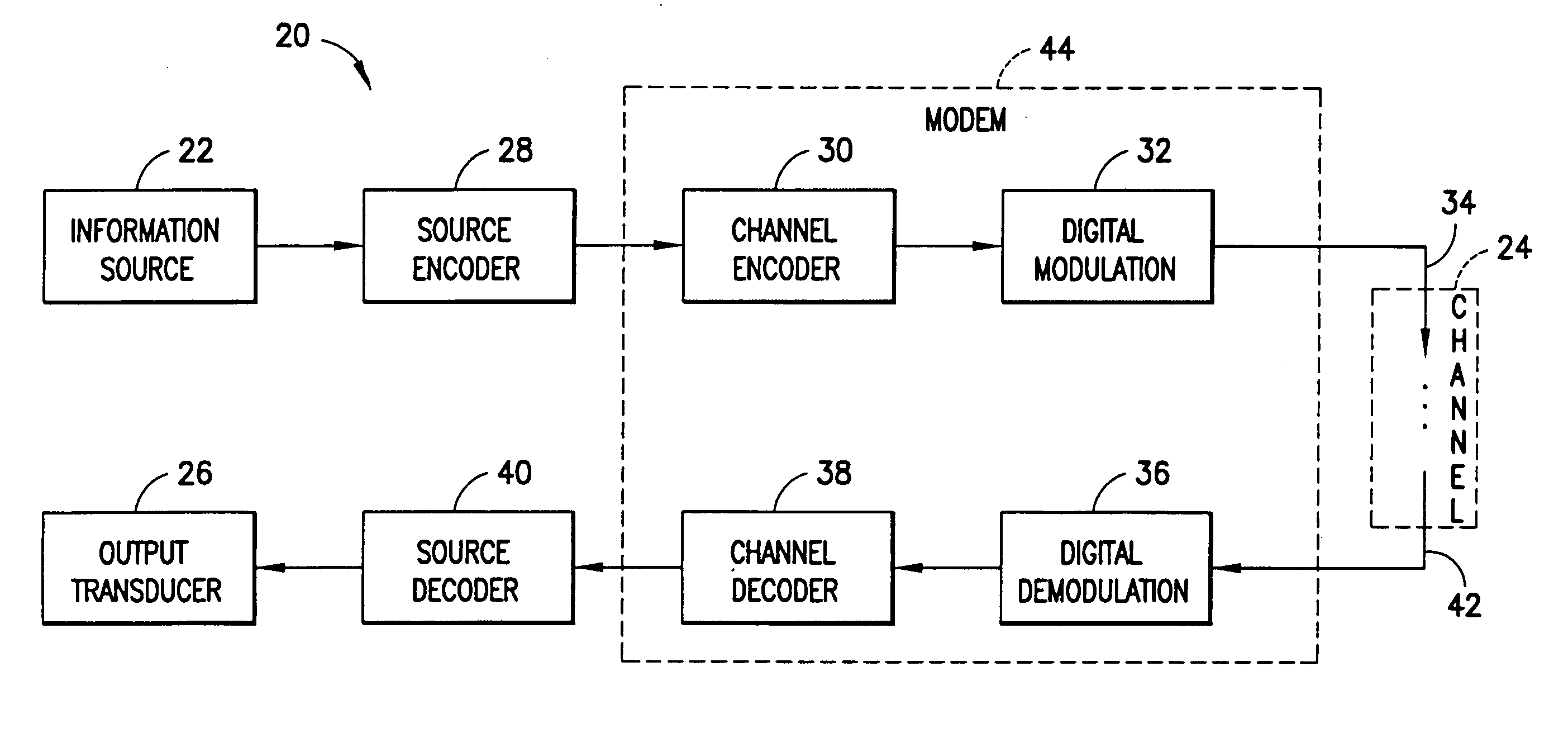

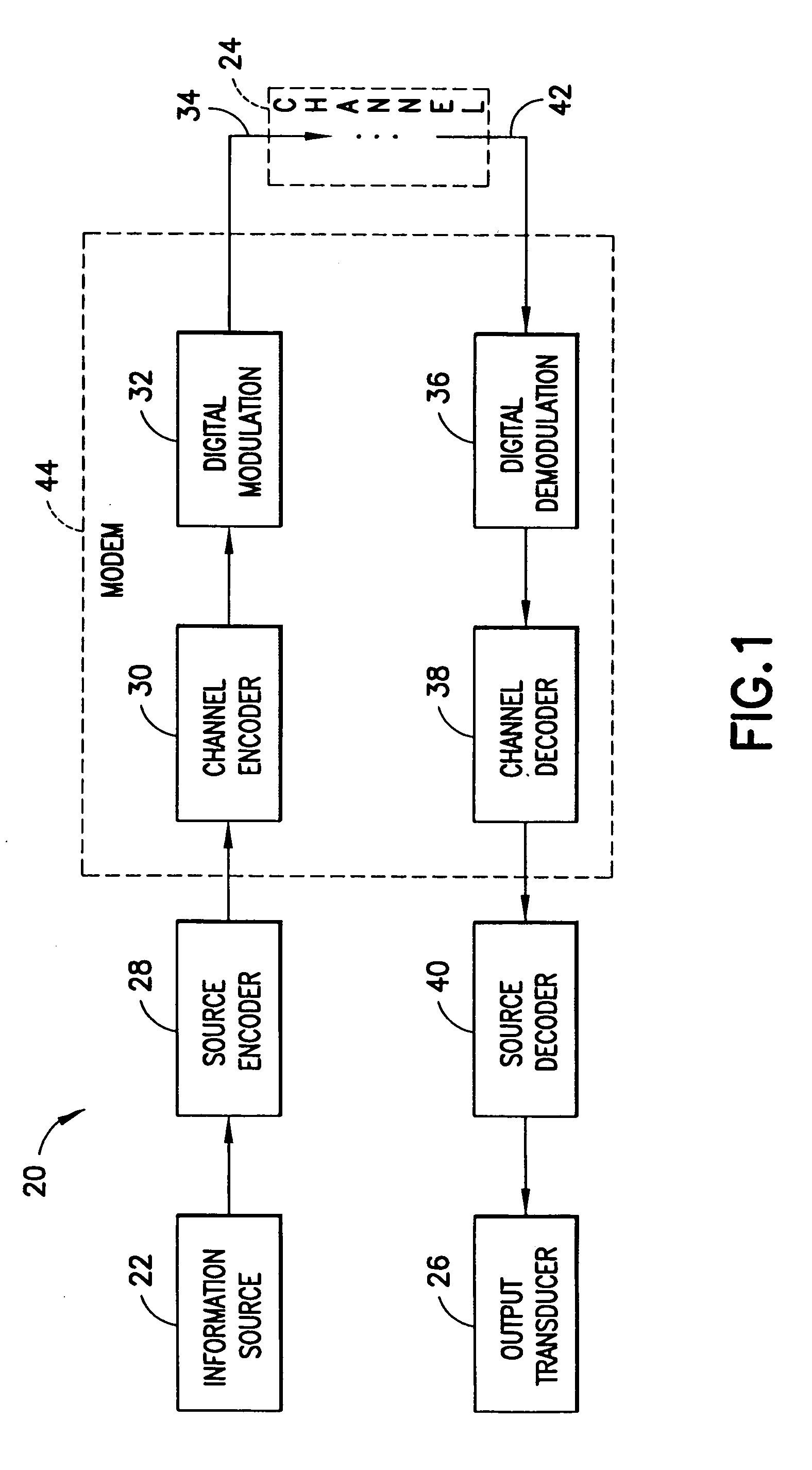

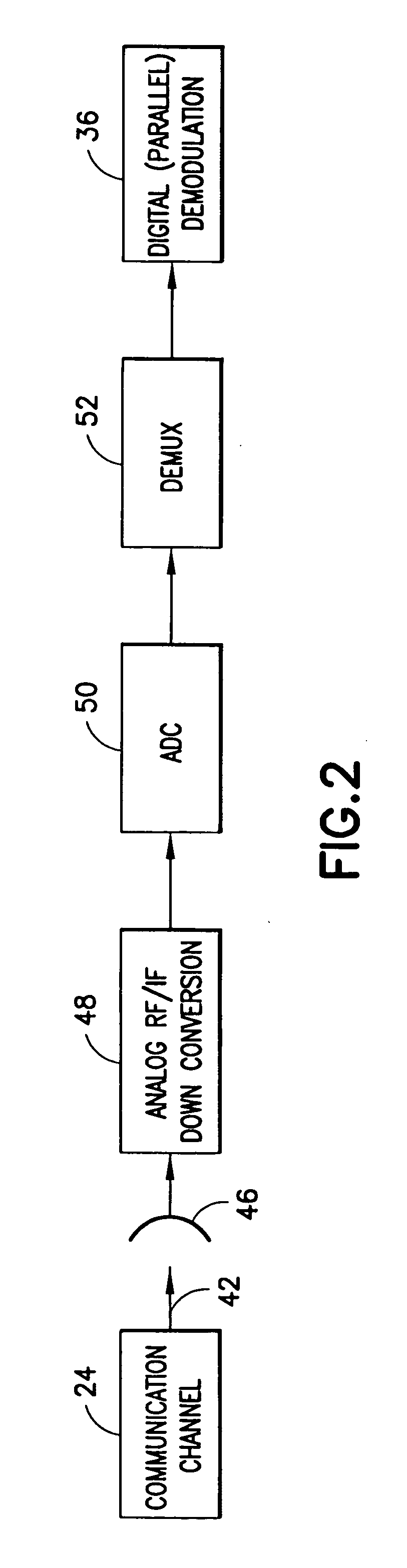

Parallel DSP demodulation for wideband software-defined radios

ActiveUS20050286619A1Little and programmabilityReduce clock frequencyAmplitude-modulated carrier systemsAmplitude demodulationModem deviceEngineering

A demodulator, suitable for use in a communication system and in a modem, has a block polyphase circuit with circuit blocks for different signal processing functions, particularly filtering, delay, and frequency conversion. The circuit blocks are arranged for parallel processing of different portions of an input sequence of signals. Signals of the input sequence to be filtered are divided among the blocks by a demultiplexer for processing at a clock frequency lower than a clock frequency of the input signal sequence. Signals outputted by groups of the circuit blocks are summed to produce an output signal of the group. Frequency and timing reference signals, as well as fractional delay interpolation, are produced also by parallel-channel circuitry. Output signals of all of the groups are multiplexed to provide an output signal sequence such that the repetition frequency of the outputted signals may be higher, lower, or equal to that of the input signal sequence. This enables use of programmable circuitry operative at clock rates lower than rates required to process directly the input signal sequence.

Owner:L 3 COMM CORP

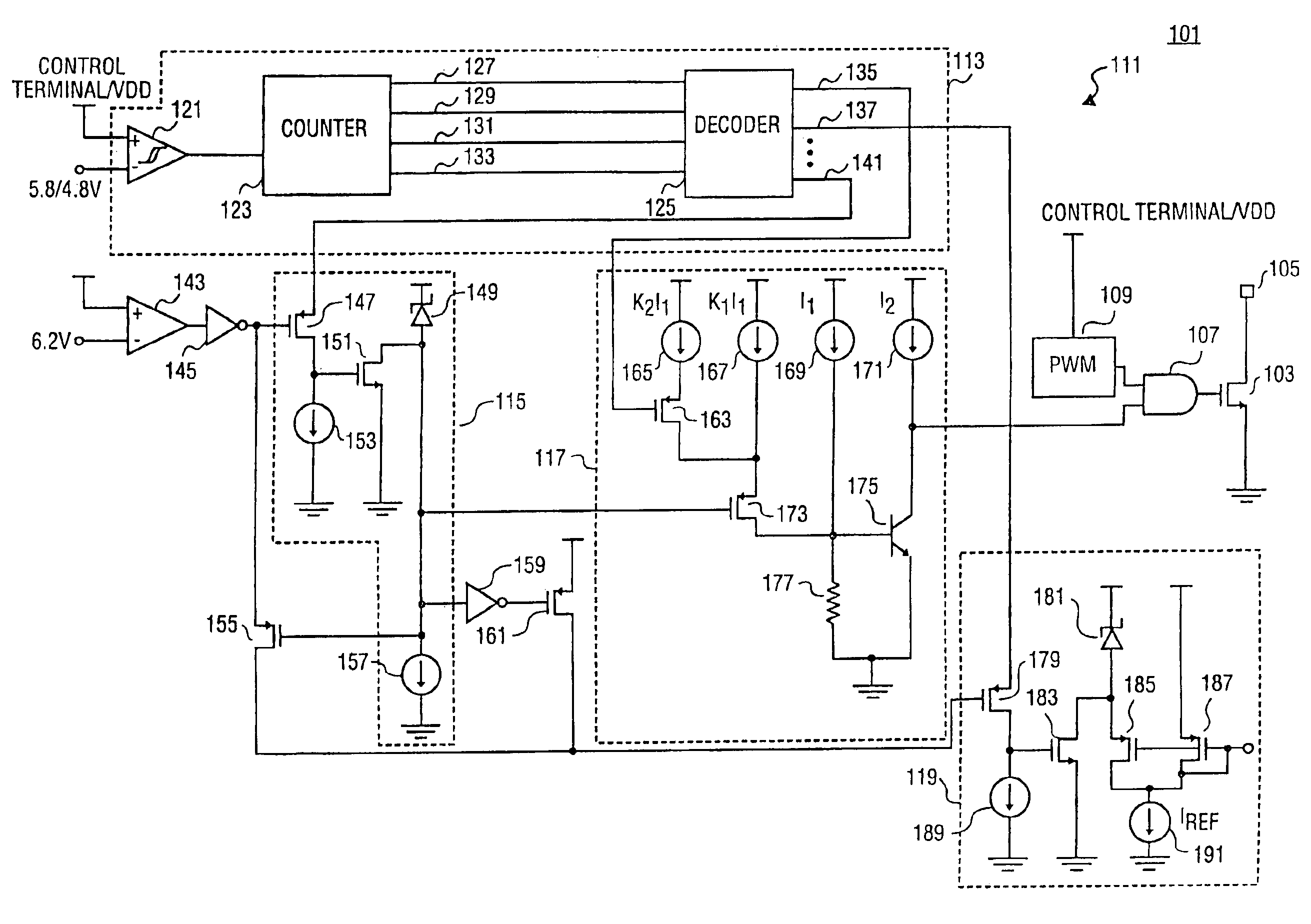

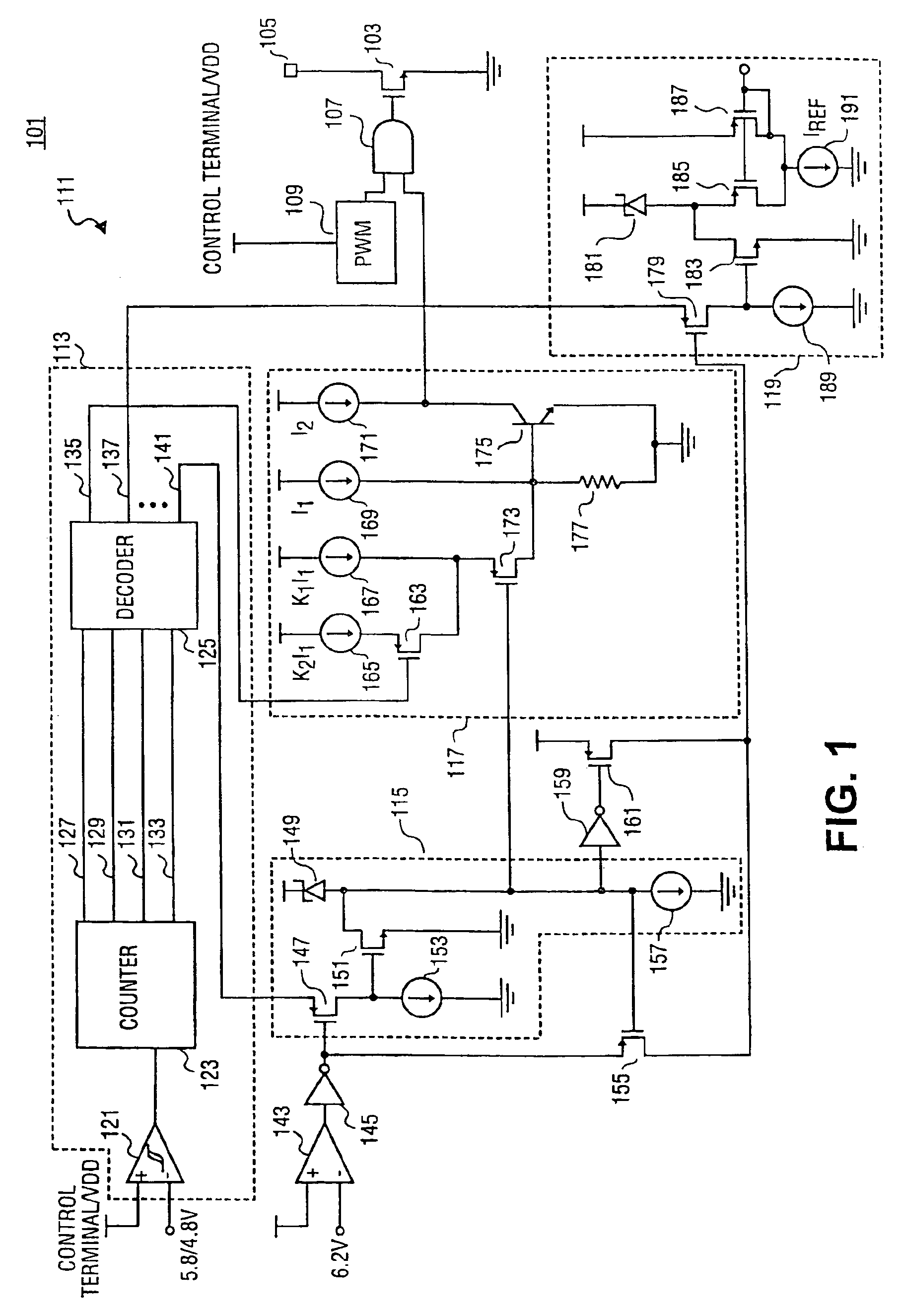

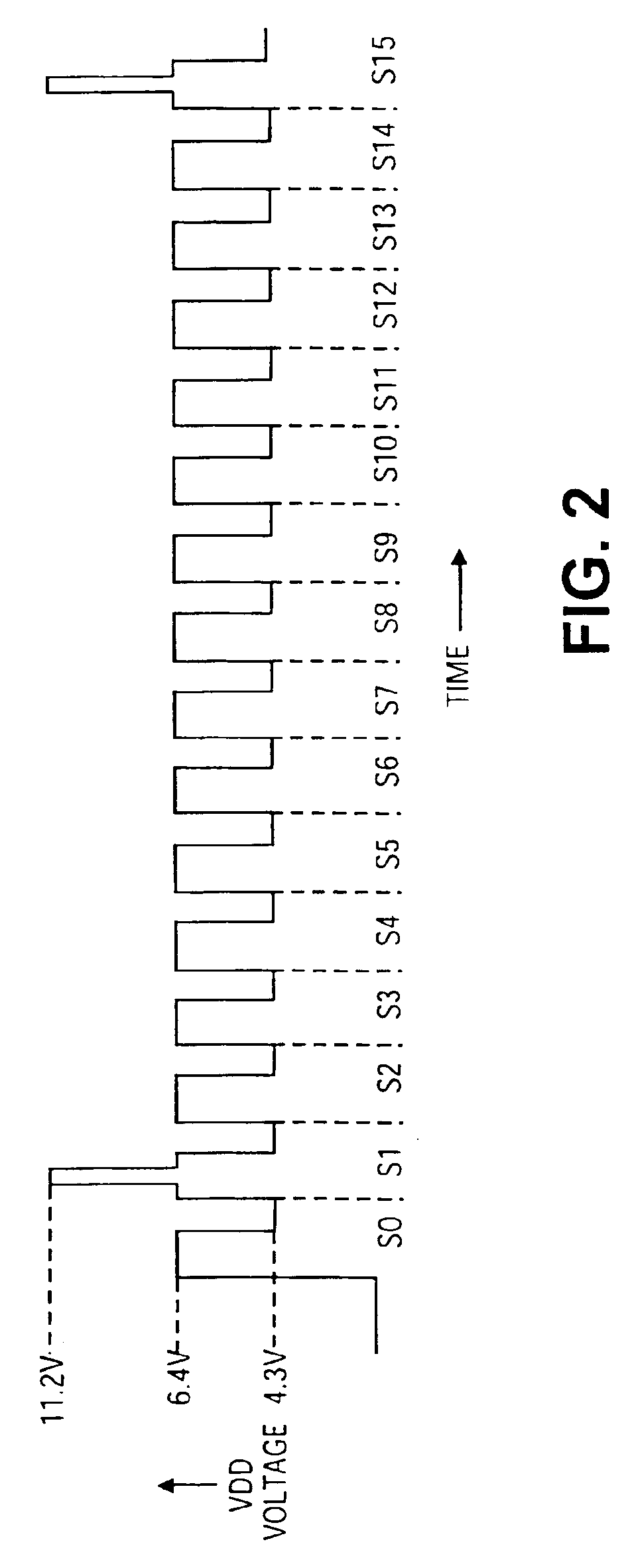

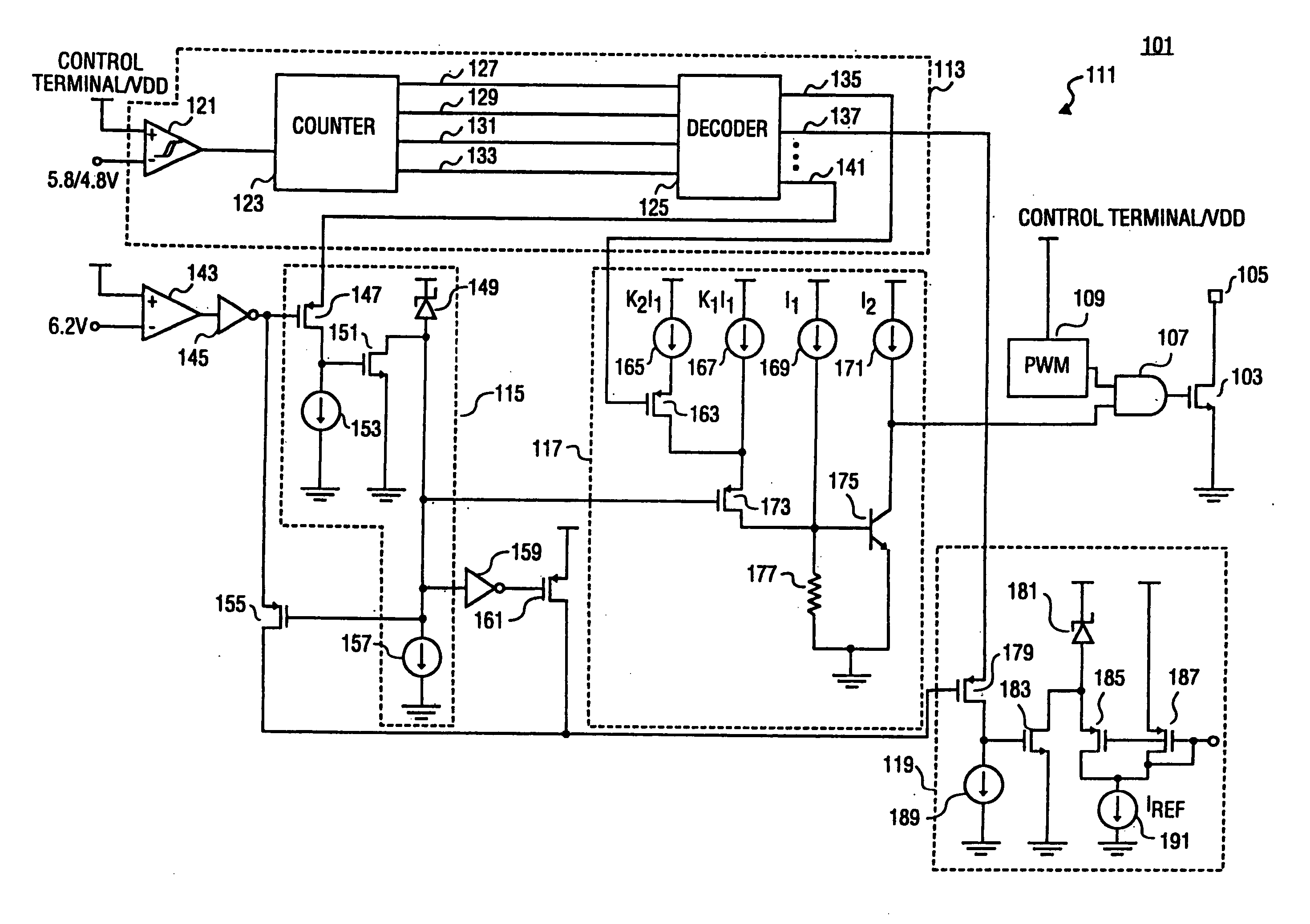

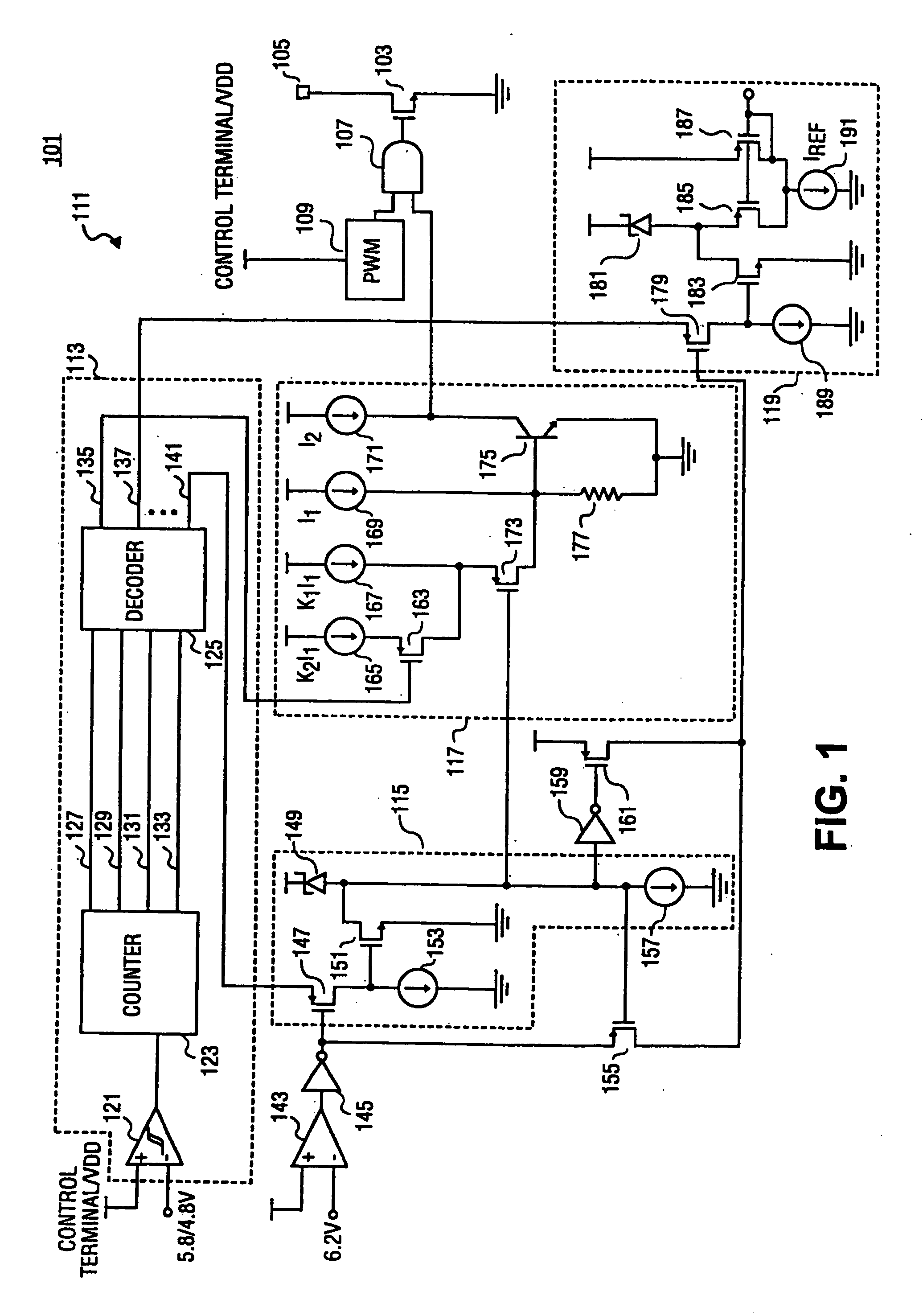

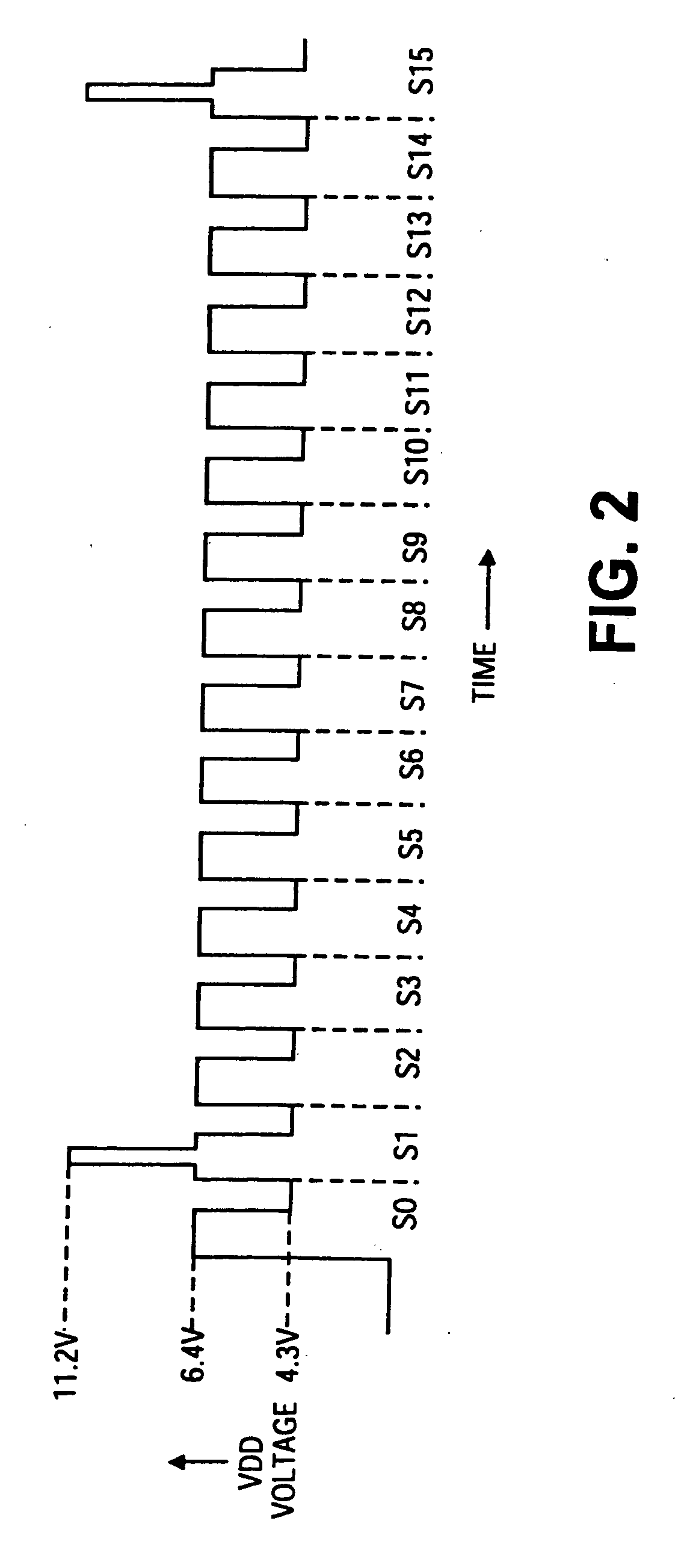

Method and apparatus providing final test and trimming for a power supply controller

A power supply controller having final test and trim circuitry. In one embodiment, a power supply controller for switched mode power supply includes a selector circuit, a trim circuit, a shutdown circuit and a disable circuit. The trim circuit includes a programmable circuit connection that can be selected by the selector circuit by toggling a voltage on an external terminal such as for example a power supply terminal, a control terminal or a function terminal of the power supply controller. The programmable circuit connection in the trim circuit can be programmed by applying a programming voltage to the external terminal. The shutdown circuit shuts down the power supply controller if the temperature rises above an over temperature threshold voltage. The shutdown circuit includes adjustment circuitry that can be used to test the shutdown circuit. The adjustment circuitry can adjust and reduce the over temperature threshold of the power supply controller. Thus, the power supply controller can be tested without having to actually heat the part. The disable circuit includes a programmable circuit connection, which when programmed prevents further trimming of power supply controller and prevents adjustment of the shutdown circuit over temperature threshold.

Owner:POWER INTEGRATIONS INC

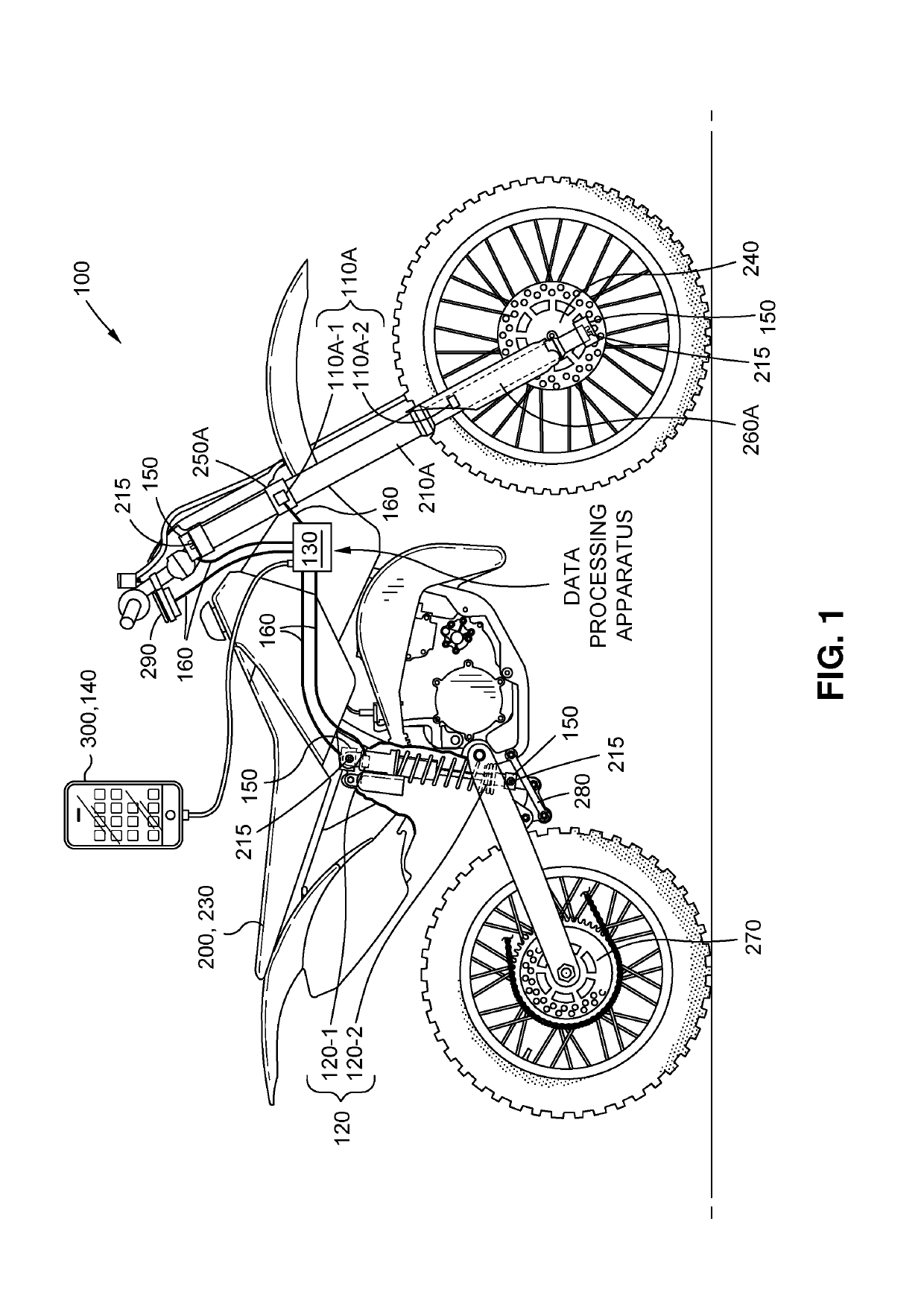

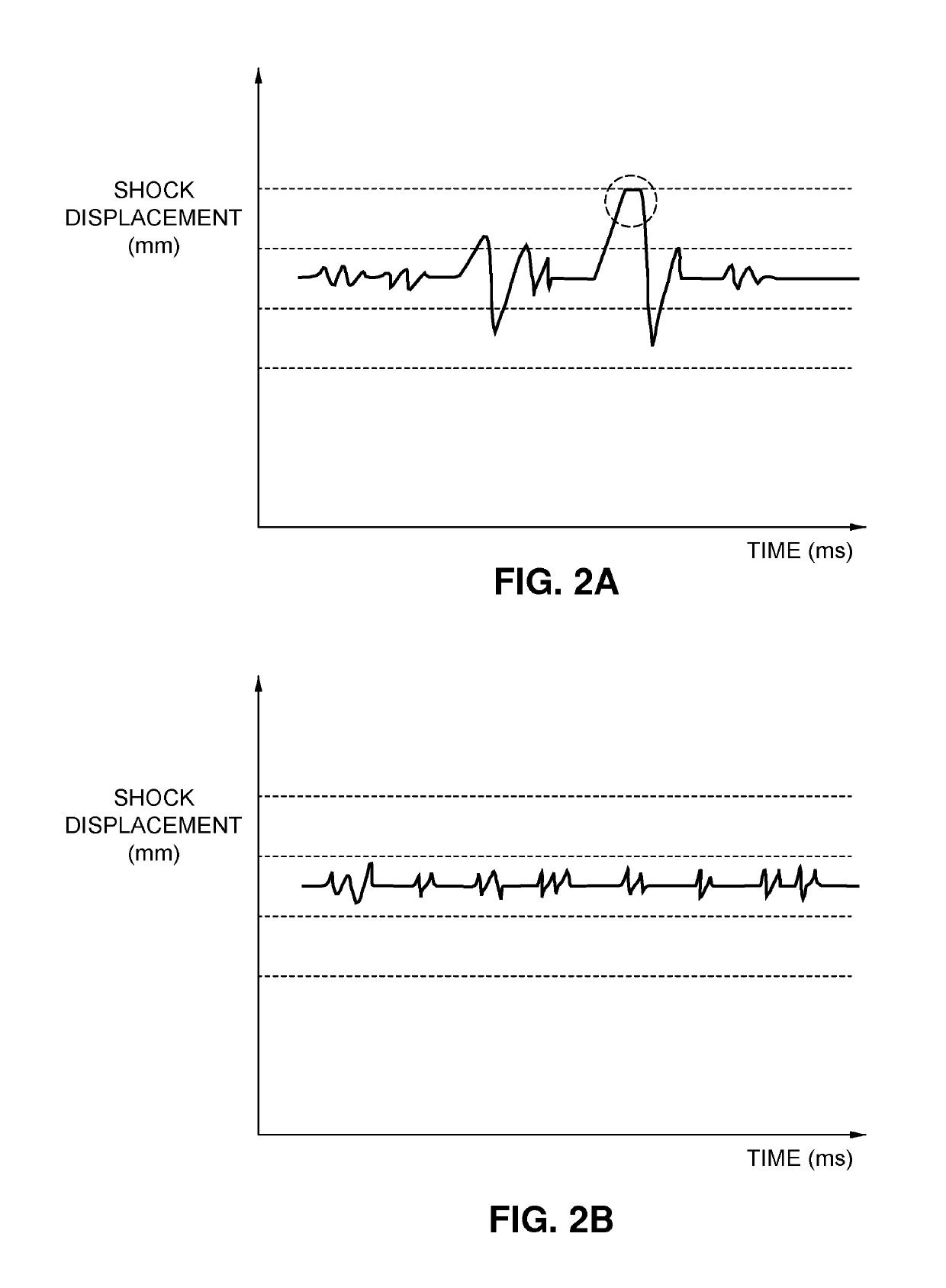

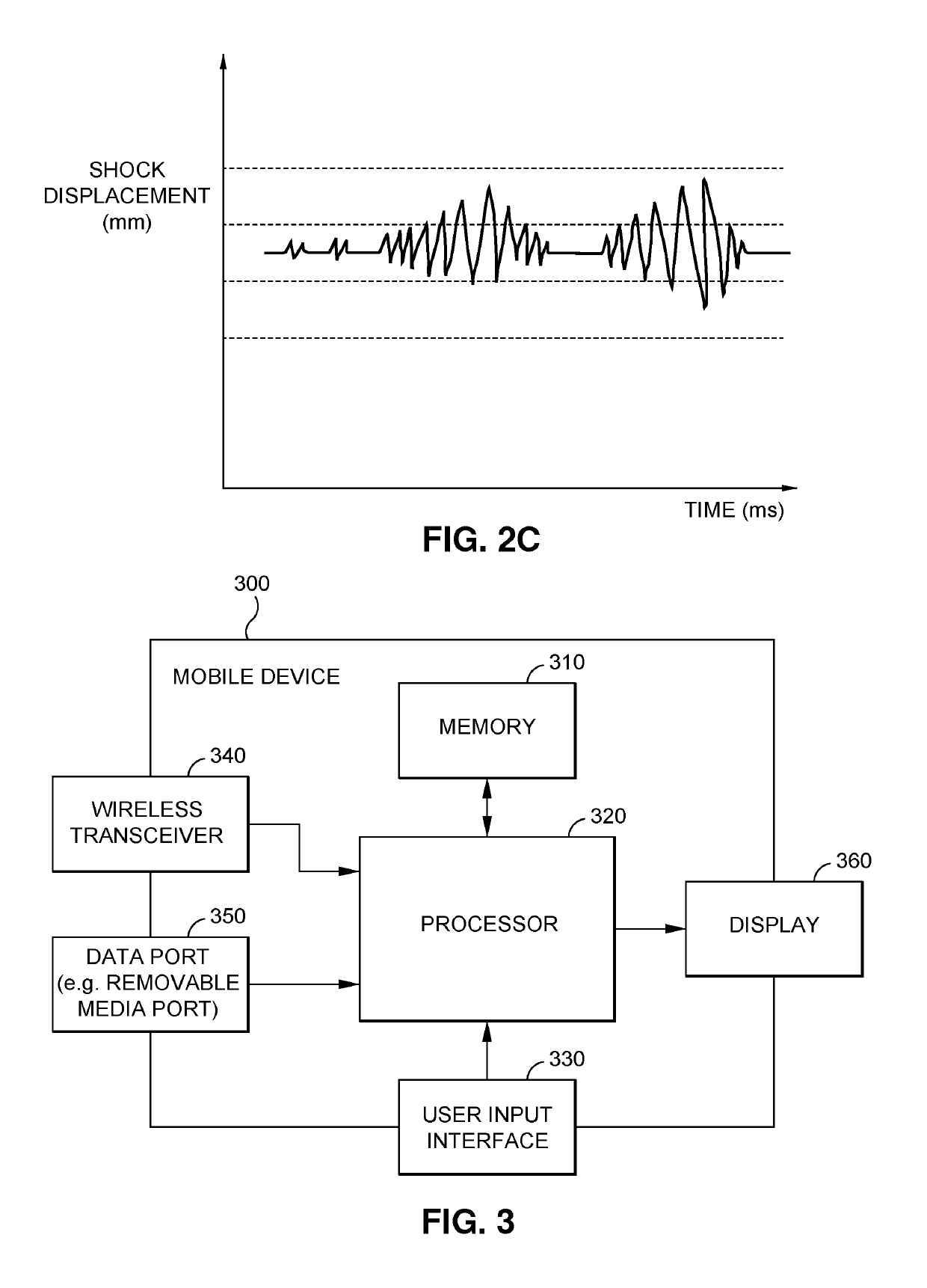

Off-road vehicle suspension monitoring and adjustment system

A suspension monitoring and adjustment system for an off-road vehicle includes a distance sensor arranged to measure shock displacement of a suspension of the vehicle. The system may include an output device configured to output shock displacement data generated by the distance sensor and a processor or programmable circuit operable to produce a visual representation of the shock displacement data output by the output device. The system may include a processor or programmable circuit operable to generate an adjustment signal based on shock displacement data generated by the distance sensor and a suspension adjuster arranged to adjust the suspension of the vehicle in response to the adjustment signal.

Owner:SHAW RONALD D +3

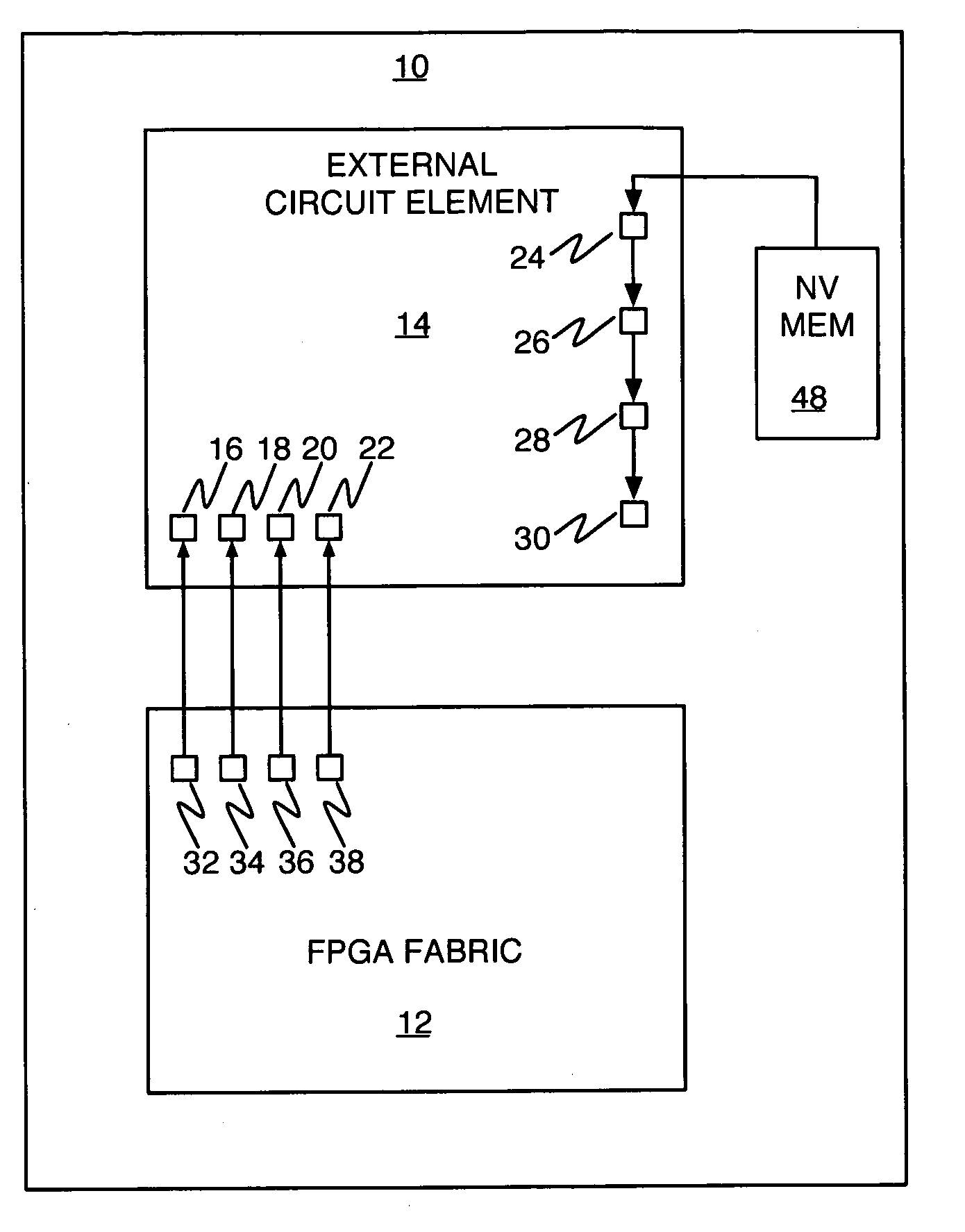

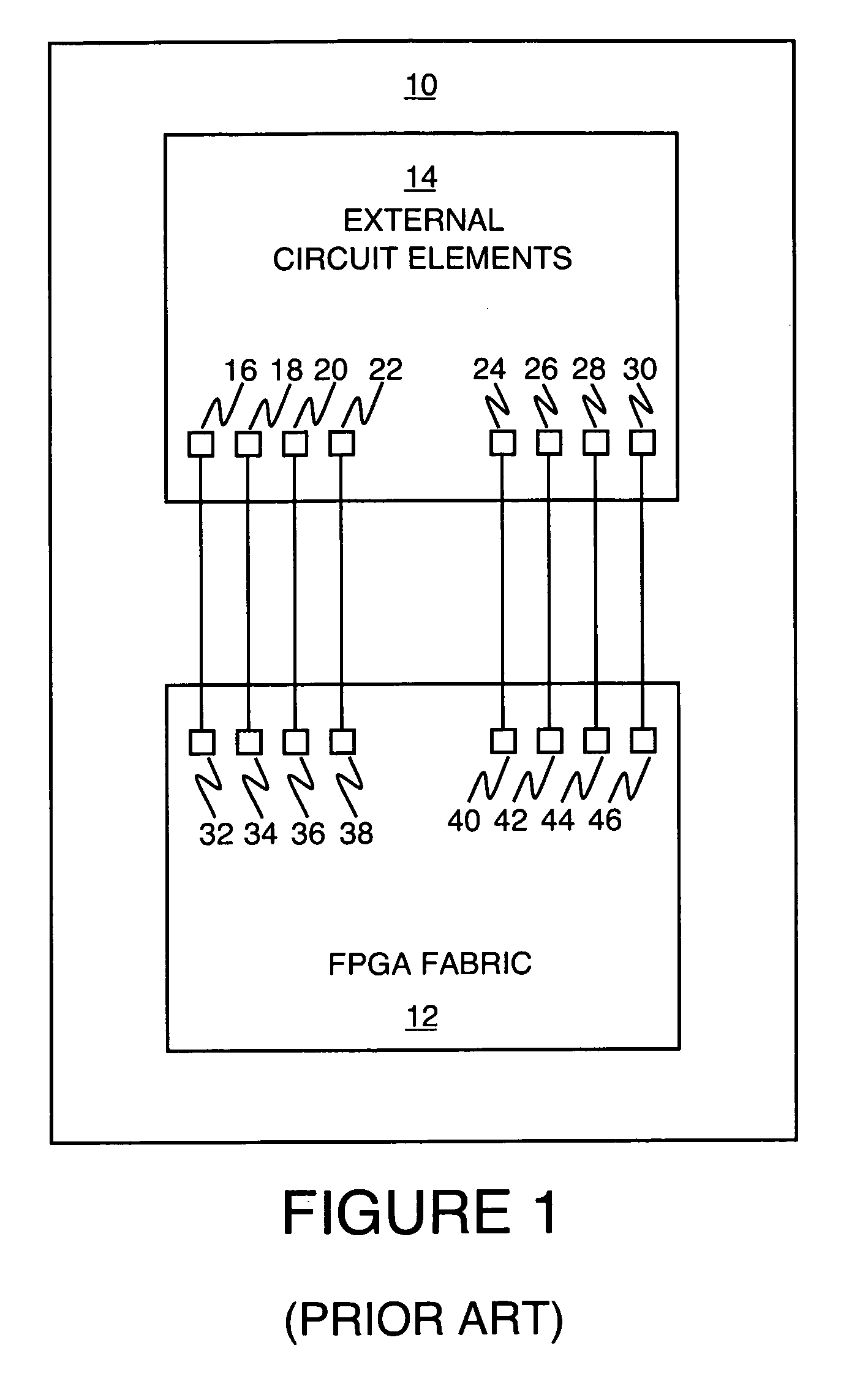

Non-volatile memory configuration scheme for volatile-memory-based programmable circuits in an FPGA

ActiveUS7112993B2Solid-state devicesLogic circuits using elementary logic circuit componentsComputer architectureProcessor register

A non-volatile memory configuration scheme is disclosed for volatile-memory-based programmable circuits in a programmable integrated circuit that includes an FPGA fabric, a plurality of first configurable circuit elements external to the FPGA fabric, and a plurality of second configurable circuit elements external to the FPGA fabric. A plurality of distributed configuration non-volatile memory cells is disposed in the FPGA, each one of the distributed configuration non-volatile memory cells coupled to a different one of the plurality of first configurable circuit elements. A non-volatile memory array stores configuration information for the second configurable circuit elements. A plurality of register cells is disposed with the second configurable circuit elements and is coupleable to the non-volatile memory array, each one of the register cells coupled to a different one of the plurality of second configurable circuit elements.

Owner:MICROSEMI SOC

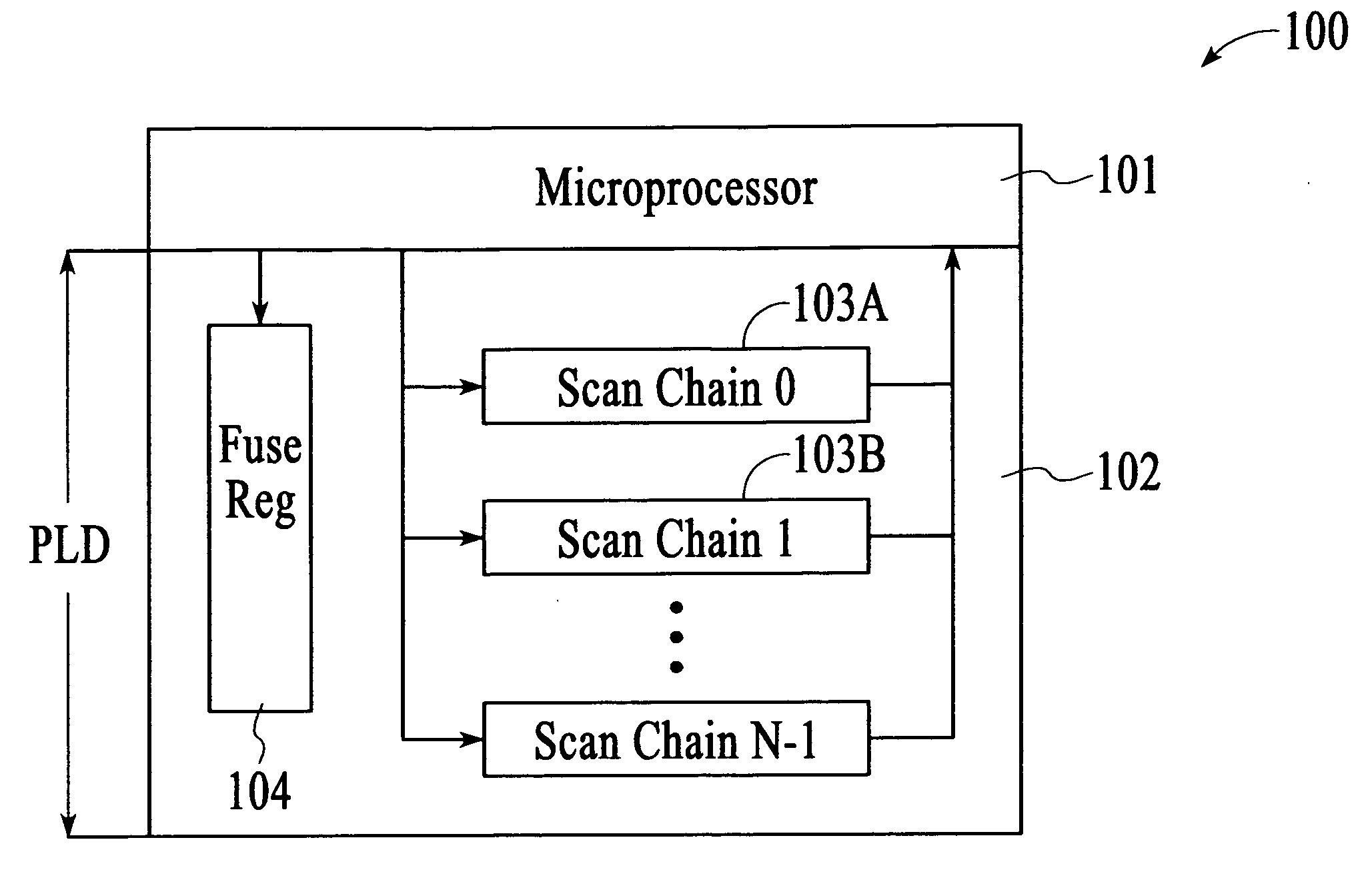

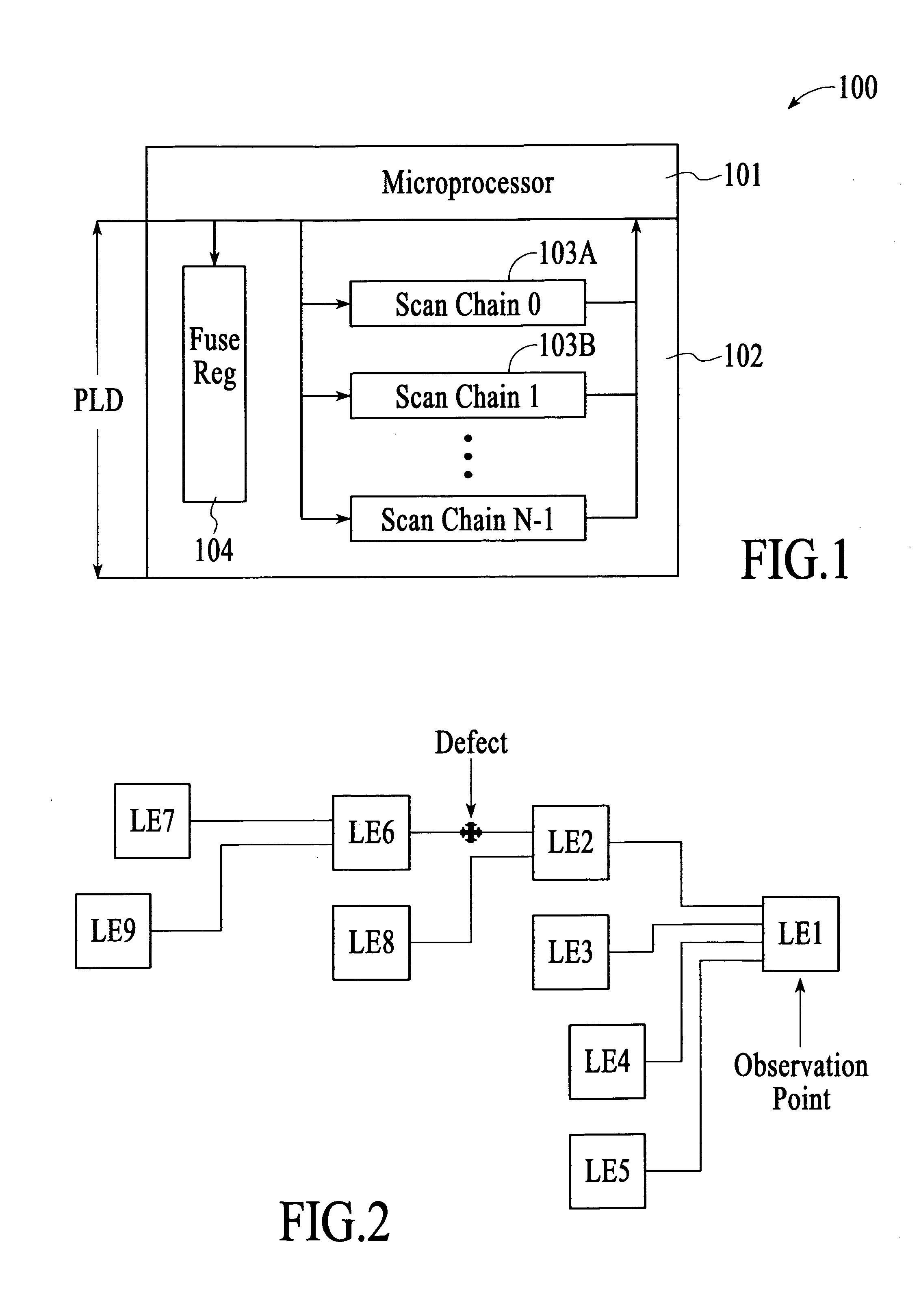

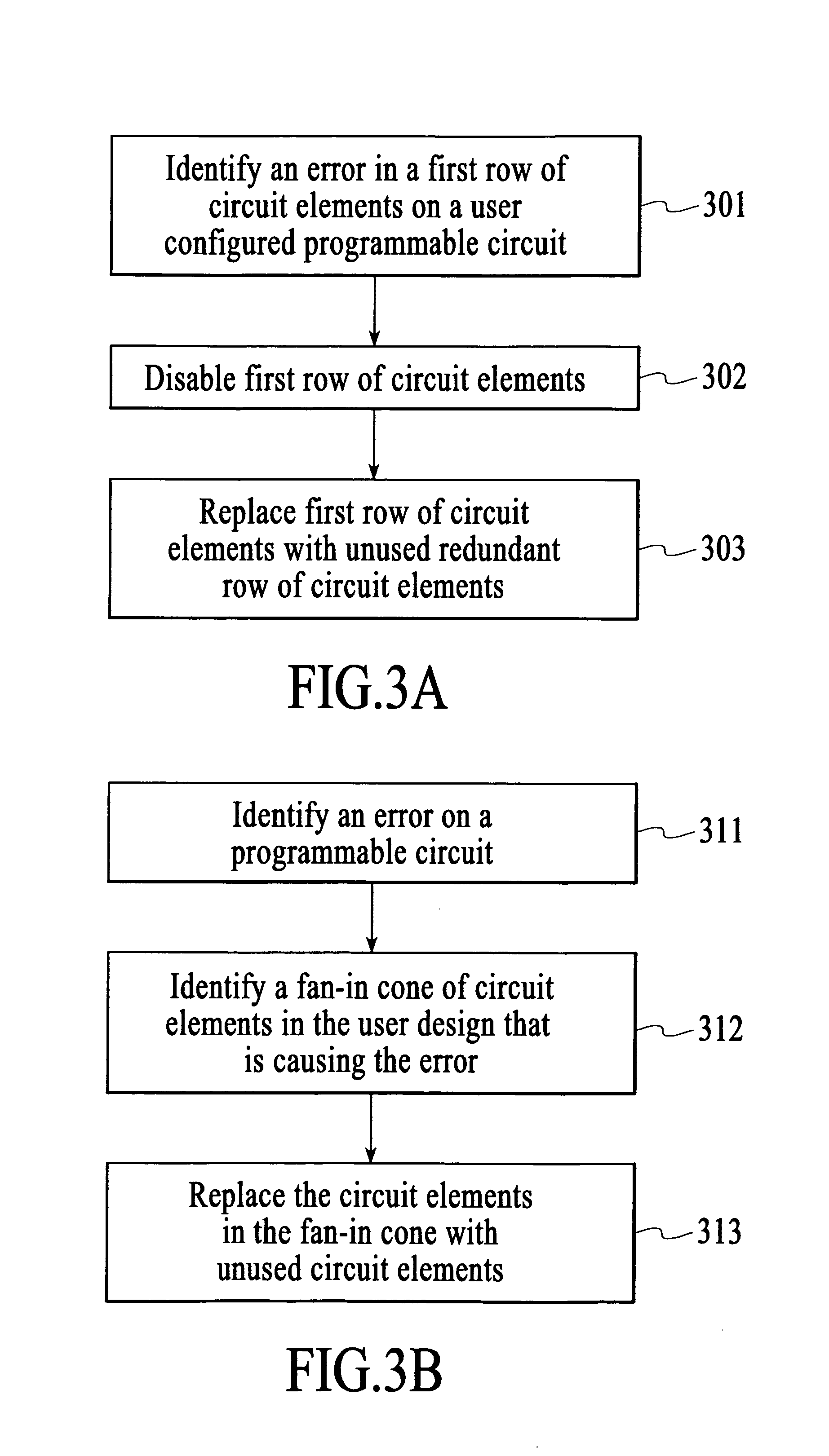

Failure isolation and repair techniques for integrated circuits

InactiveUS7111213B1Reduce the amount requiredElectronic circuit testingError detection/correctionProgrammable circuitsIntegrated circuit layout

Techniques for isolating and repairing failures on a programmable circuit are provided. An error on programmable circuit may be caused by a defect on the chip. The error is located, and the circuit elements effected by the defect are isolated. By identifying operable circuit elements near the defect, the number of circuit elements that are adversely effected by the defected can be narrowed down. The failed circuit elements adversely effected by the defect are then shut down and cut off from the rest of the programmable circuit. The functionality performed by the failed circuit elements is transferred to an unused portion of the programmable circuit. The se techniques reduce the amount of circuit elements that need to be shut down as a result of a defect on a programmable circuit.

Owner:ALTERA CORP

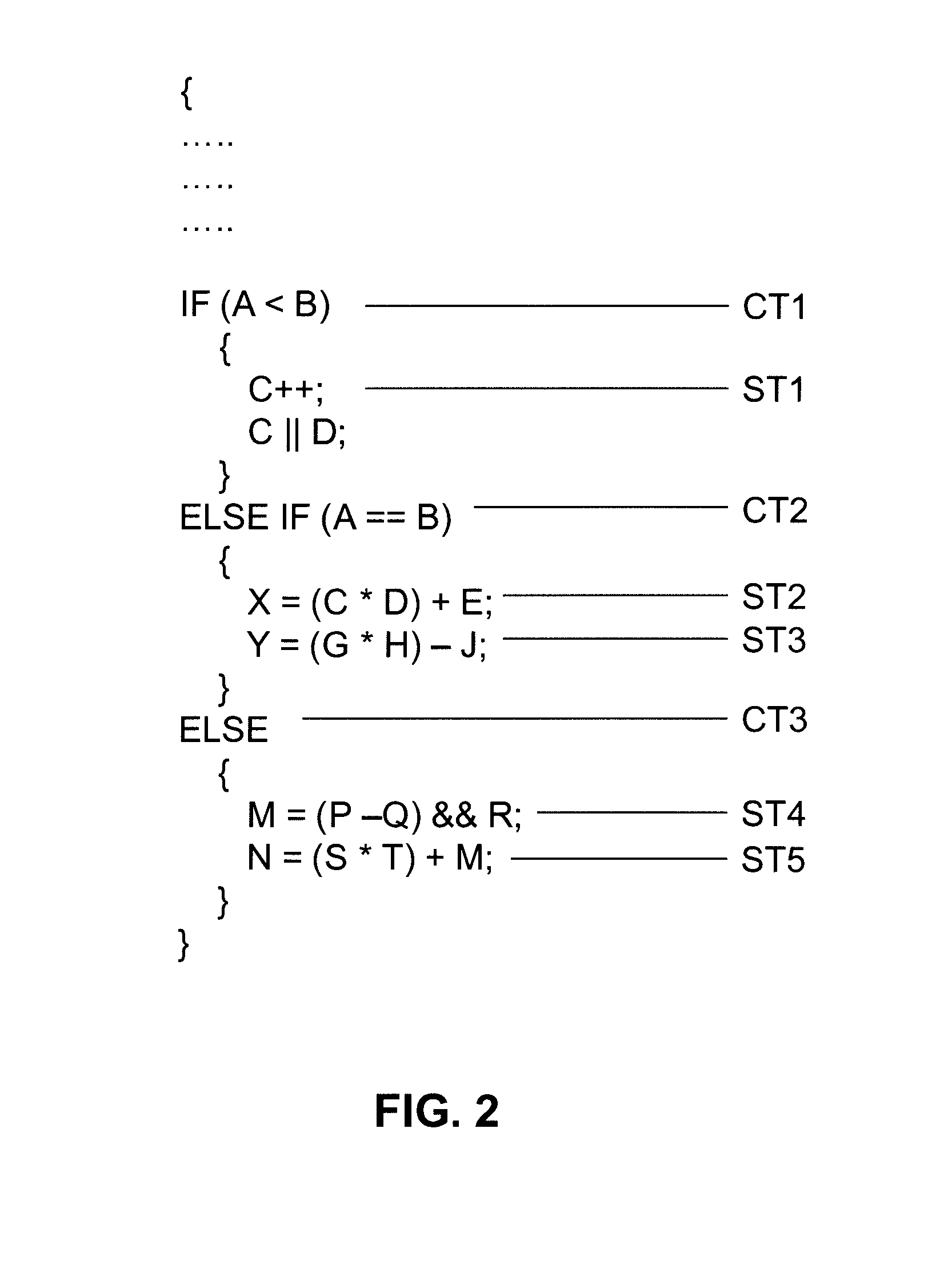

Multithreaded processor array with heterogeneous function blocks communicating tokens via self-routing switch fabrics

ActiveUS9158575B2Dataflow computersProgram initiation/switchingSelf routingStructure of Management Information

A shared resource multi-thread processor array wherein an array of heterogeneous function blocks are interconnected via a self-routing switch fabric, in which the individual function blocks have an associated switch port address. Each switch output port comprises a FIFO style memory that implements a plurality of separate queues. Thread queue empty flags are grouped using programmable circuit means to form self-synchronised threads. Data from different threads are passed to the various addressable function blocks in a predefined sequence in order to implement the desired function. The separate port queues allows data from different threads to share the same hardware resources and the reconfiguration of switch fabric addresses further enables the formation of different data-paths allowing the array to be configured for use in various applications.

Owner:SMITH GRAEME ROY

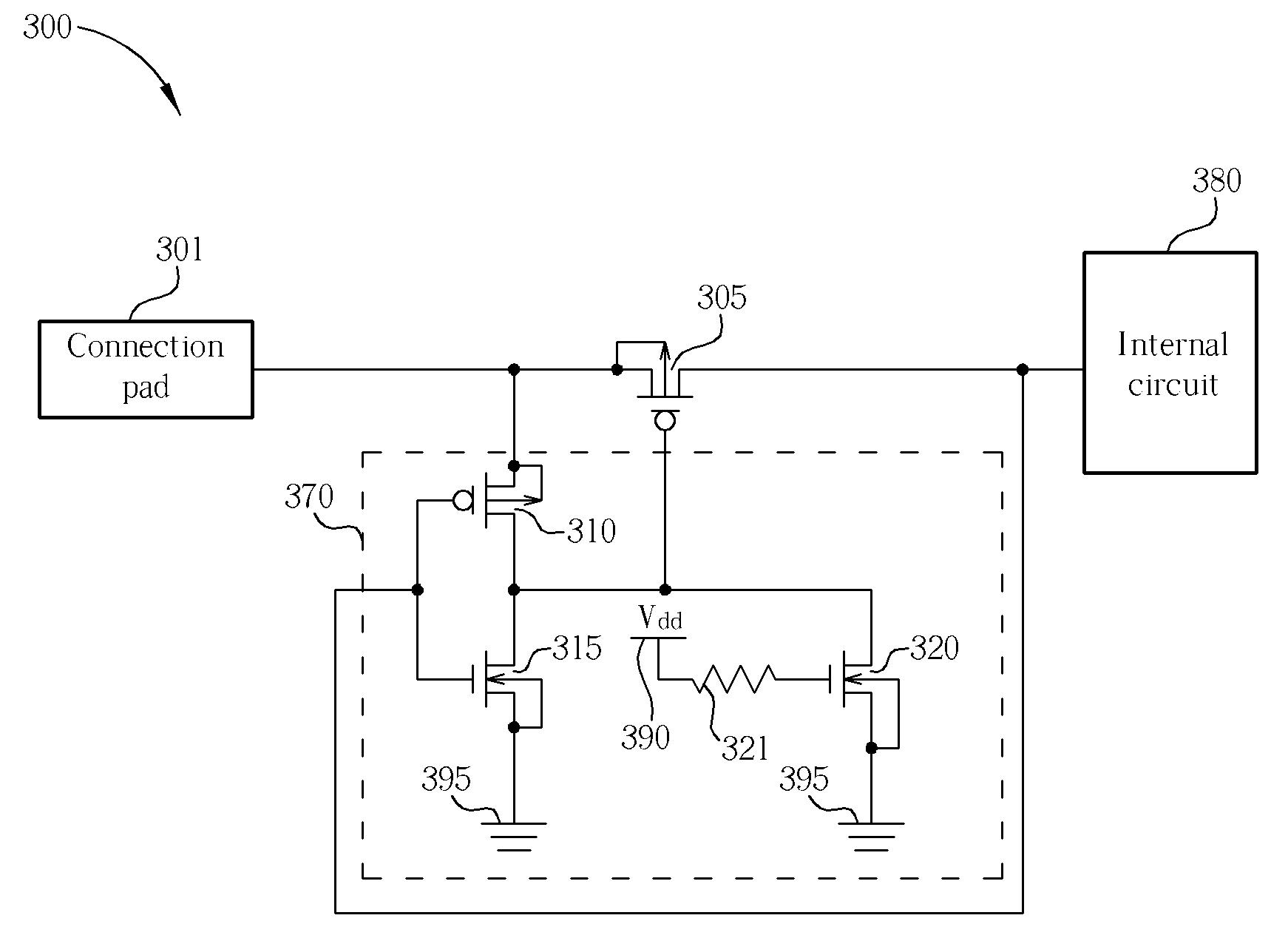

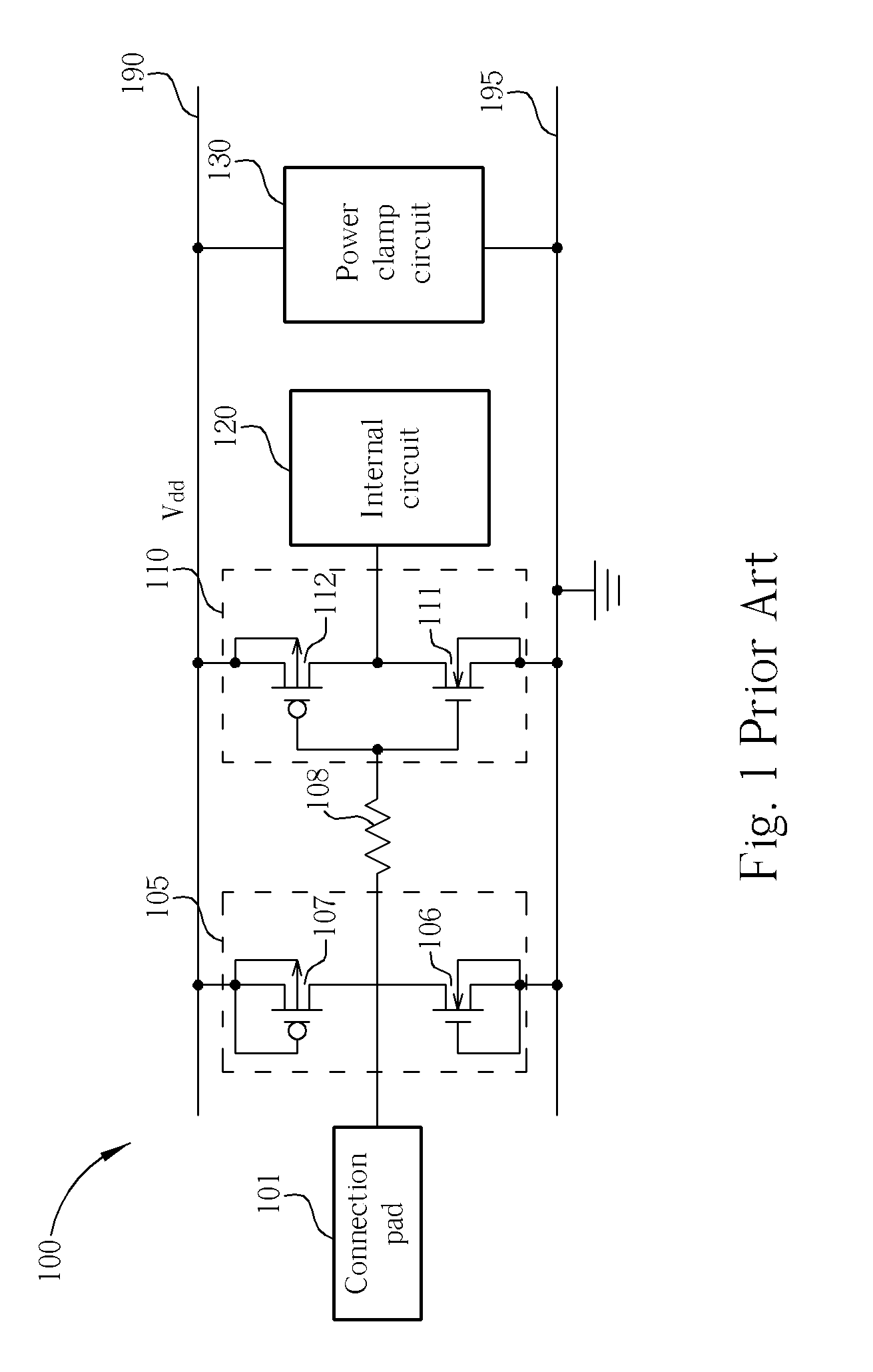

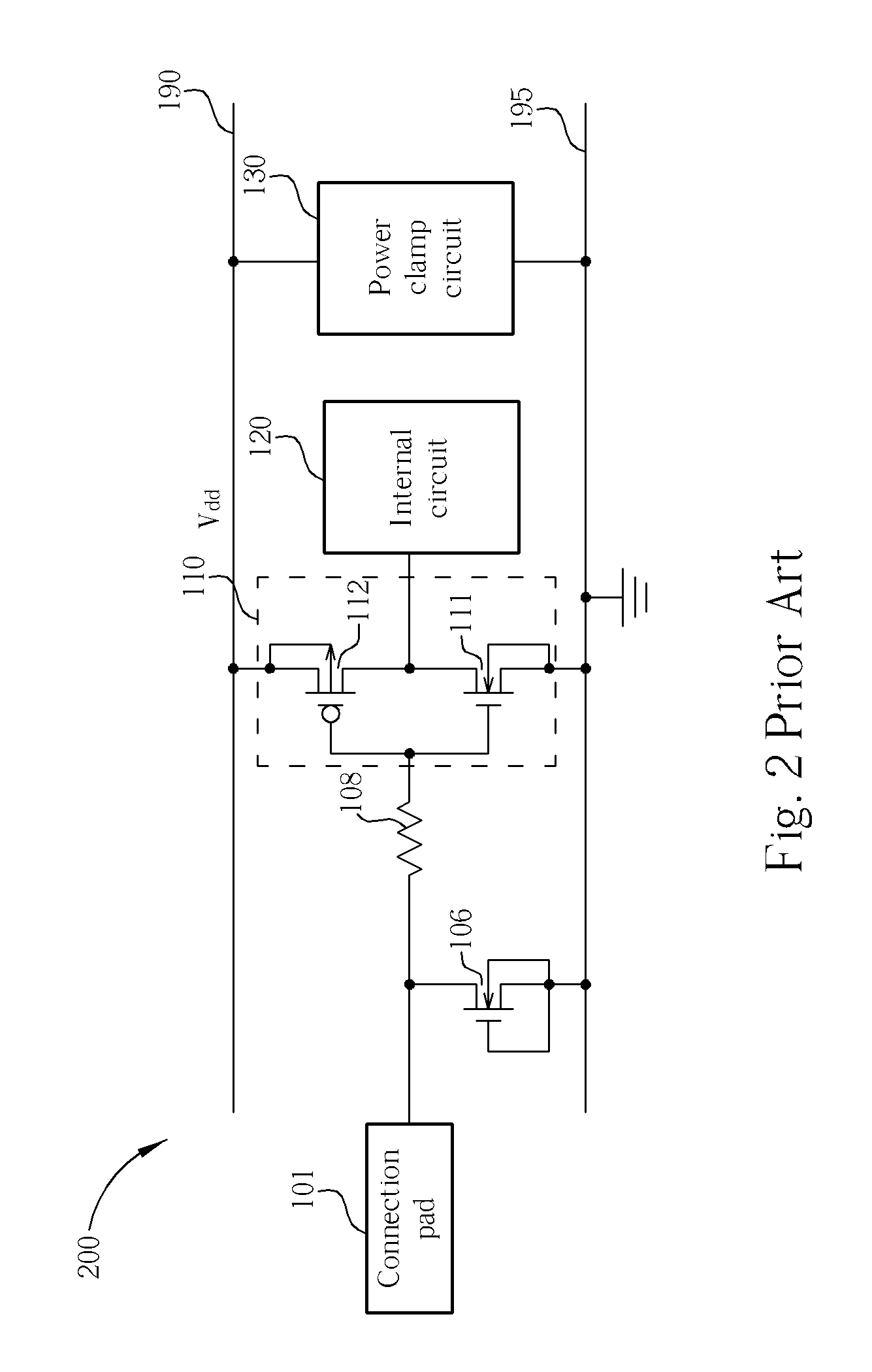

ESD avoiding circuits based on the ESD detectors in a feedback loop

InactiveUS20090091870A1Emergency protective arrangement detailsEmergency protective arrangements for limiting excess voltage/currentElectrostatic dischargeProgrammable circuits

When an electrostatic discharge event occurs to a connection pad of a chip, an electrostatic discharge detector layout in a feedback loop is able to detect an induced electrostatic discharge voltage for generating a control signal. A pass transistor can be turned off by the control signal for isolating the induced electrostatic discharge voltage, and the internal circuit of the chip can be protected from being damaged by the induced electrostatic discharge voltage. Furthermore, the designed circuit based on electrostatic discharge isolation technique for protecting the internal circuit of the chip is compatible with programmable circuits, and the connection pad can be furnished with burning signals or logic signals.

Owner:EMEMORY TECH INC

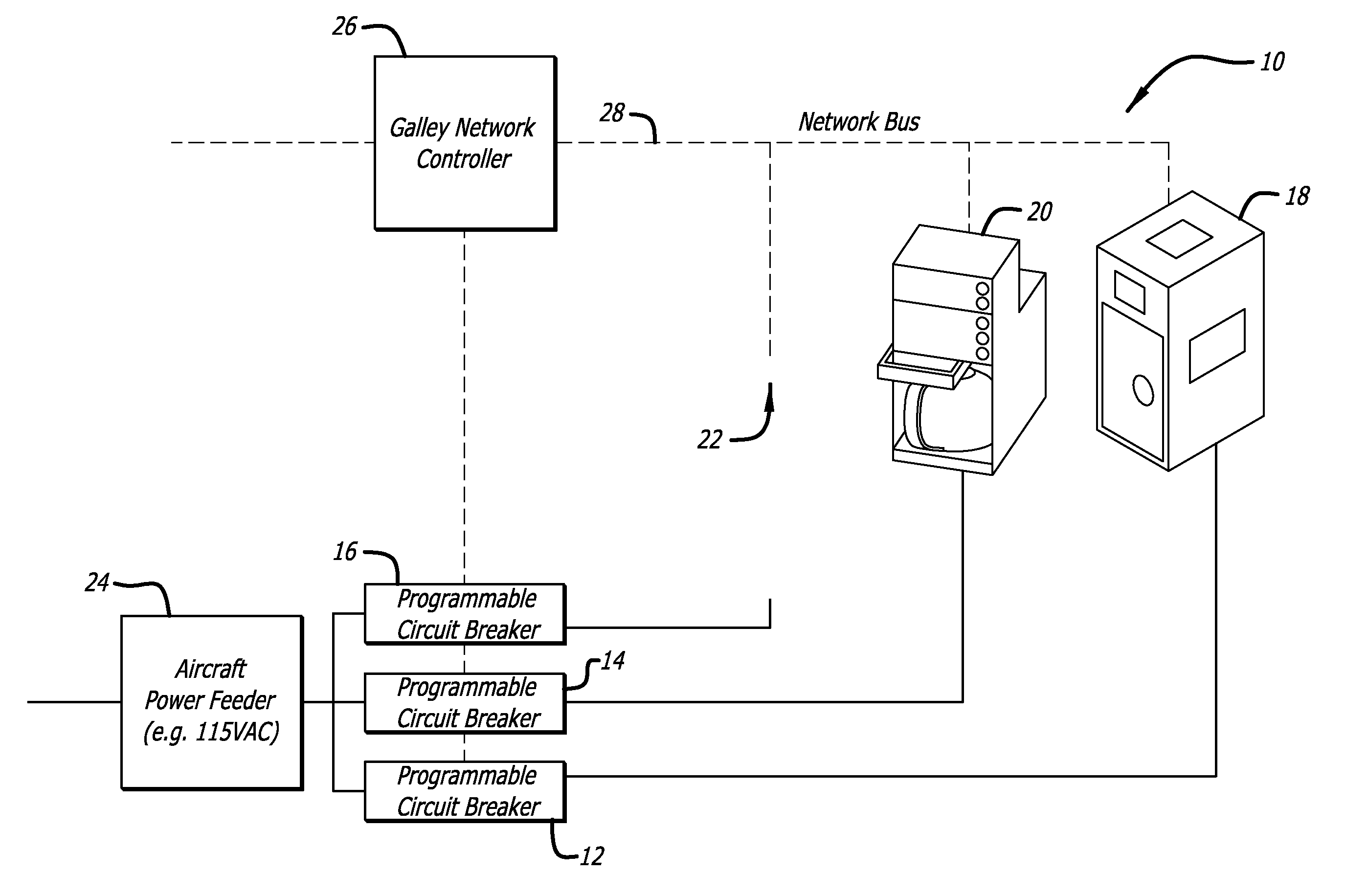

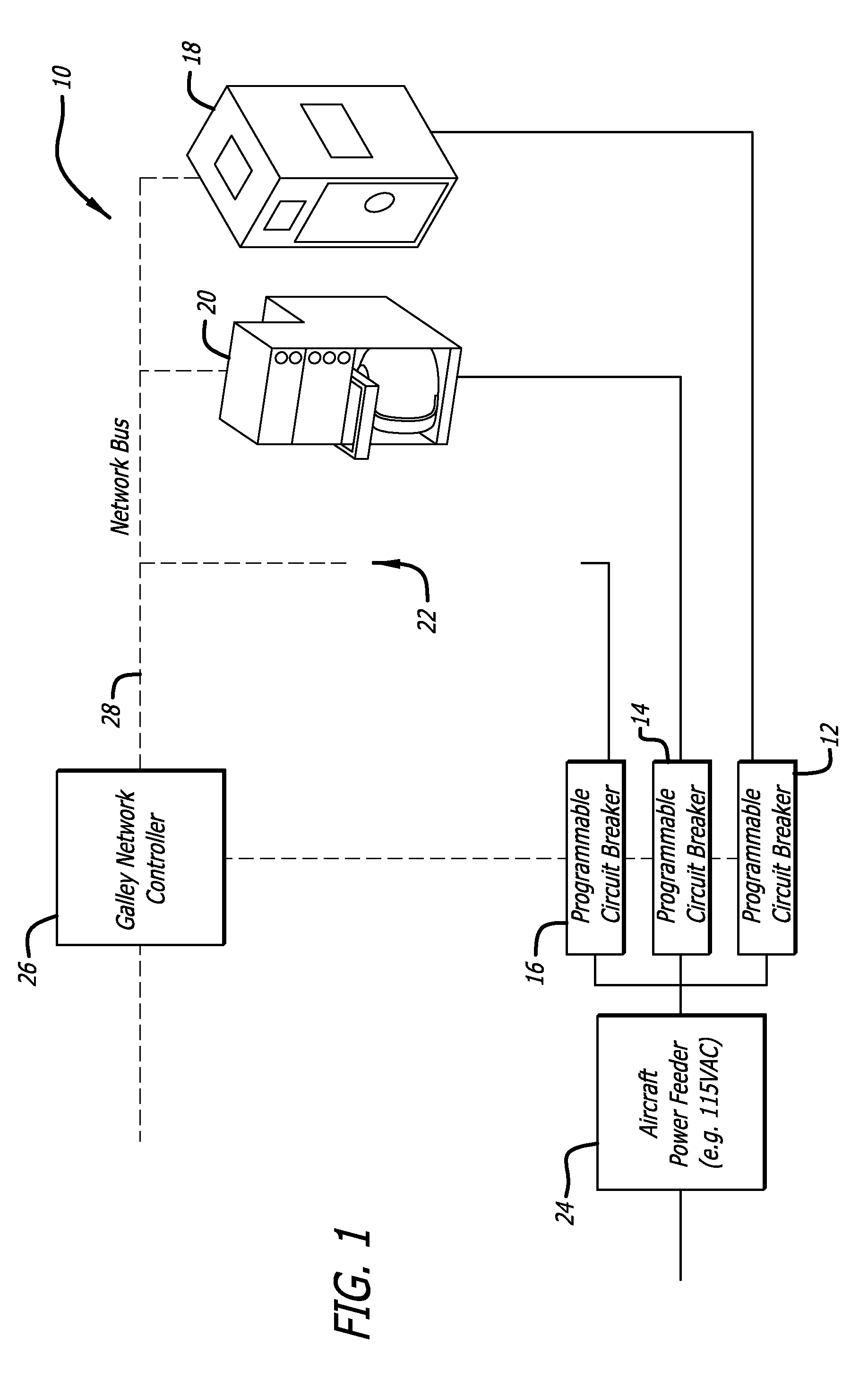

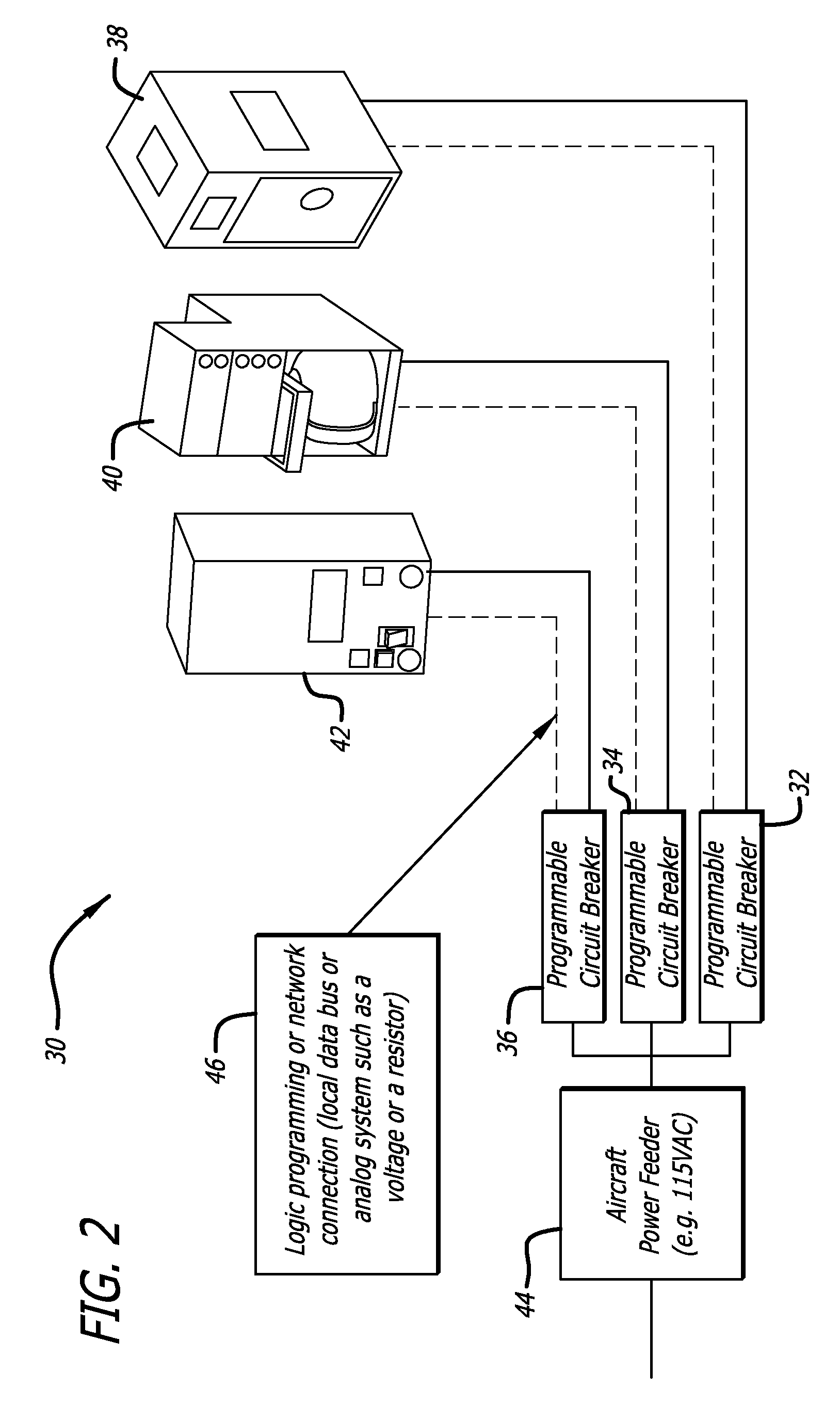

Adaptive power management system for aircraft galleys

The adaptive power management system for aircraft galleys includes one or more programmable circuit breakers for corresponding interchangeable aircraft galley inserts. Current rating settings of the programmable circuit breakers can be changed by direct interrogation by a galley network controller, which can also automatically switch selected circuit breakers to open to shut down the power supply to an entire galley complex or individual galley inserts, as needed, or by a passive signal.

Owner:BE INTPROP

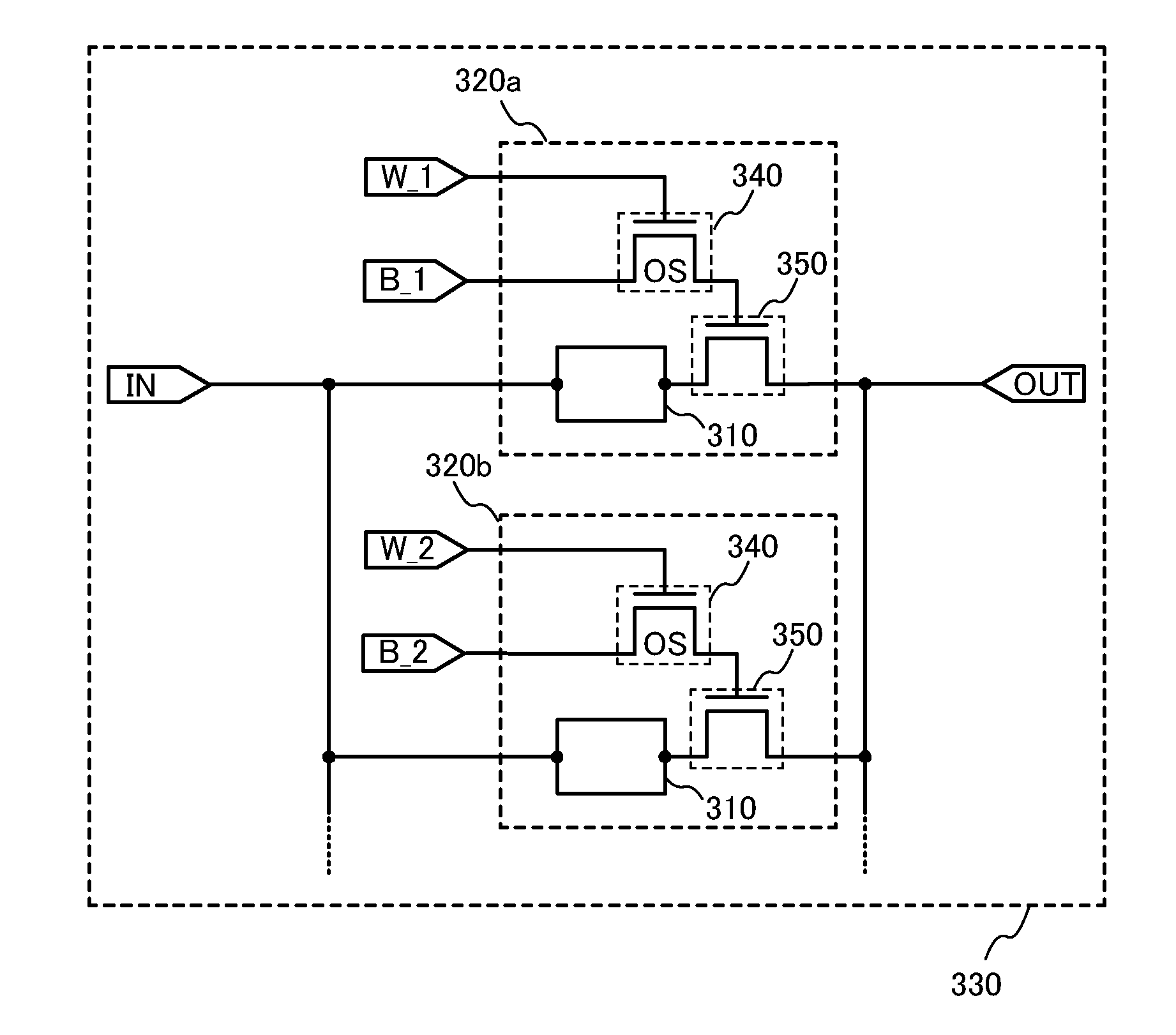

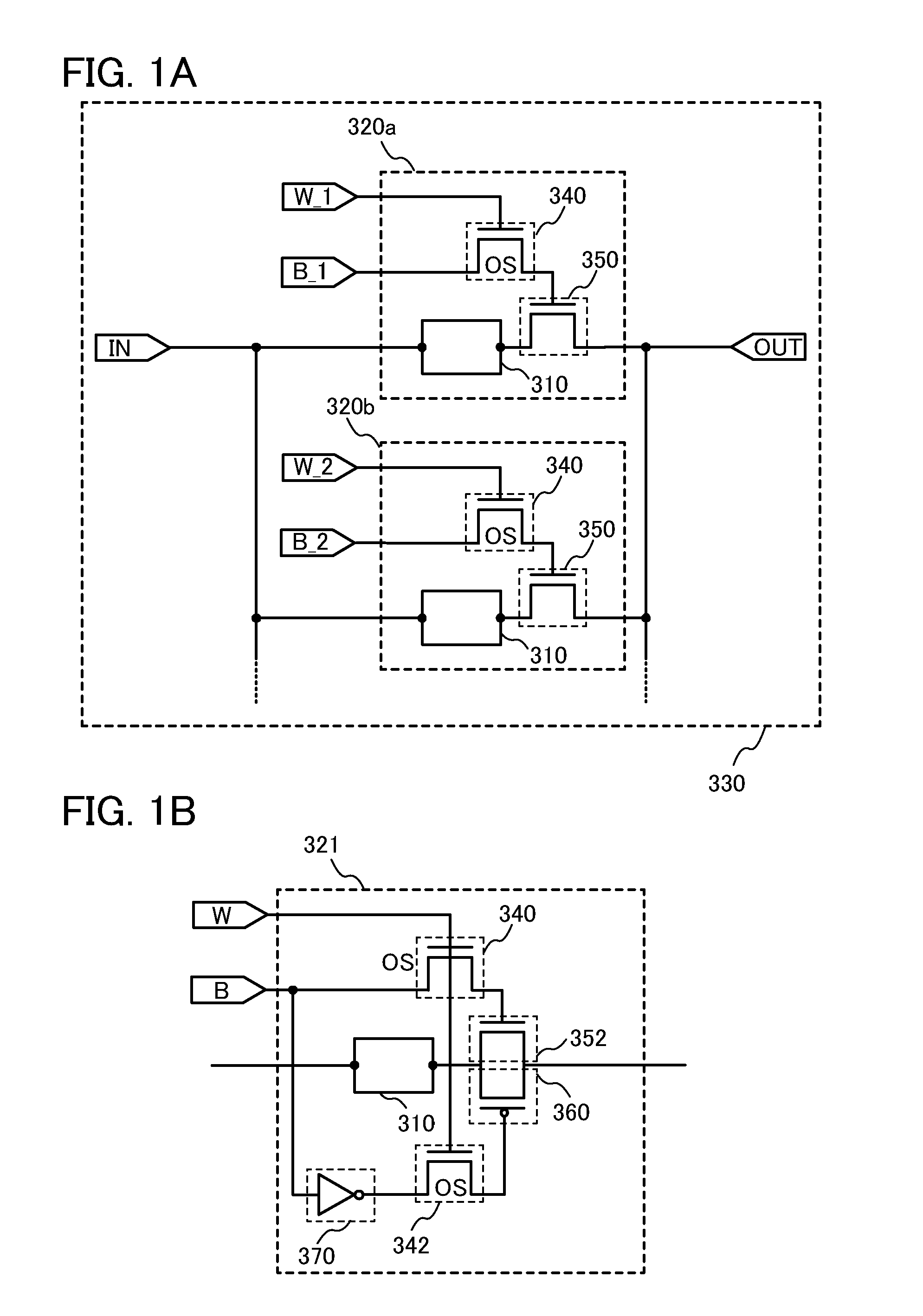

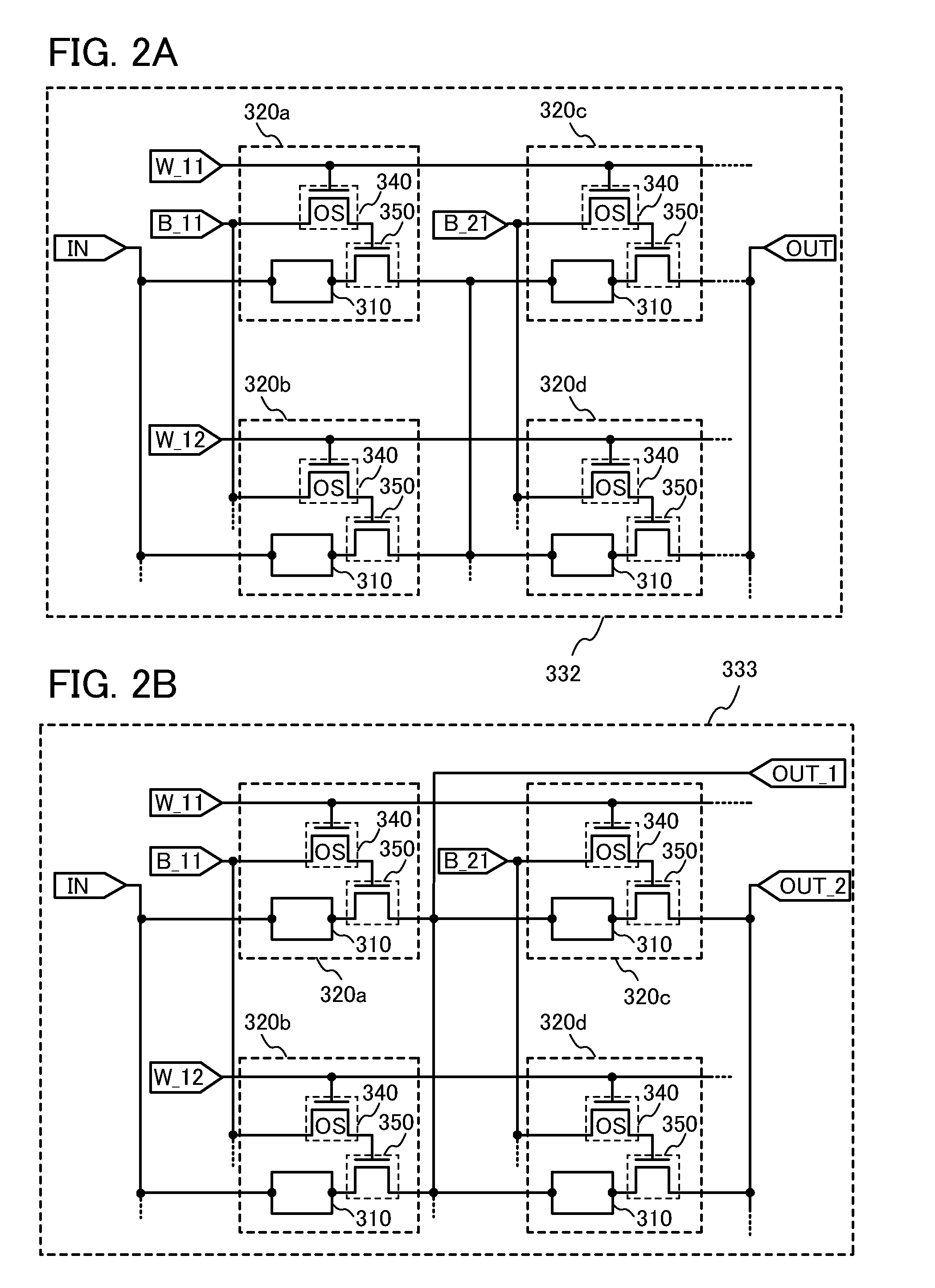

Semiconductor device

InactiveUS20120293203A1Low costImprove design flexibilitySolid-state devicesRead-only memoriesEngineeringProgrammable circuits

A programmable analog device in which data can be held even when supply of a power supply potential is stopped. The programmable circuit includes unit cells connected in parallel or in series, and each of the unit cells includes an analog element. A conduction state of each of the unit cells is changed between an on state and an off state. Each of the unit cells includes, as a switch of the unit cell, a first transistor having a sufficiently low off-state current and a second transistor, a gate electrode of the second transistor being electrically connected to a source or drain electrode of the first transistor. The conduction state of the unit cell is controlled with a potential of the gate electrode of the second transistor, which can be kept even when no power is supplied thanks to the low off-state current of the first transistor.

Owner:SEMICON ENERGY LAB CO LTD

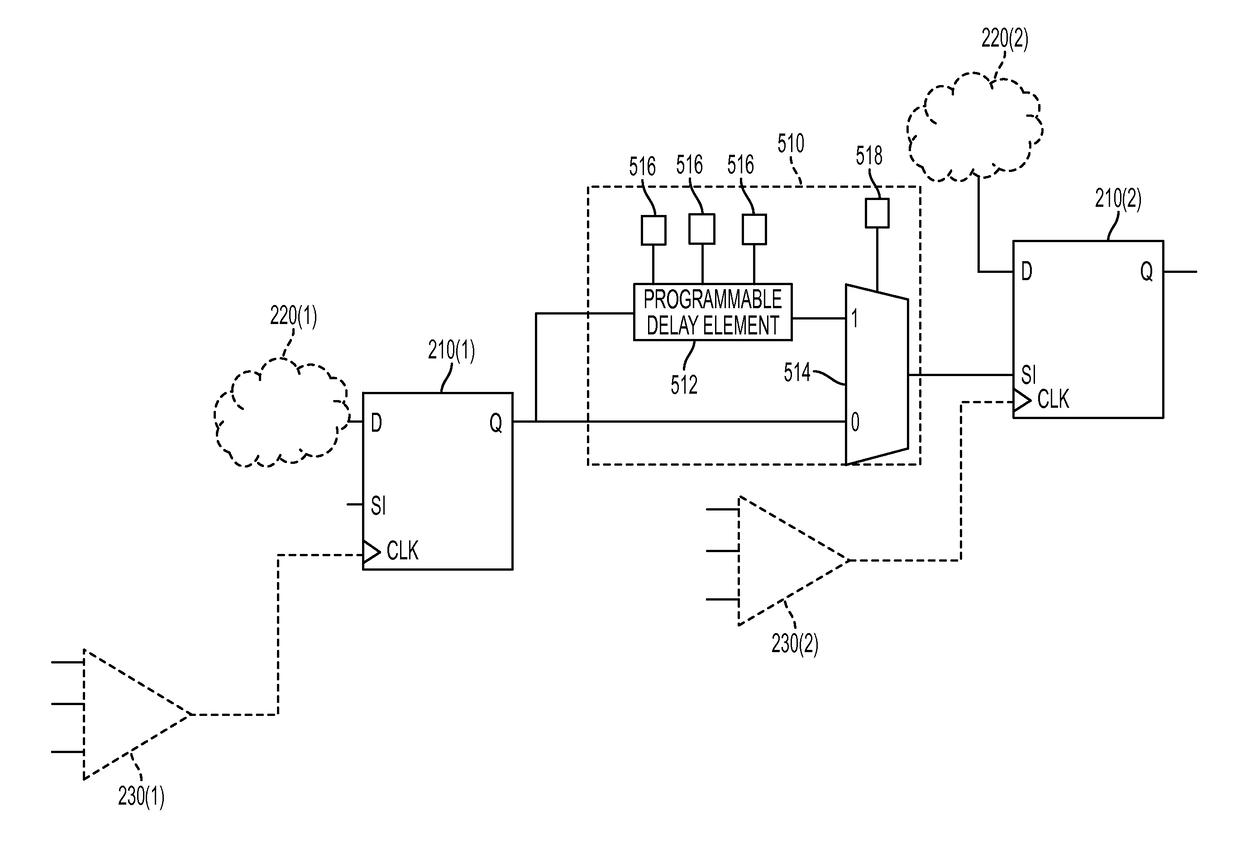

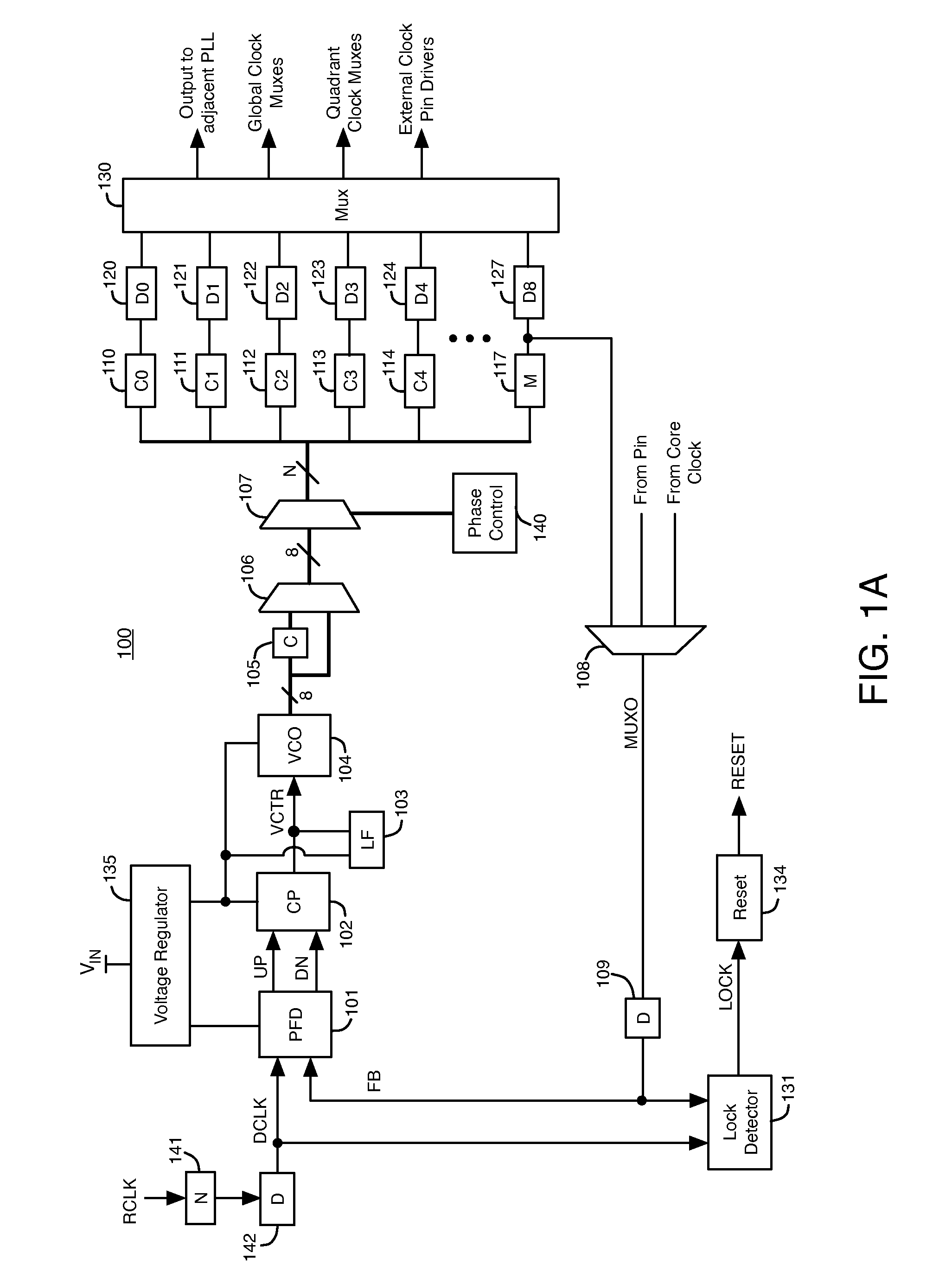

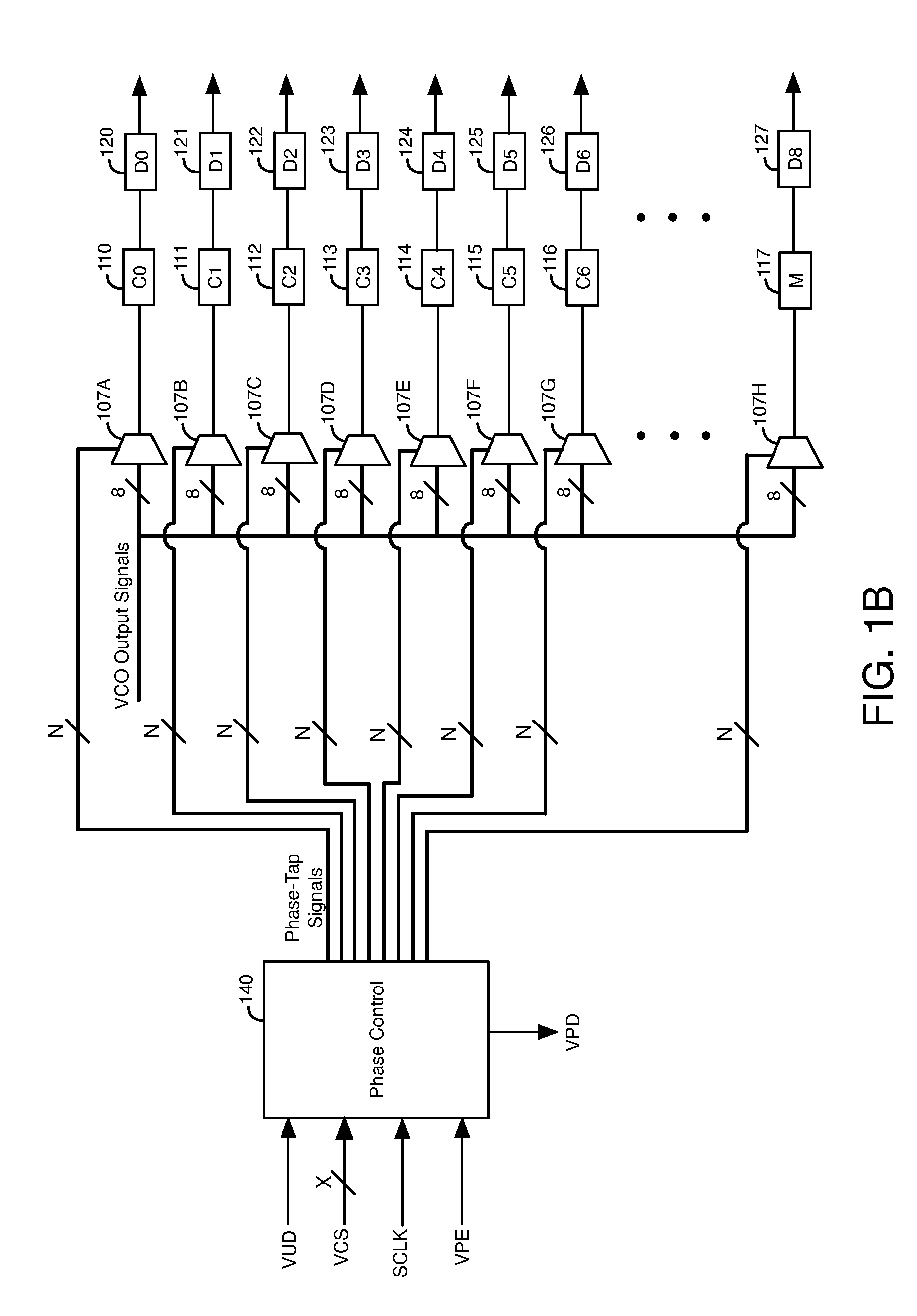

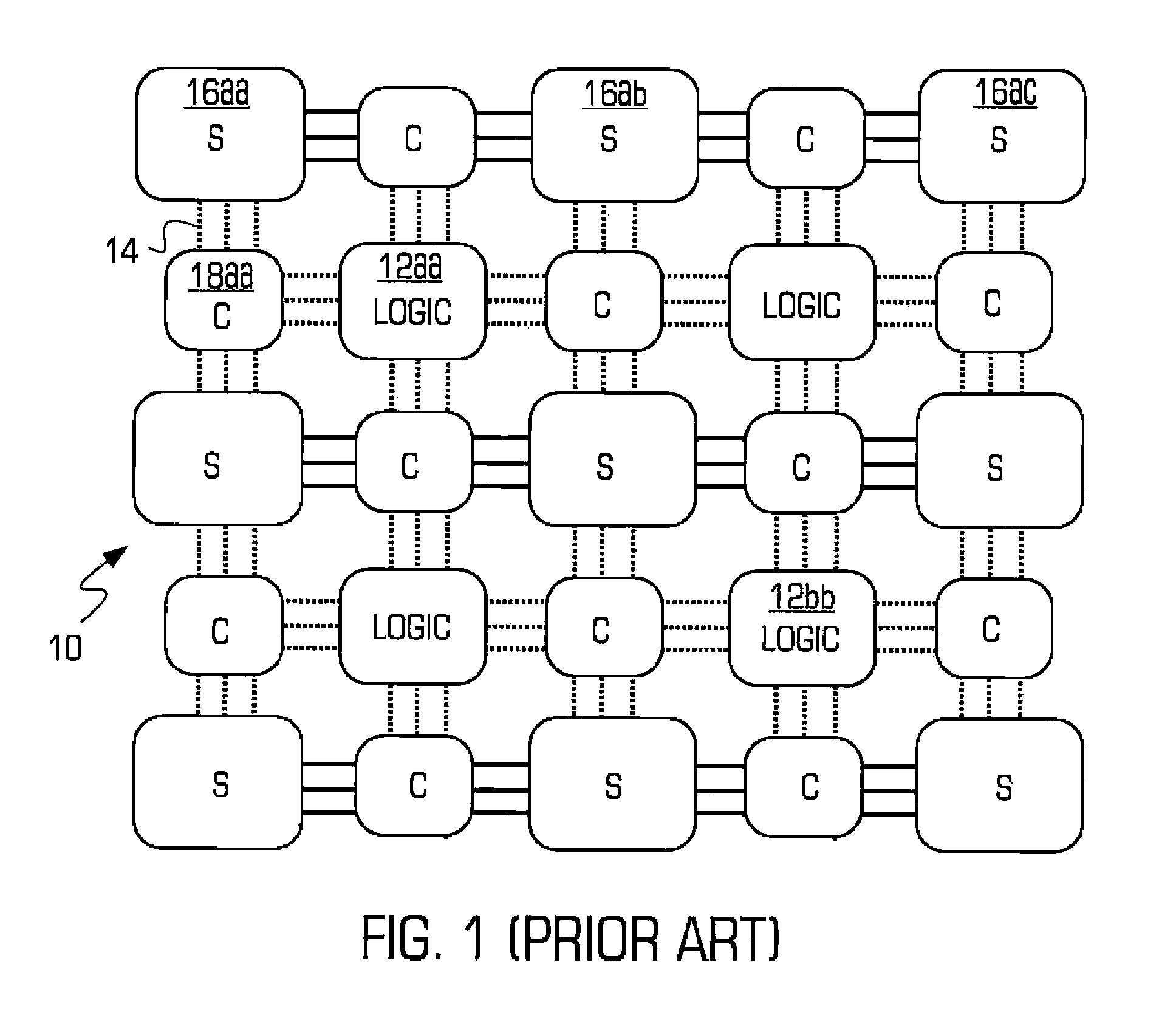

Techniques for reconfiguring programmable circuit blocks

InactiveUS7532029B1Pulse automatic controlLogic circuits using elementary logic circuit componentsPhase shiftedProcessor register

Techniques are provided for dynamically reconfiguring programmable circuit blocks on integrated circuits during user mode. First configuration bits are loaded from first configuration scan registers into second configuration scan registers during configuration mode. The first configuration bits are used to configure programmable settings of a programmable circuit block. During user mode, second configuration bits are transmitted from a pin to the second configuration scan registers without transferring the second configuration bits through the first configuration scan registers. The second configuration bits are used to reconfigure the programmable settings of the programmable circuit block during the user mode. Also, phase shift circuitry can dynamically shift the phase of an output clock signal by selecting a different input clock signal. The phase shift circuitry has a delay circuit that allows the phase of a high frequency clock signal to be shifted without causing glitches in the clock signal.

Owner:ALTERA CORP

Software protection

ActiveUS20110307961A1Improved software protectionLow costDigital data processing detailsInstruction analysisParallel computingProgrammable circuits

Owner:NXP BV

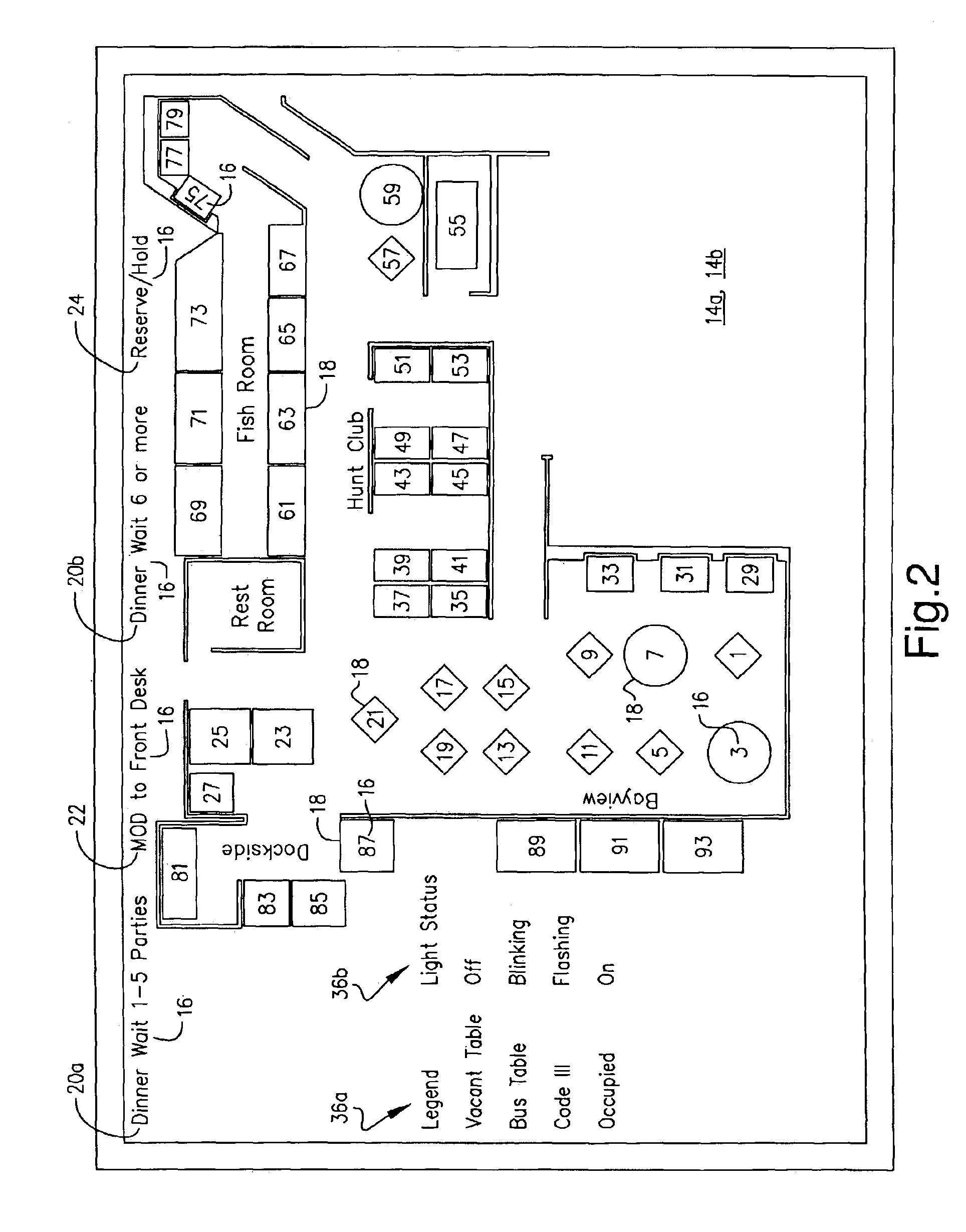

Restaurant table turn system network

InactiveUS6980088B2Function increaseMore costSignalling system detailsElectric/electromagnetic visible signallingControl systemProgrammable circuits

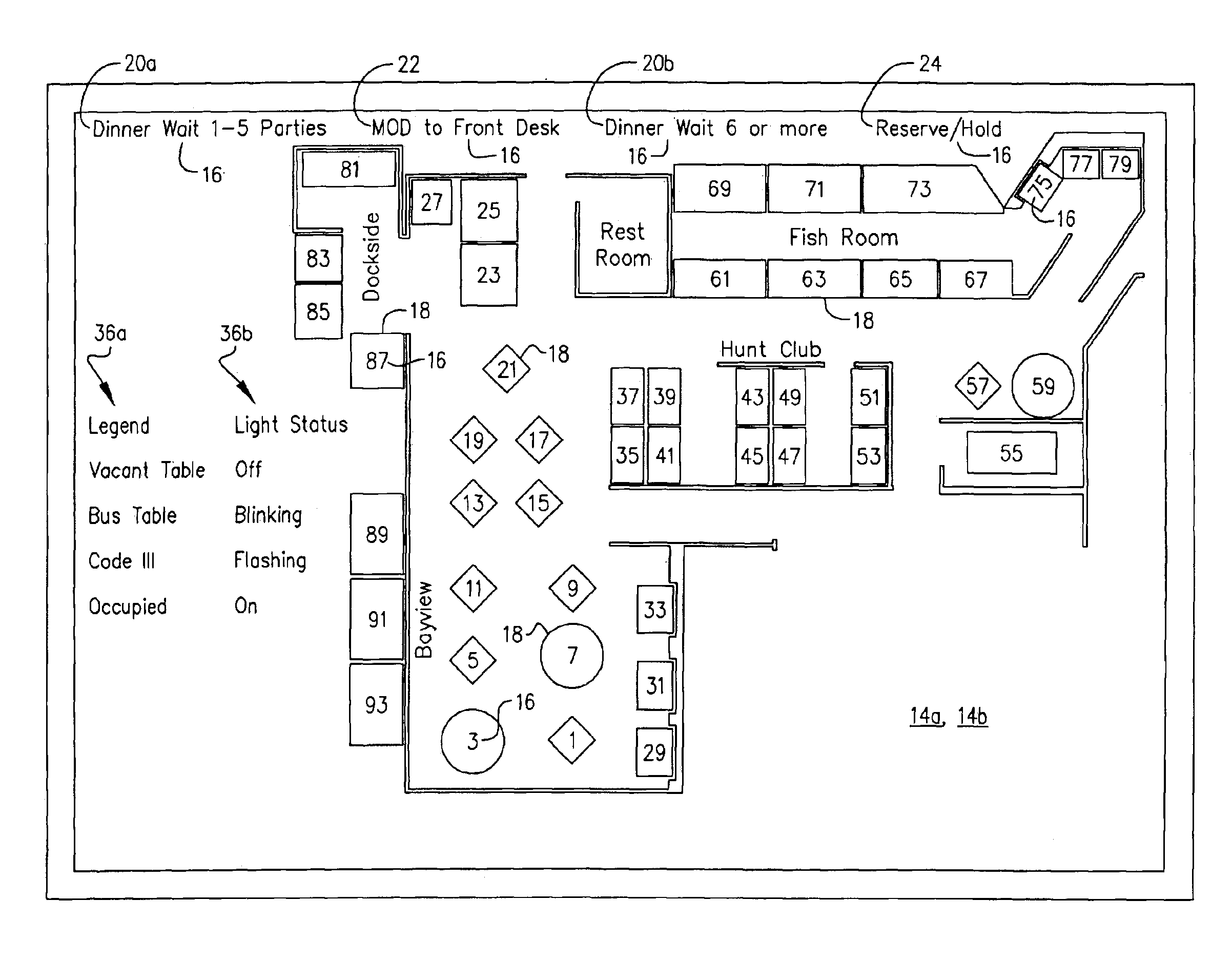

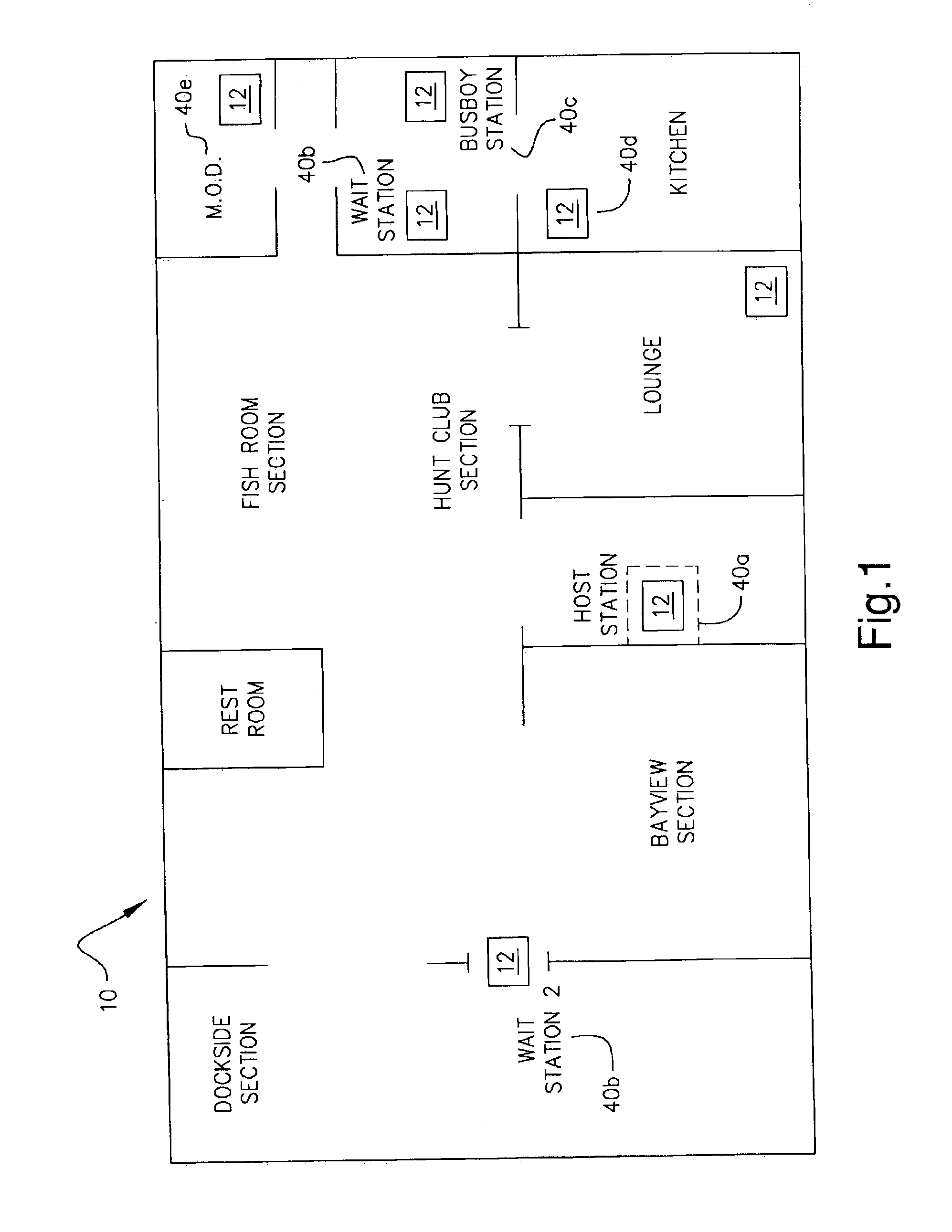

A restaurant table turn control and display system for providing real-time communication to staff personnel throughout key areas of a restaurant, comprising two or more monitoring consoles, each having a restaurant layout display having indicia representative of tables available for seating in the restaurant and for communicating to the staff other requirements or needs; a touch screen for activating desired status changes on the system; LED bulbs arranged in an underlying relationship to the indicia on the restaurant layout or software driven images depicted on the display screen, which can be a combination monitor and touch screen; and a controller circuit with programmable circuitry for operating and controlling the system, including providing status changes and communicating such status changes simultaneously to other monitoring consoles electrically operatively connected to said monitoring console.

Owner:RESTAURANT TECH CONCEPTS

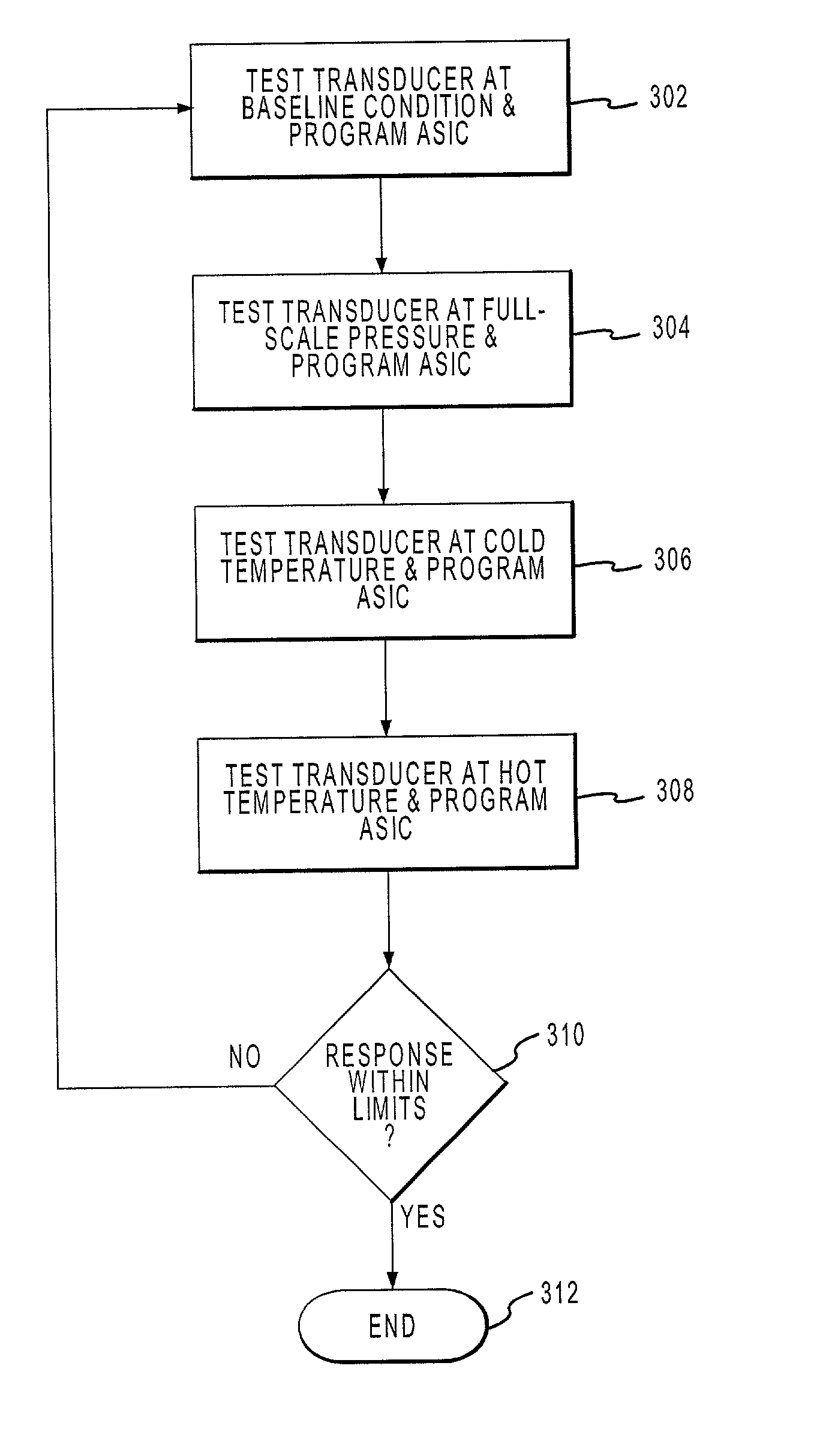

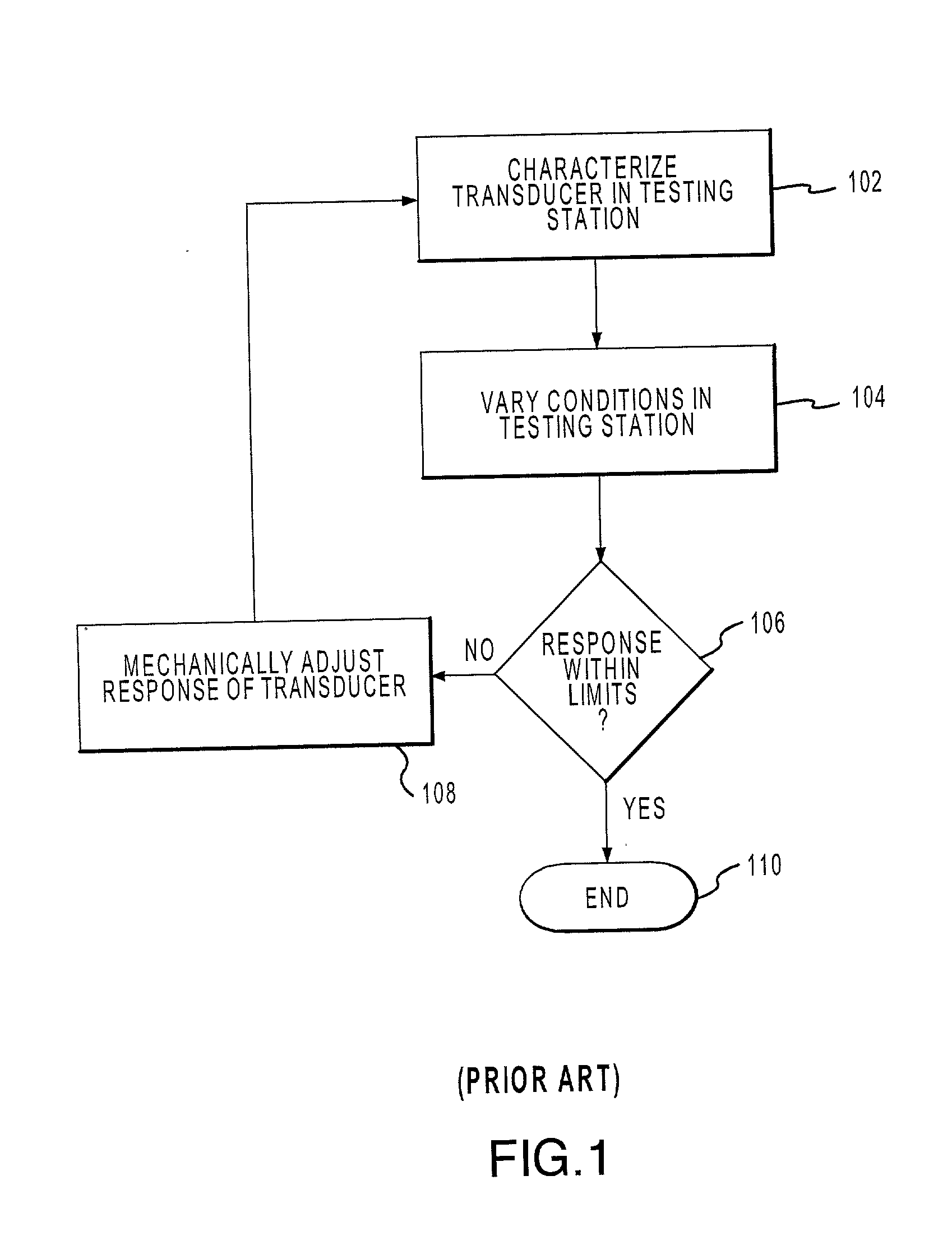

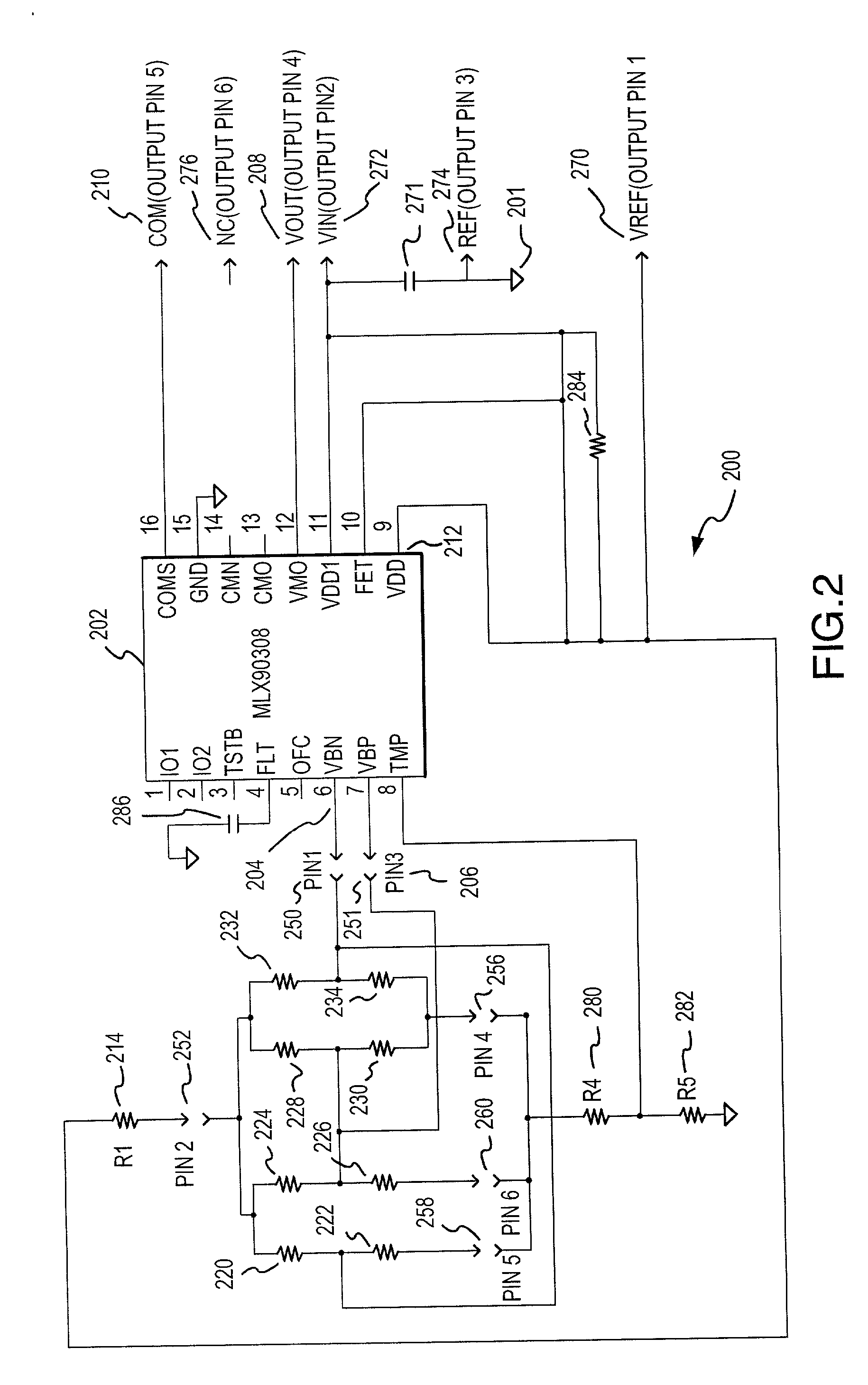

Method and apparatus for the calibration and compensation of sensors

InactiveUS20020078732A1Fluid pressure measurementApparatus with stored calibration coefficientsTransducerEngineering

The present invention discloses a method of using of a programmable circuit to calibrate a transducer. The programmable circuit is coupled to or communicates with a computer and to a testing station. The computer automatically varies the conditions of the testing station and programs the programmable circuit to produce a desired response. In another embodiment, a system is presented that can be used to measure various parameters that includes a programmable that may be mounted in the same package as a sensor. Such a system may include pressure sensors that are optimized to measure very low pressures.

Owner:HONEYWELL INT INC

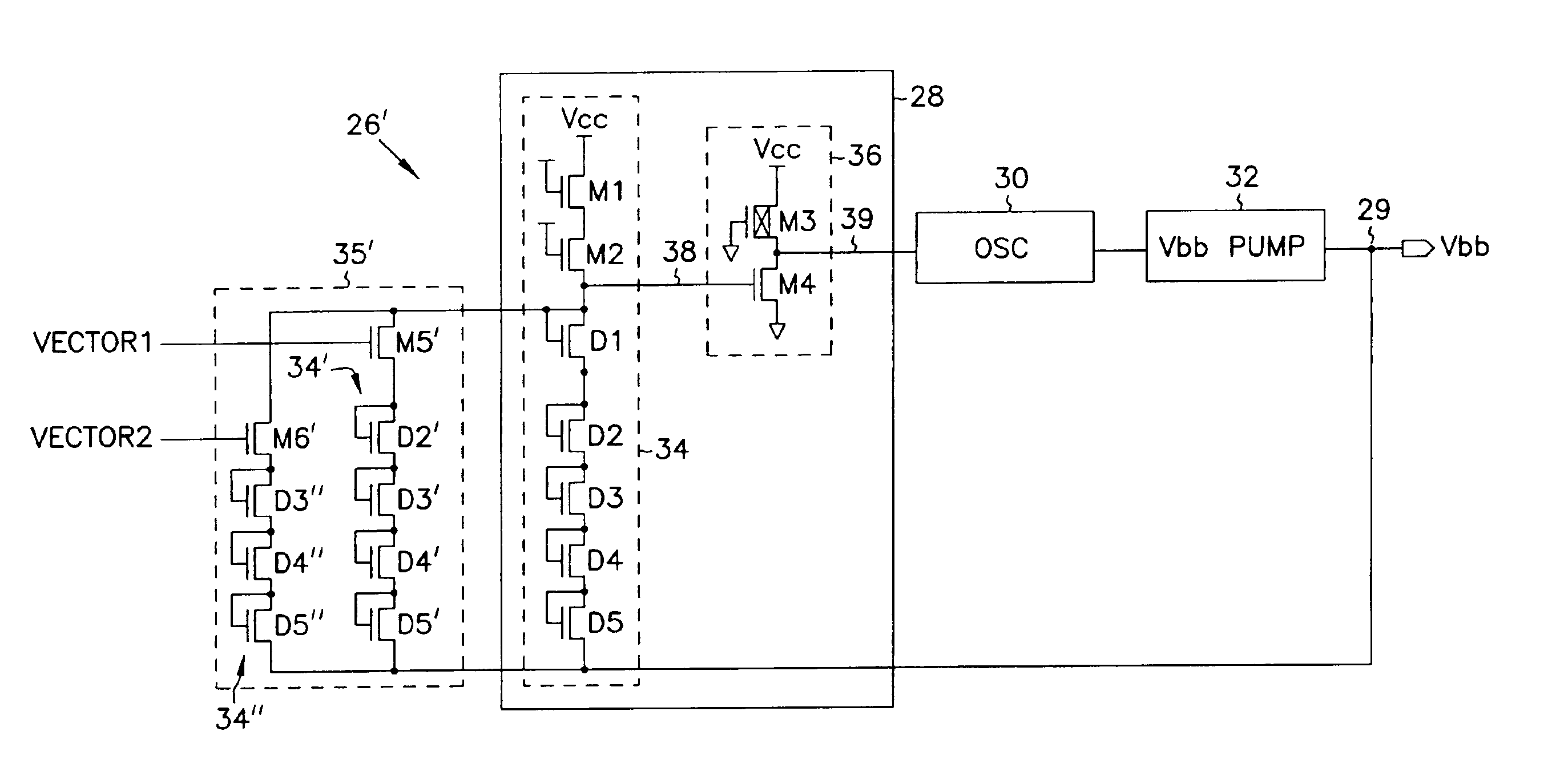

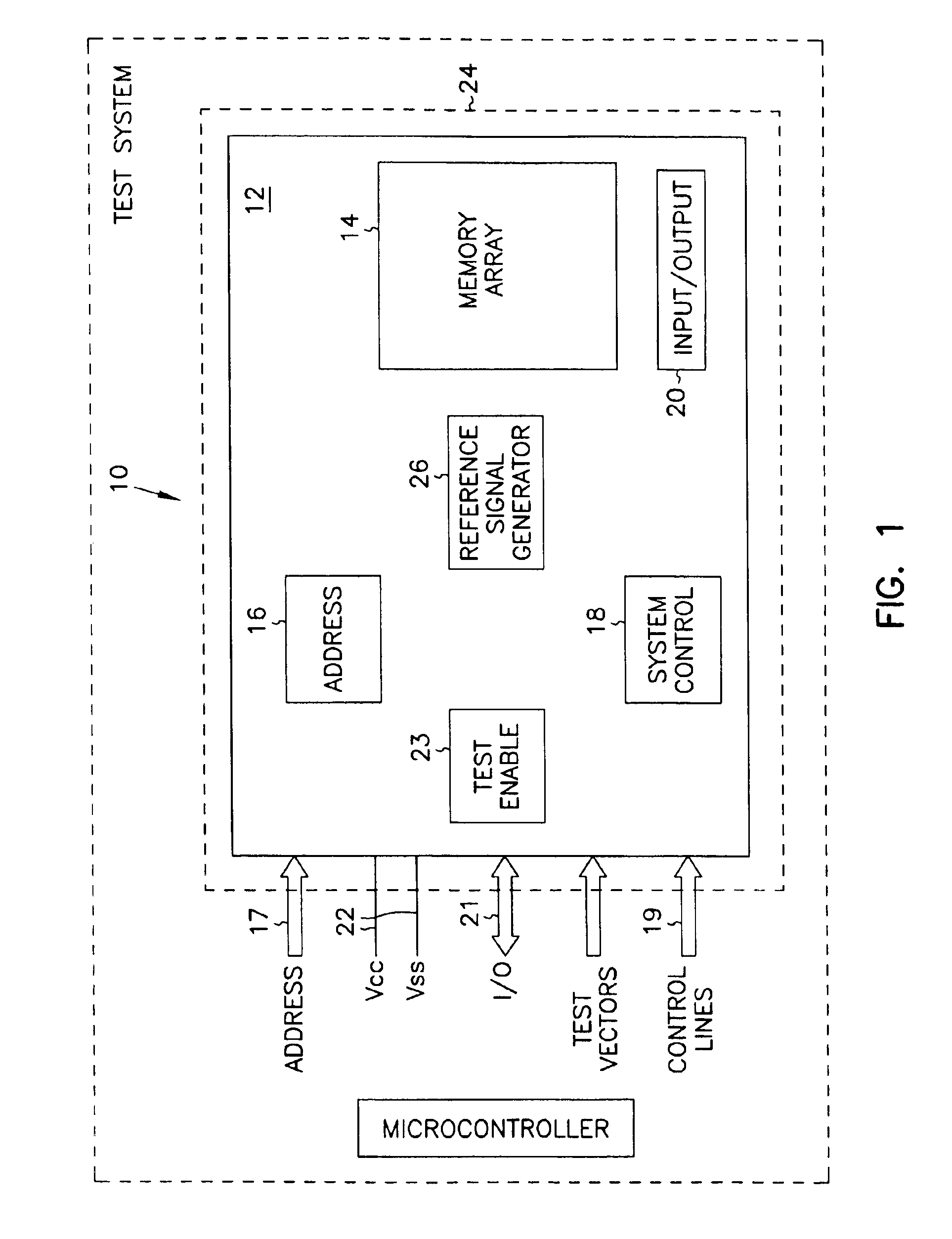

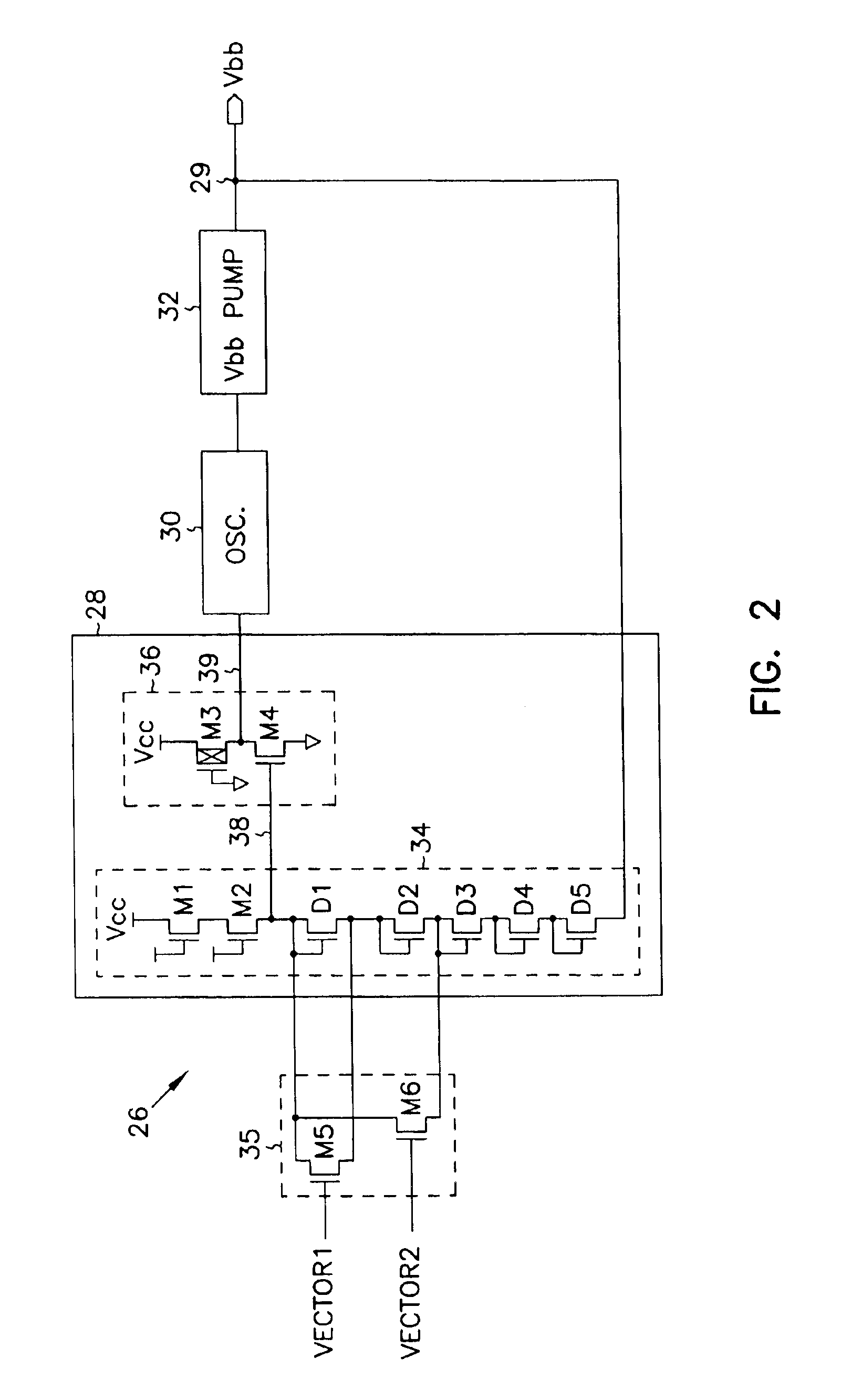

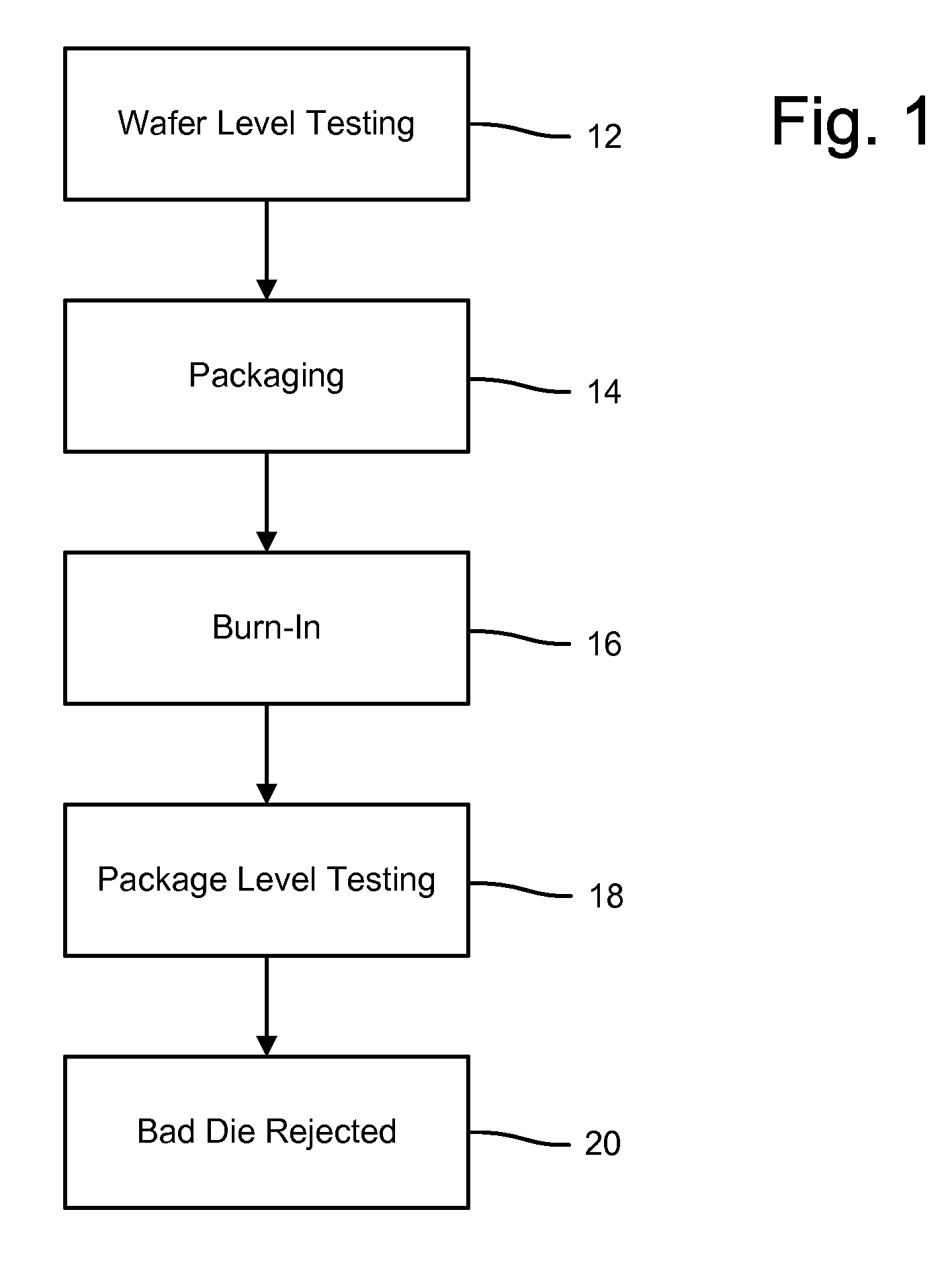

System for testing integrated circuit devices

InactiveUS6930503B2Shorten the timeShorten the time to marketDigital storageFault location by increasing destruction at faultProgrammable logic deviceProgrammable circuits

A voltage generating circuit for generating internal voltage for a packaged integrated circuit memory device, is controllable to provide incremental adjustments in the voltage for testing of the memory device. The voltage generating circuit permits internally generated voltages of the memory device, such as the substrate voltage Vbb, the DVC2 voltage, and the pumped voltage Vccp, to be controlled externally through the application of test signals via the conventional test function, in performing standard device tests such as the static refresh test, logic 1s and 0s margin testing, and the like for packaged memory devices. Also, programmable circuits including programmable logic devices, such as anti-fuses, are provided that are programmable to maintain the voltage at a magnitude to which it is adjusted.

Owner:CONVERSANT INTPROP MANAGEMENT INC

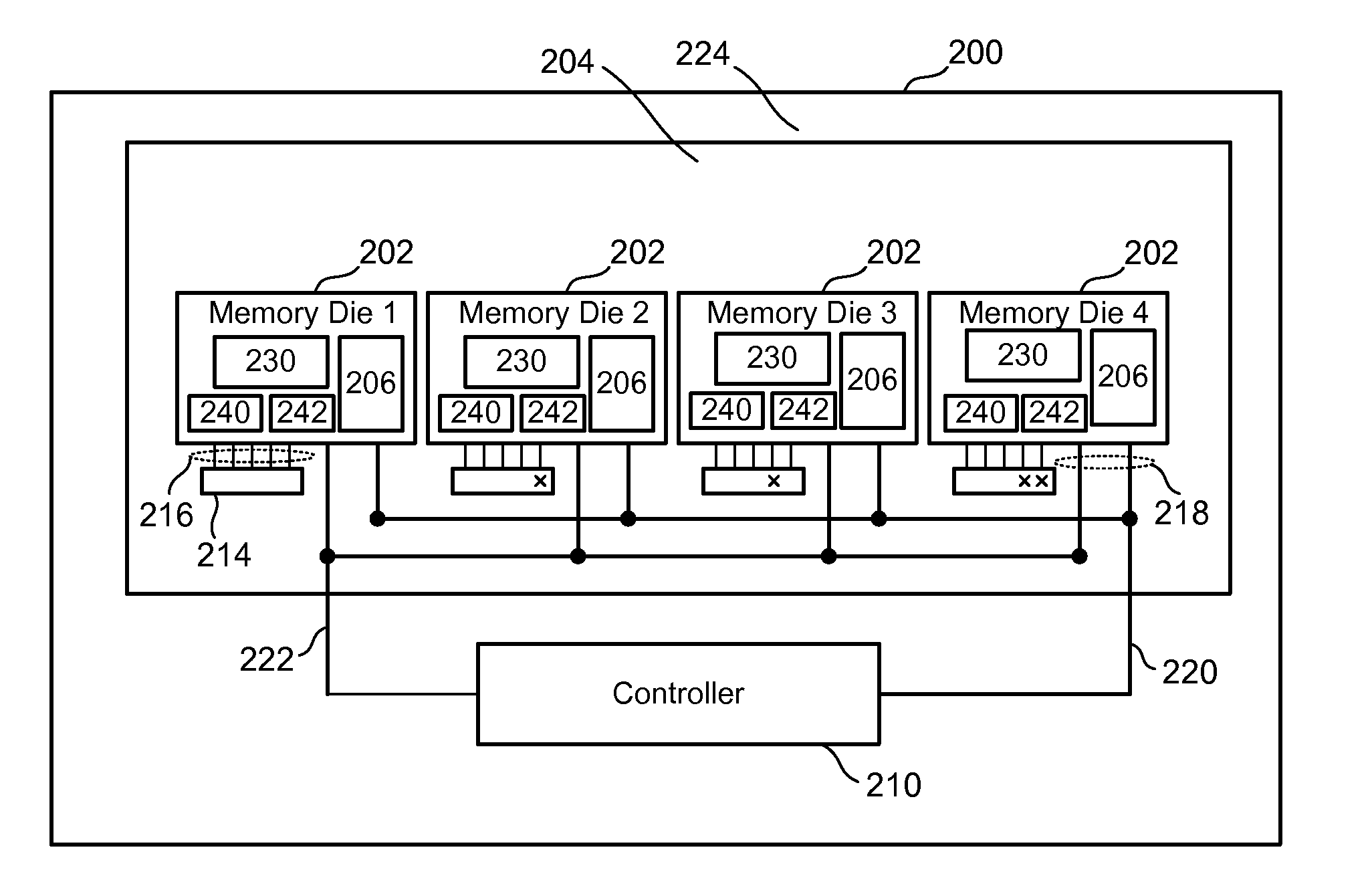

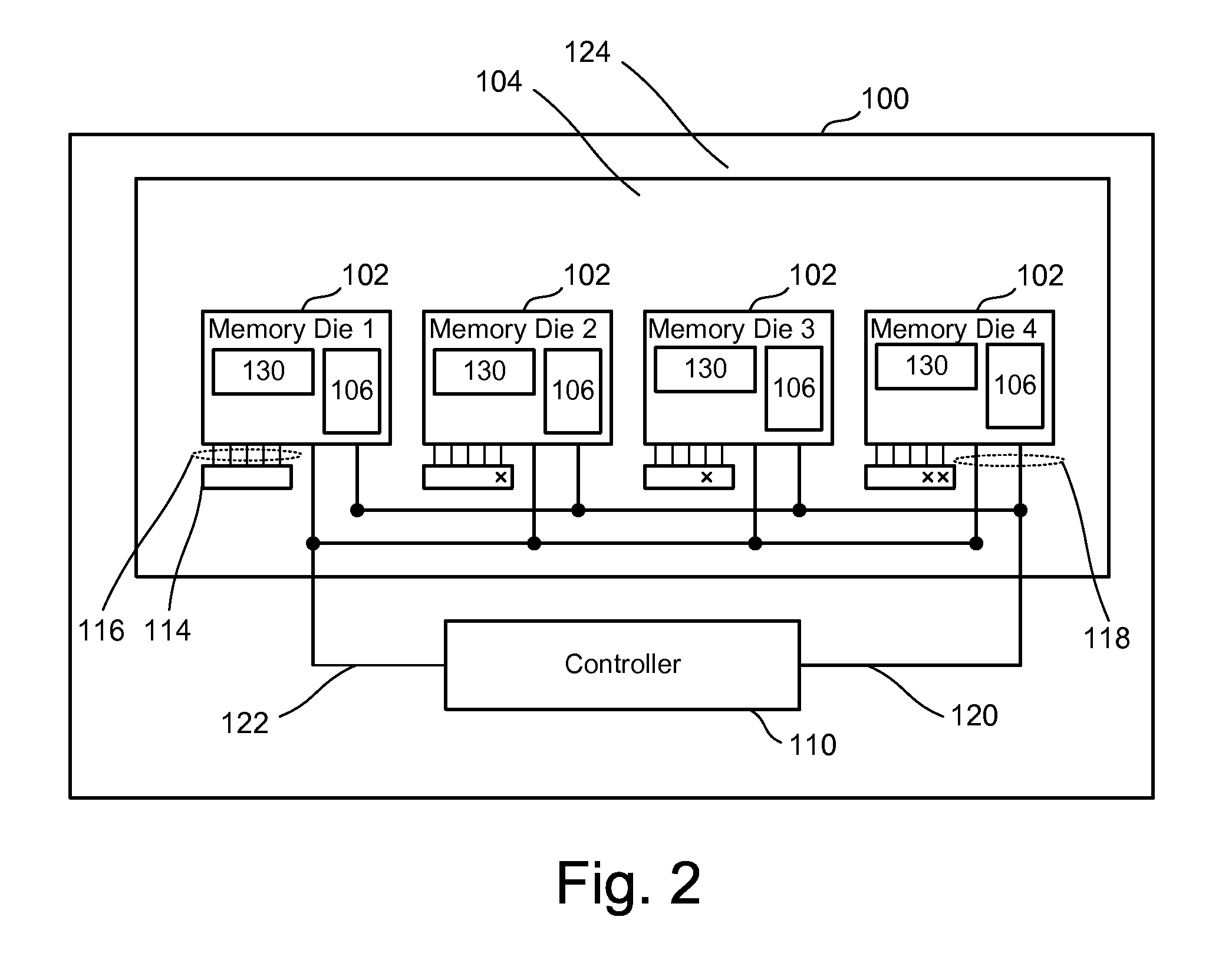

Systems for programmable chip enable and chip address in semiconductor memory

Memory die are provided with programmable chip enable circuitry to allow particular memory die to be disabled after packaging and / or programmable chip address circuitry to allow particular memory die to be readdressed after being packaged. In a multi-chip memory package, a memory die that fails package-level testing can be disabled and isolated from the memory package by a programmable circuit that overrides the master chip enable signal received from the controller or host device. To provide a continuous address range, one or more of the non-defective memory die can be re-addressed using another programmable circuit that replaces the unique chip address provided by the pad bonding. Memory chips can also be also be readdressed after packaging independently of detecting a failed memory die.

Owner:SANDISK TECH LLC

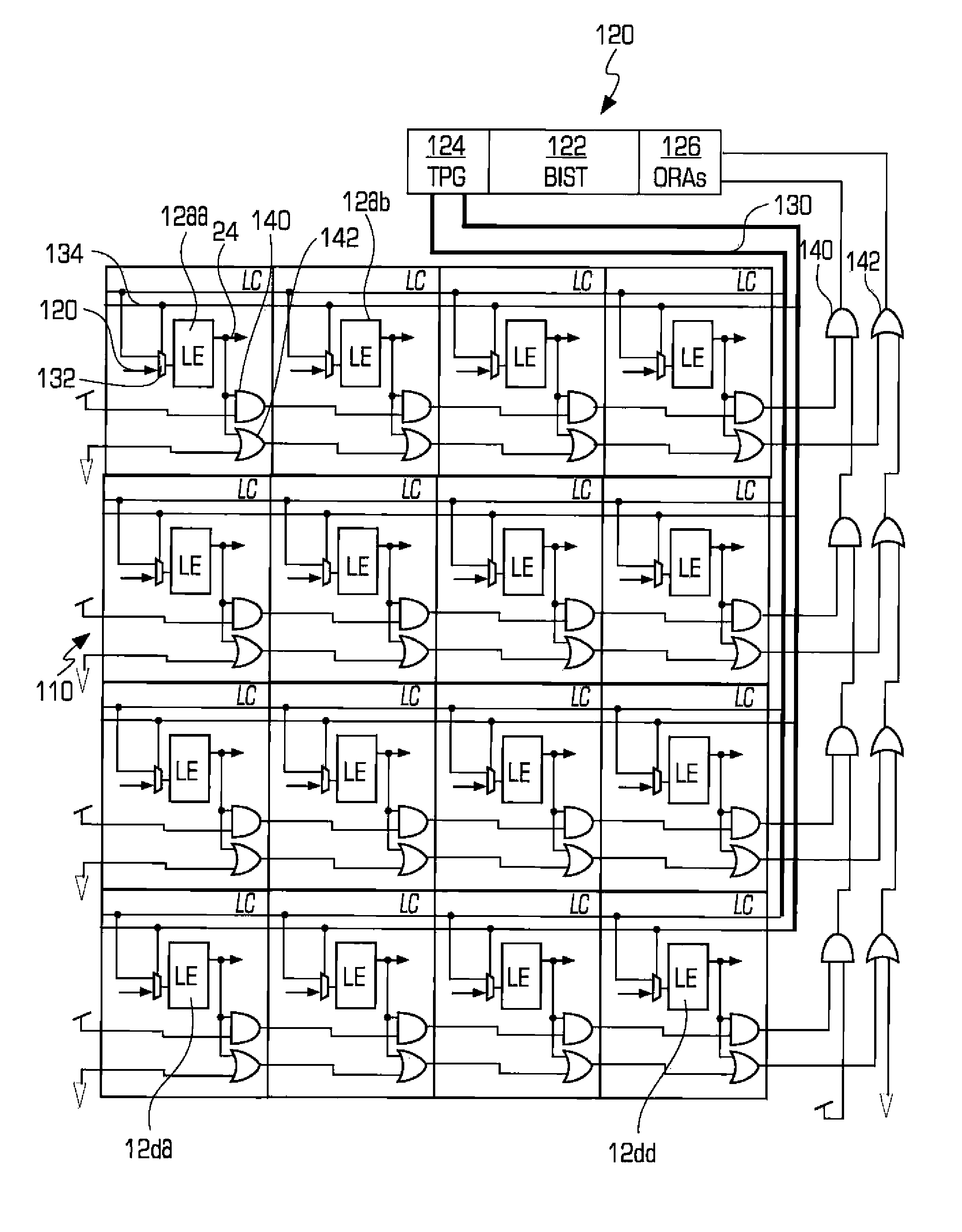

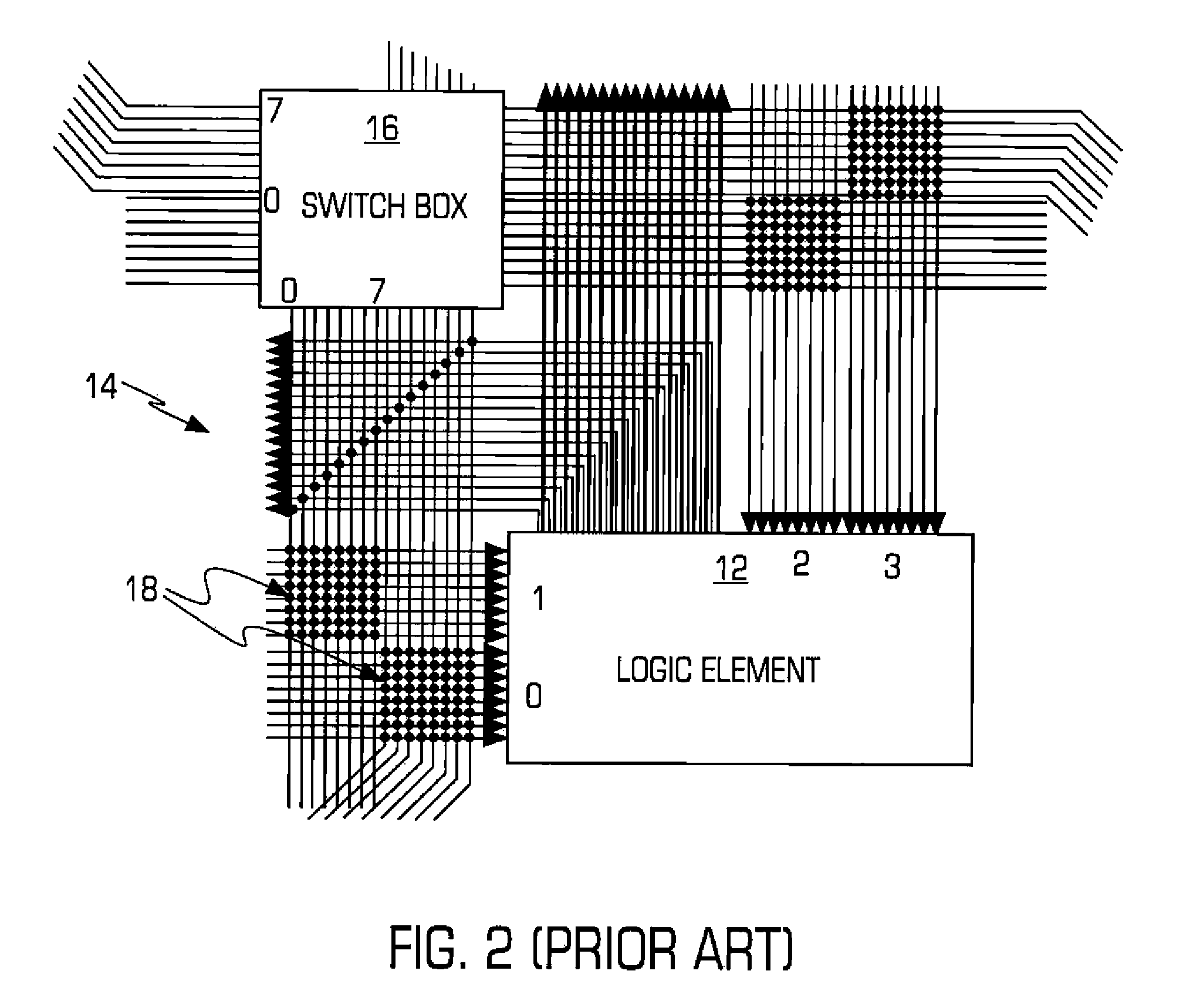

Programmable integrated circuit having built in test circuit

A programmable integrated circuit has a plurality of logic elements with each logic element having a plurality of input leads and at least one output lead. The programmable integrated circuit further comprises a group of interconnect lines, and a first set of programmable circuits for electrically connecting the input and output leads of the plurality of logic elements to each other through the group of interconnect lines. The programmable integrated circuit further comprises a test circuit having at least one input and one output. Further the programmable integrated circuit comprises a second set of programmable circuits for electrically connecting the one output of the test circuit to the plurality of input leads of each of the plurality of logic elements and for electrically connecting the at least one output lead of each of the plurality of logic elements to the one input of the test circuit, through the group of interconnect lines.

Owner:SILICON STORAGE TECHNOLOGY

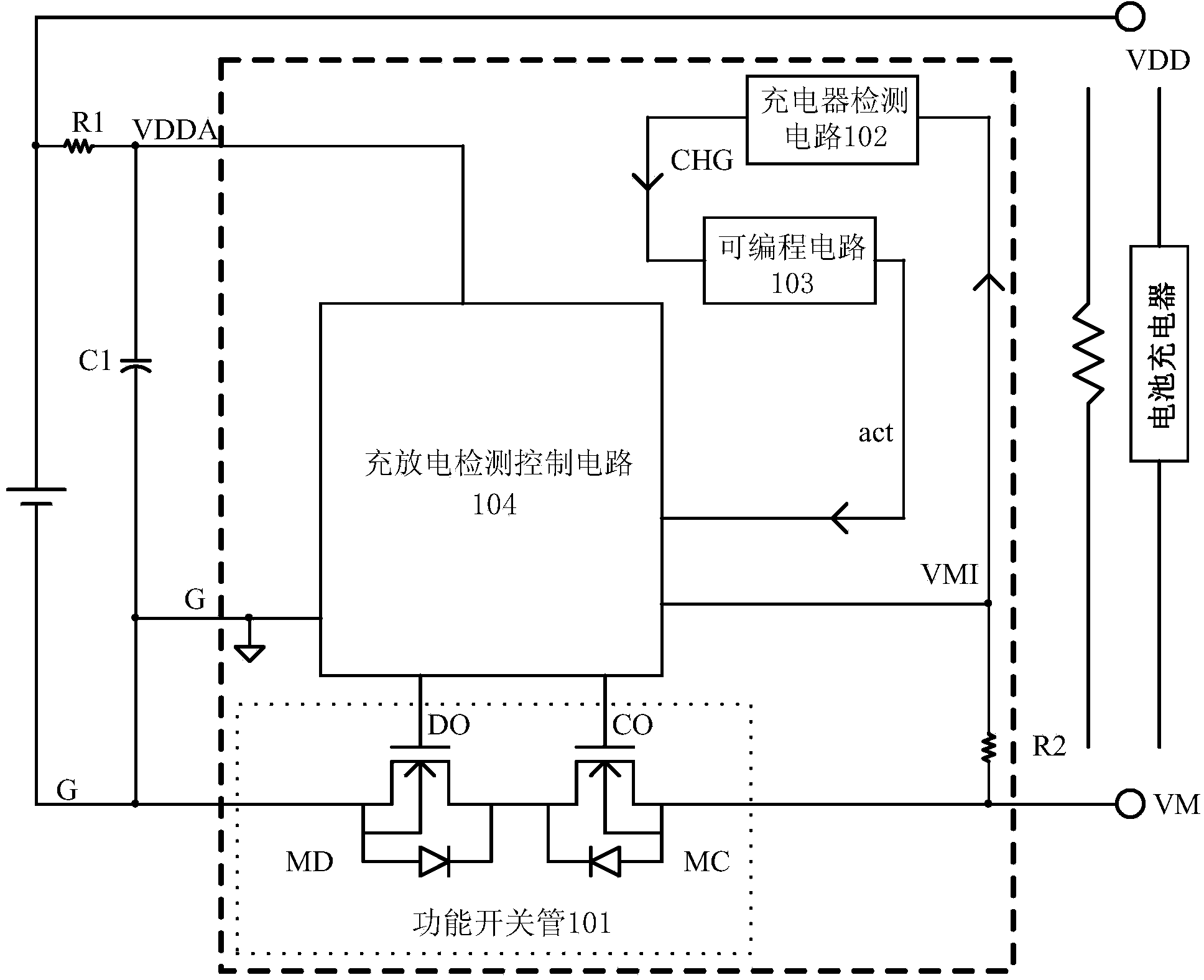

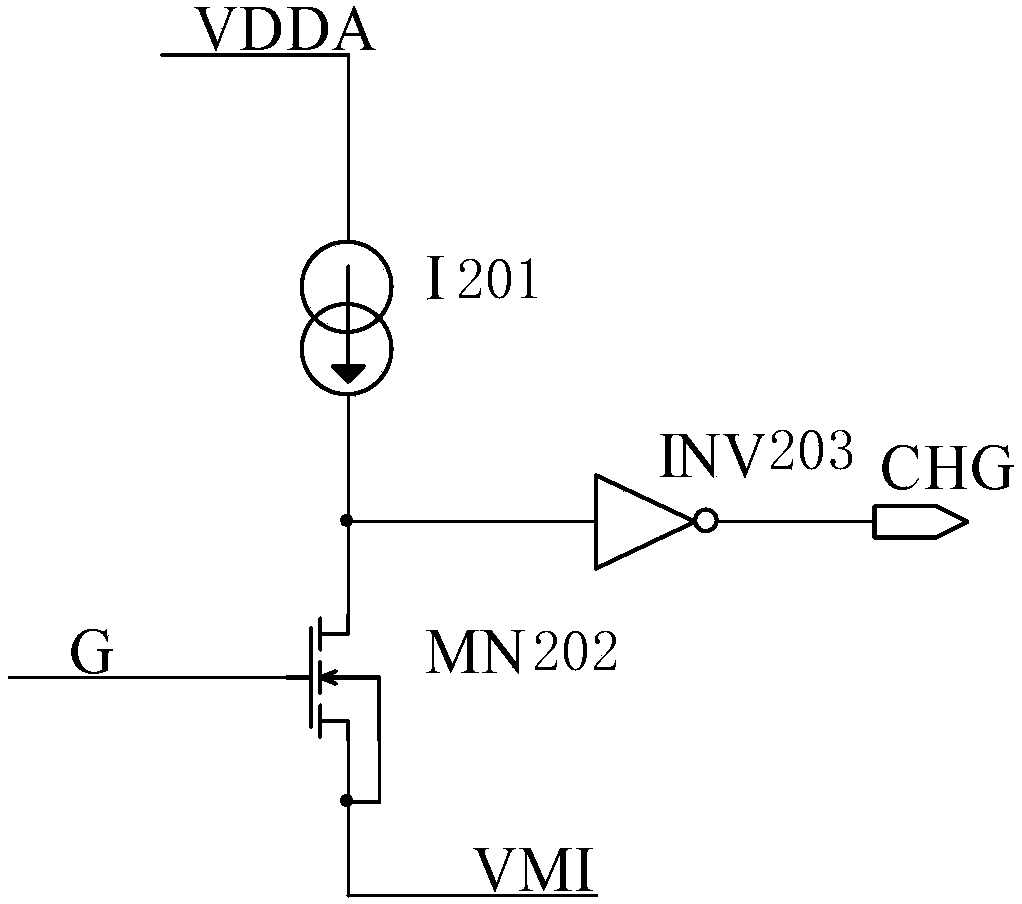

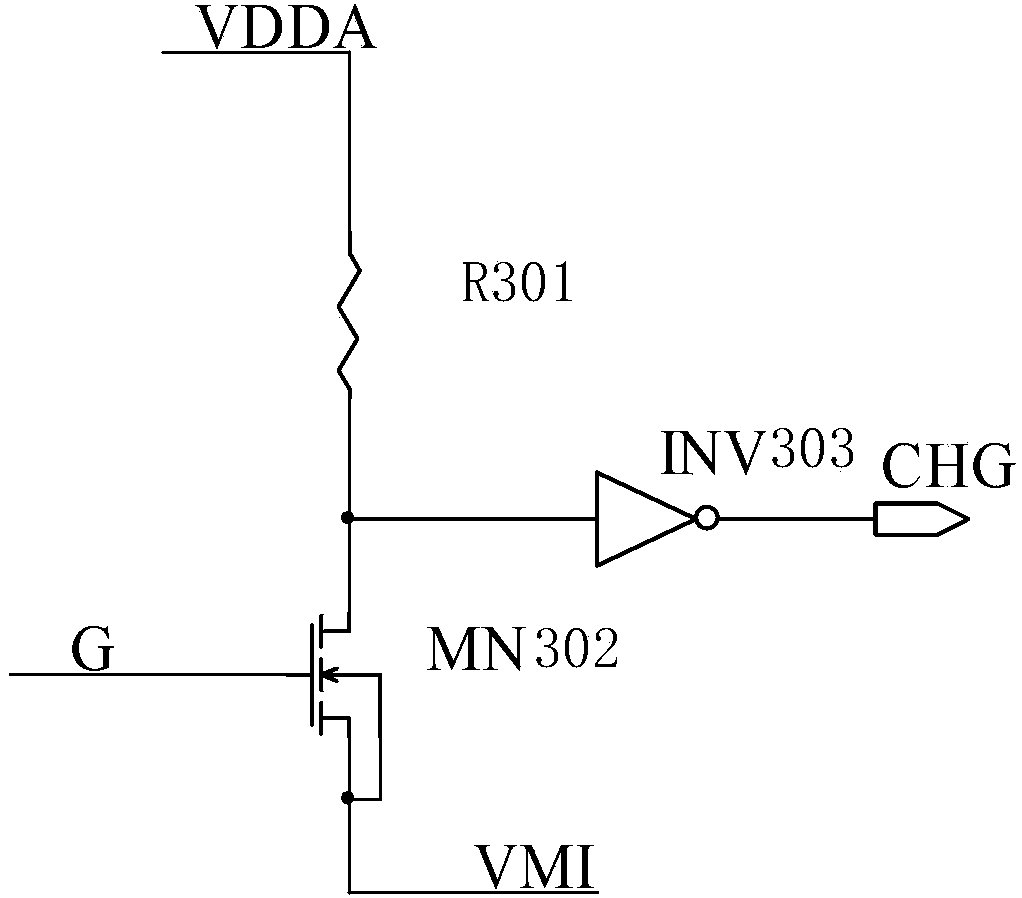

Battery protection circuit and system

ActiveCN104348233AImprove experienceElectric powerBattery overcurrent protectionElectricityElectrical battery

The embodiment of the invention relates to a battery protection circuit and a battery protection system. The battery protection circuit comprises a functional switch tube, a charger detection circuit, a programmable circuit and a charge-discharge detection control circuit, wherein the functional switch tube is connected between a negative electrode of a battery and the charge-discharge detection control circuit; the charger detection circuit is used for detecting whether the battery is connected to a charger, outputting a charge-discharge turn-off signal when the connection of the battery to the charger is not detected, and outputting a first charge-discharge activation signal when the connection of the battery to the charger is detected; the programmable circuit is used for outputting an initial state signal when receiving the charge-discharge turn-off signal and rewriting the initial state signal into a second charge-discharge activation signal when receiving the first charge-discharge activation signal; the charge-discharge detection control circuit is used for closing the functional switch tube and forbidding the battery to be charged and discharged when receiving the initial state signal, and opening the functional switch tube, controlling the battery to be charged and discharged and detecting the charge-discharge state of the battery when receiving the second charge-discharge activation signal. Thus the problem that the power of an existing battery is completely consumed after the battery stands for a period of time before being used can be solved.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

Method and apparatus providing final test and trimming for a power supply controller

InactiveUS20060053319A1Volume/mass flow measurementDc-dc conversionProgrammable circuitsThermal threshold

Owner:POWER INTEGRATIONS INC

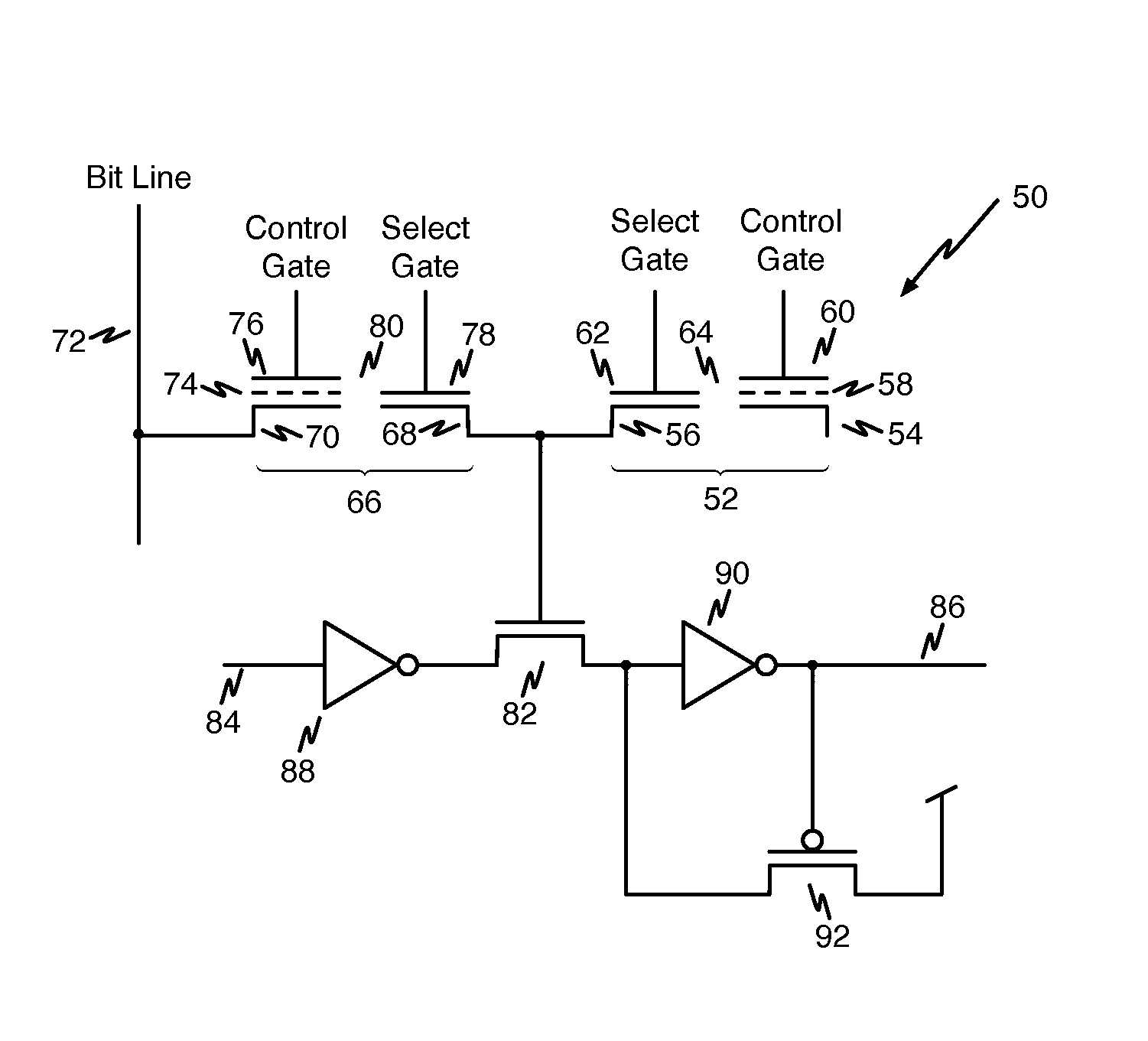

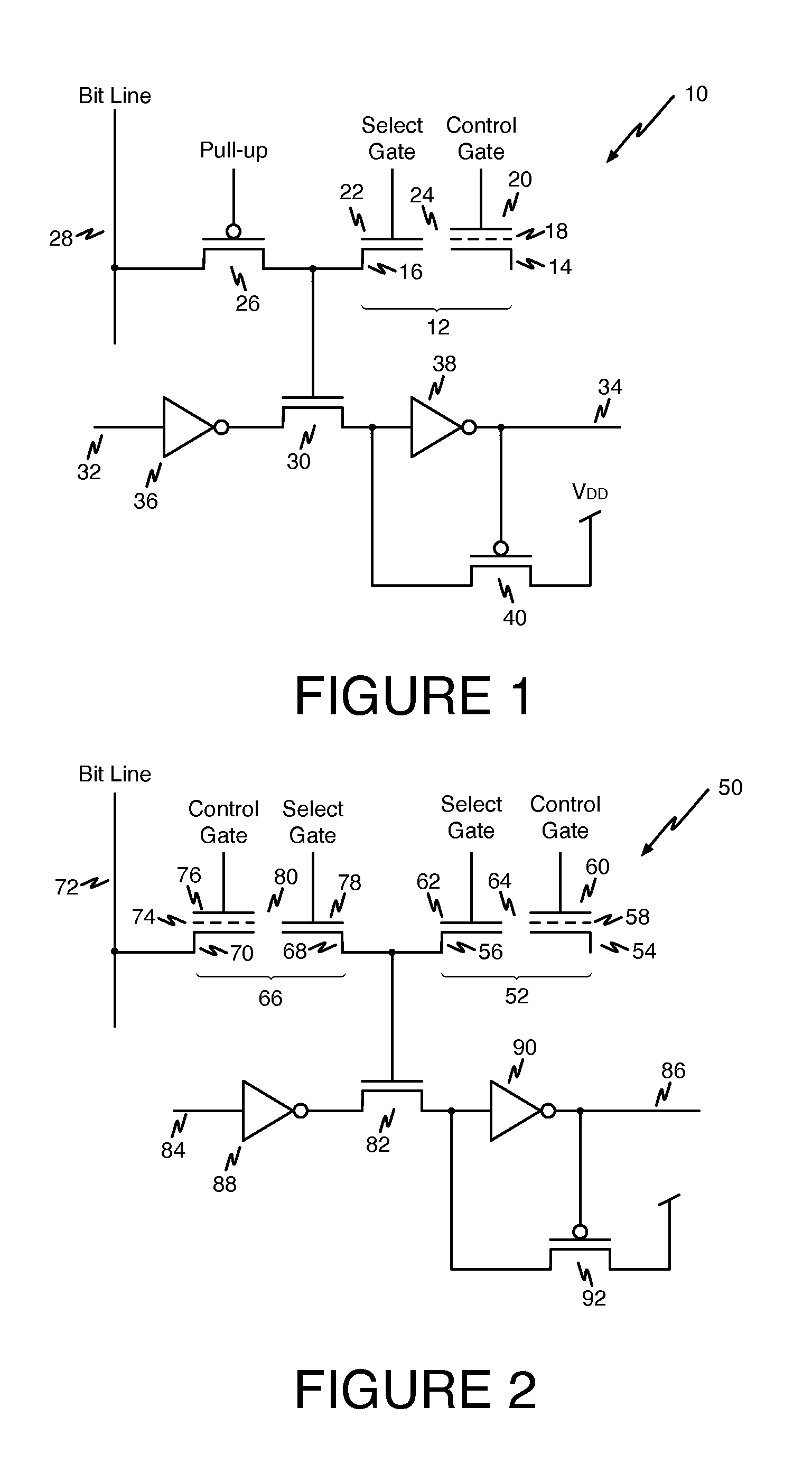

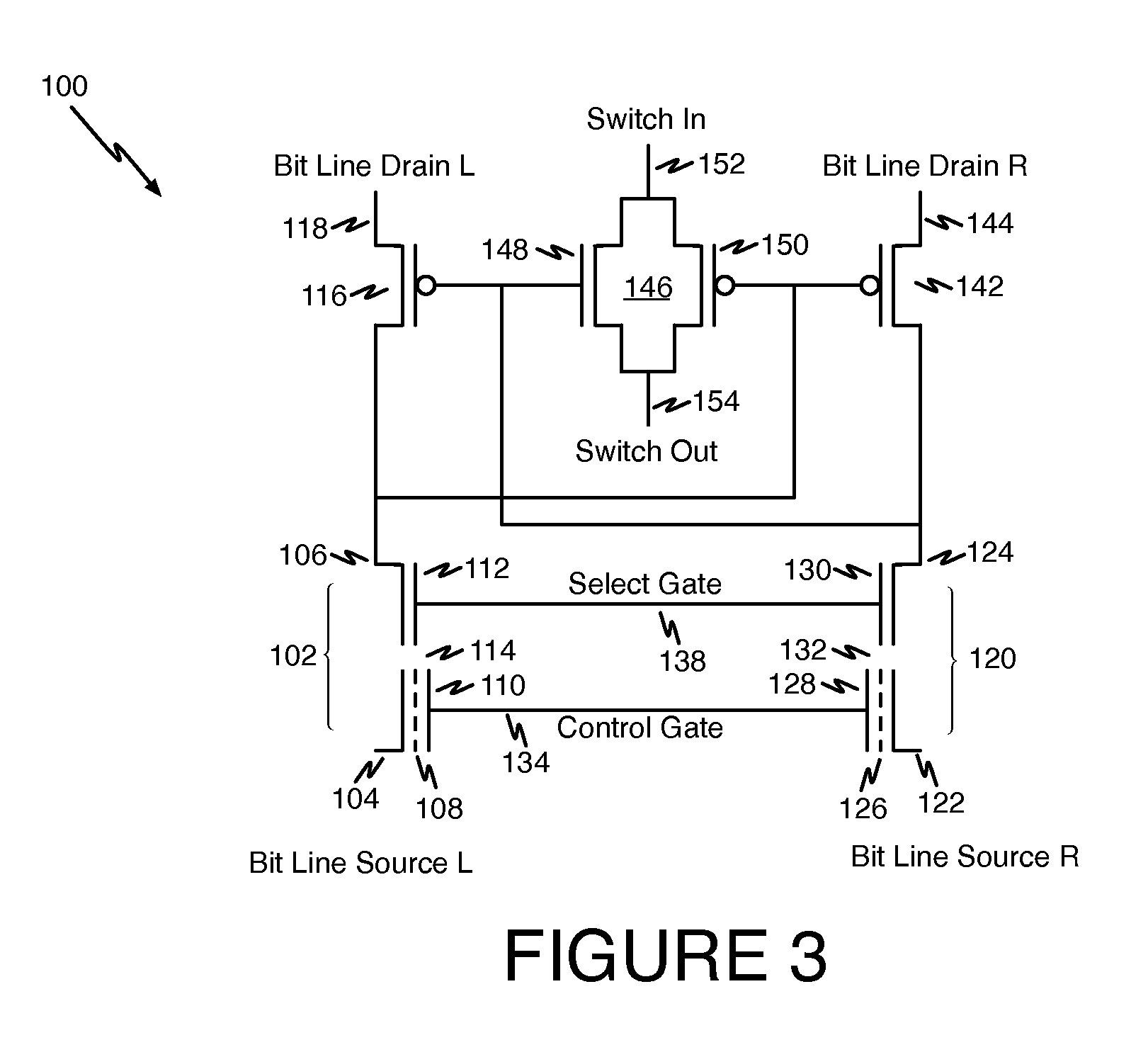

Split gate memory cell for programmable circuit device

ActiveUS7692972B1Leakage of standby current is reducedSmall cell sizeRead-only memoriesDigital storageThin oxideBit line

A split-gate memory cell, includes an n-channel split-gate non-volatile memory transistor having a source, a drain, a select gate over a thin oxide, and a control gate over a non-volatile gate material and separated from the select gate by a gap. A p-channel pull-up transistor has a drain coupled to the drain of the split-gate non-volatile memory transistor, a source coupled to a bit line, and a gate. A switch transistor has first and second source / drain diffusions, and a gate coupled to the drains of the split-gate non-volatile memory transistor and the p-channel pull-up transistor. An inverter has an input coupled to the second source / drain diffusion of the switch transistor, and an output. A p-channel level-restoring transistor has a source coupled to a supply potential, a drain coupled to the first source / drain diffusion of the switch transistor and a gate coupled to the output of the inverter.

Owner:MICROSEMI SOC

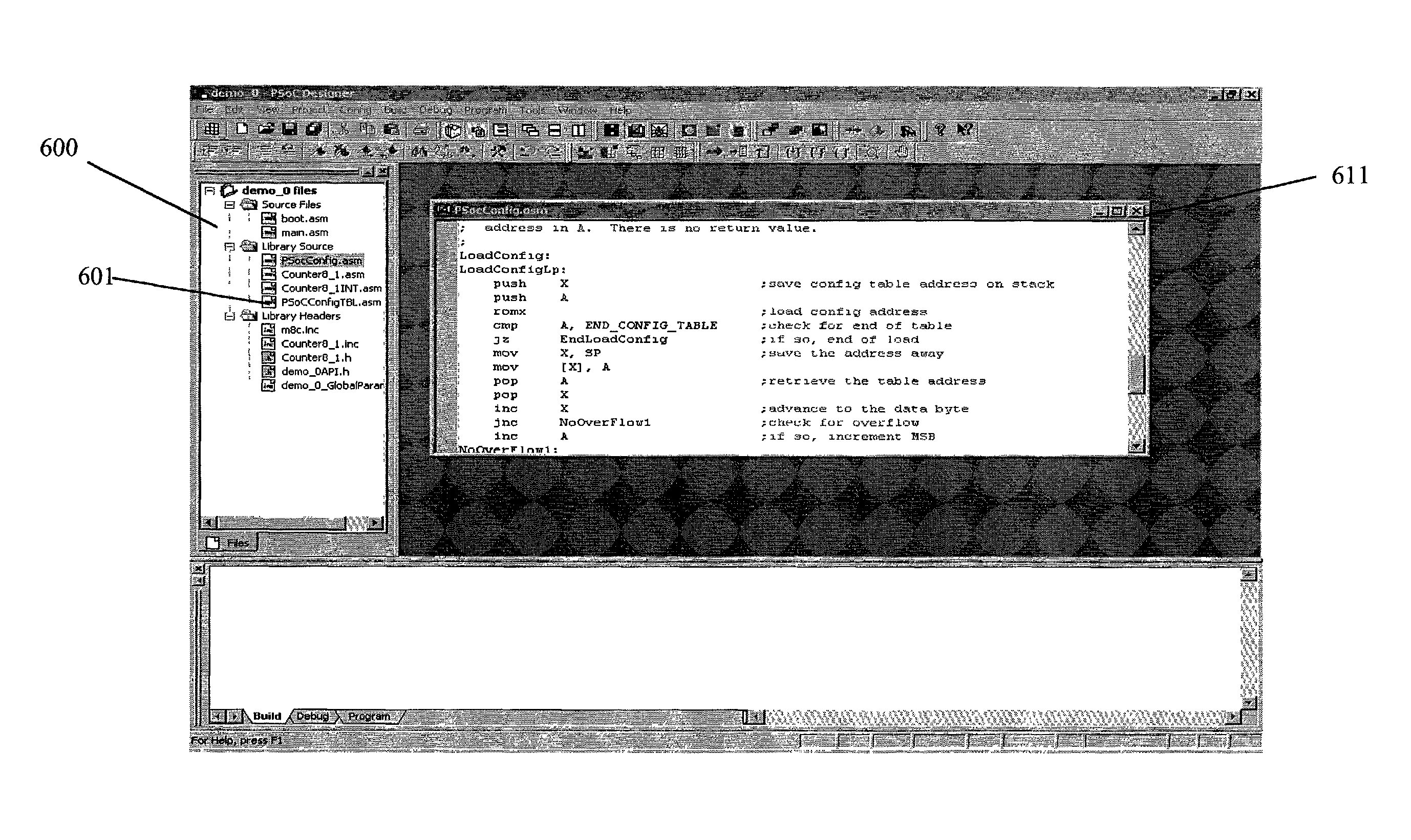

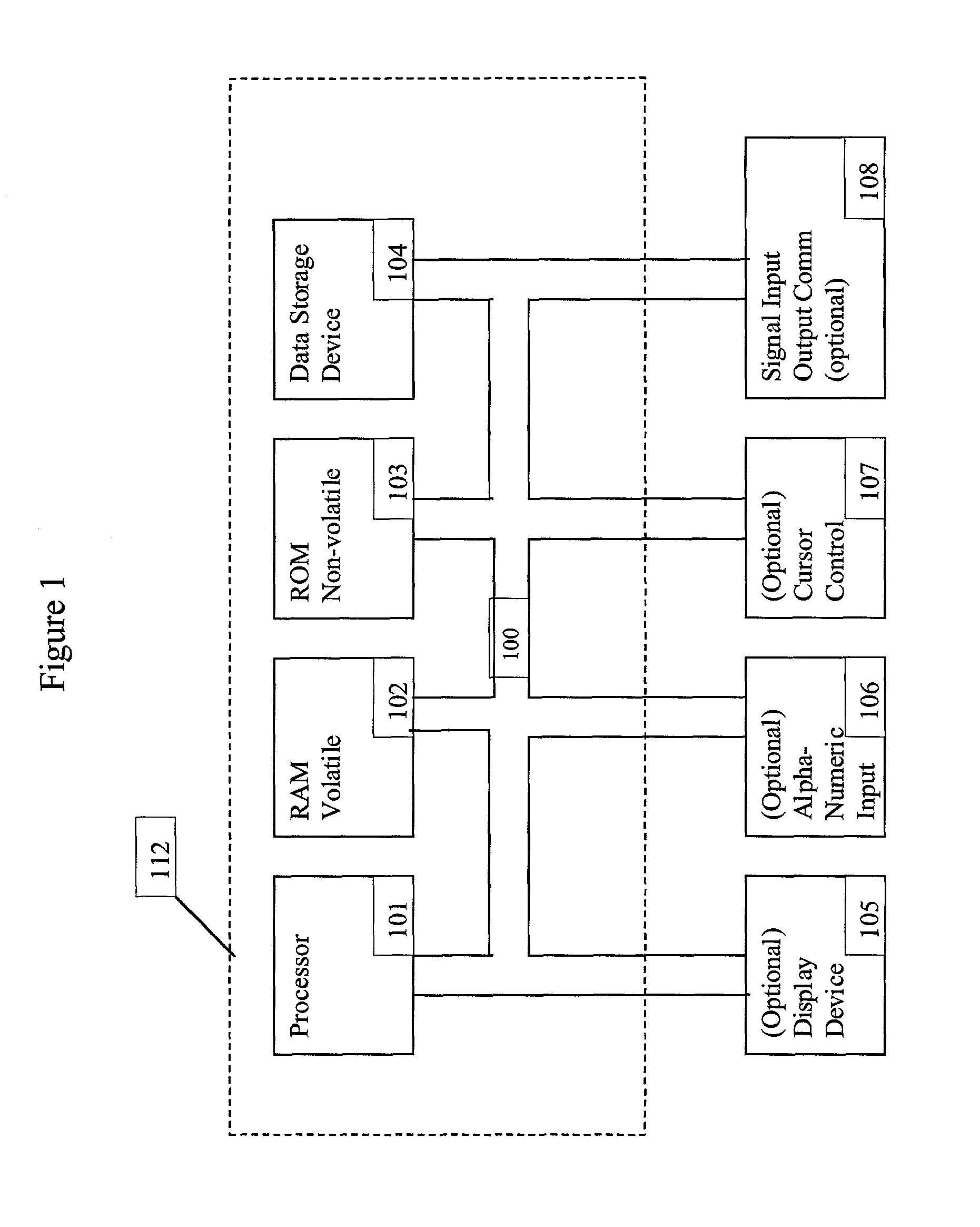

System providing automatic source code generation for personalization and parameterization of user modules

A method and system of automatically generating source code for configuring a programmable microcontroller. The method involves displaying virtual blocks in a computerized design system where the virtual blocks correspond to programmable circuit blocks in a microcontroller chip. The user selects a user module that defines a particular function to be performed on the microcontroller. The user assigns the virtual blocks to the user module. The design system then automatically generates source code for configuring the programmable blocks to perform the desired function. The source code can then be assembled, linked and loaded into the microcontroller's memory system. When executed on the microcontroller, the executable code will then set registers within the blocks to implement the function. Source code is automatically generated for: (1) realizing the user module in a hardware resource; and also (2) to configure the user module to behave in a prescribed manner.

Owner:CYPRESS SEMICON CORP