Polish stop and sealing layer for manufacture of semiconductor devices with deep trench isolation

a technology of trench isolation and sealing layer, which is applied in the direction of semiconductor/solid-state device manufacturing, basic electric elements, electric apparatus, etc., can solve the problems of increasing the difficulty of excluding inter-element interference, low-cost dielectric films typically have less desirable electrical characteristics, and achieve the effect of eliminating or drastically reducing the possibility of polysilicon stringers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

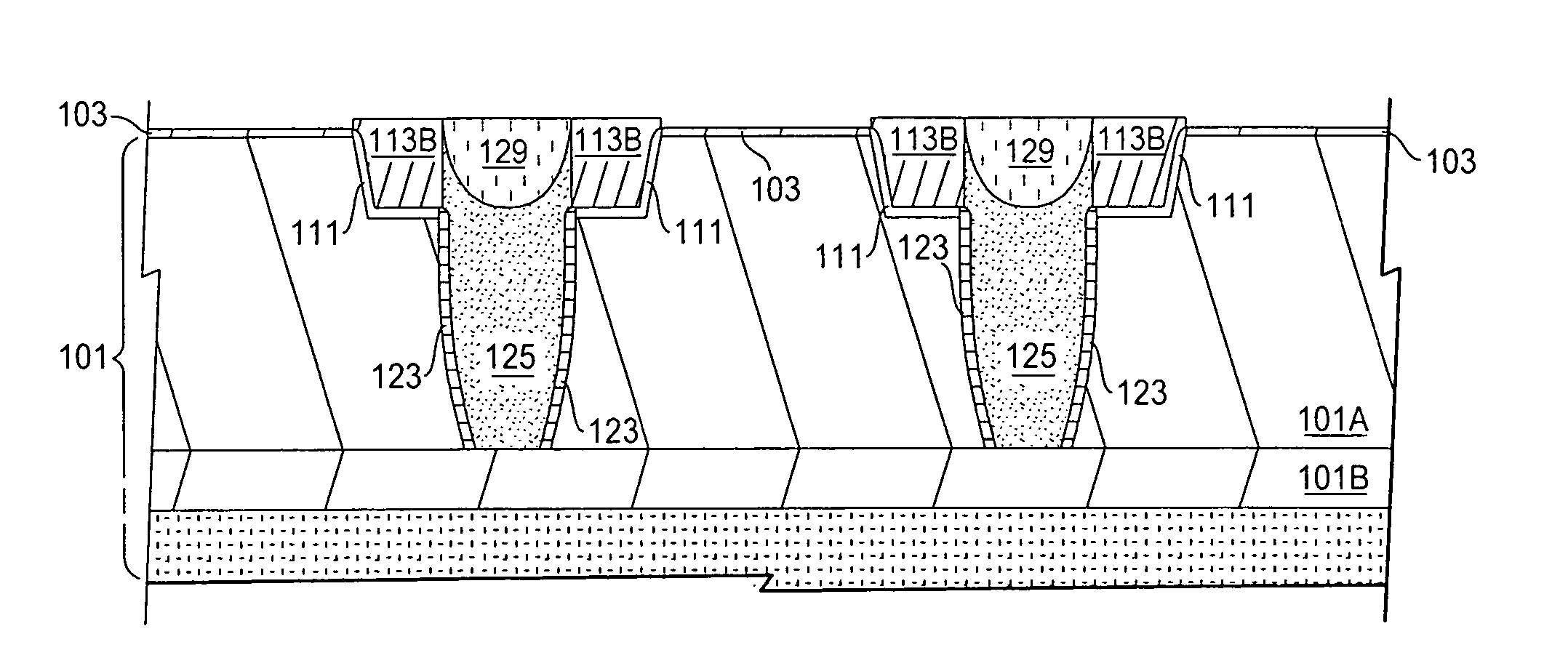

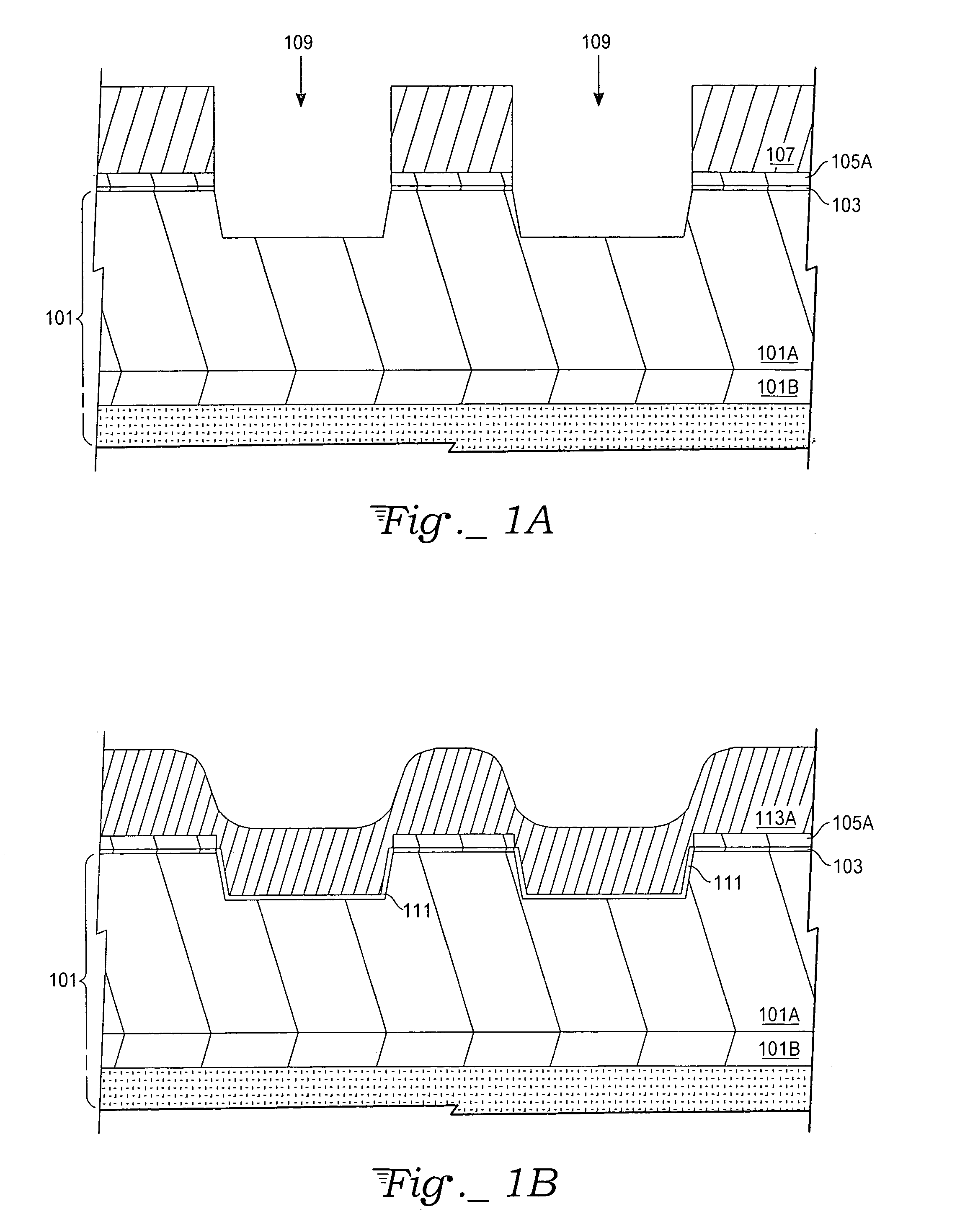

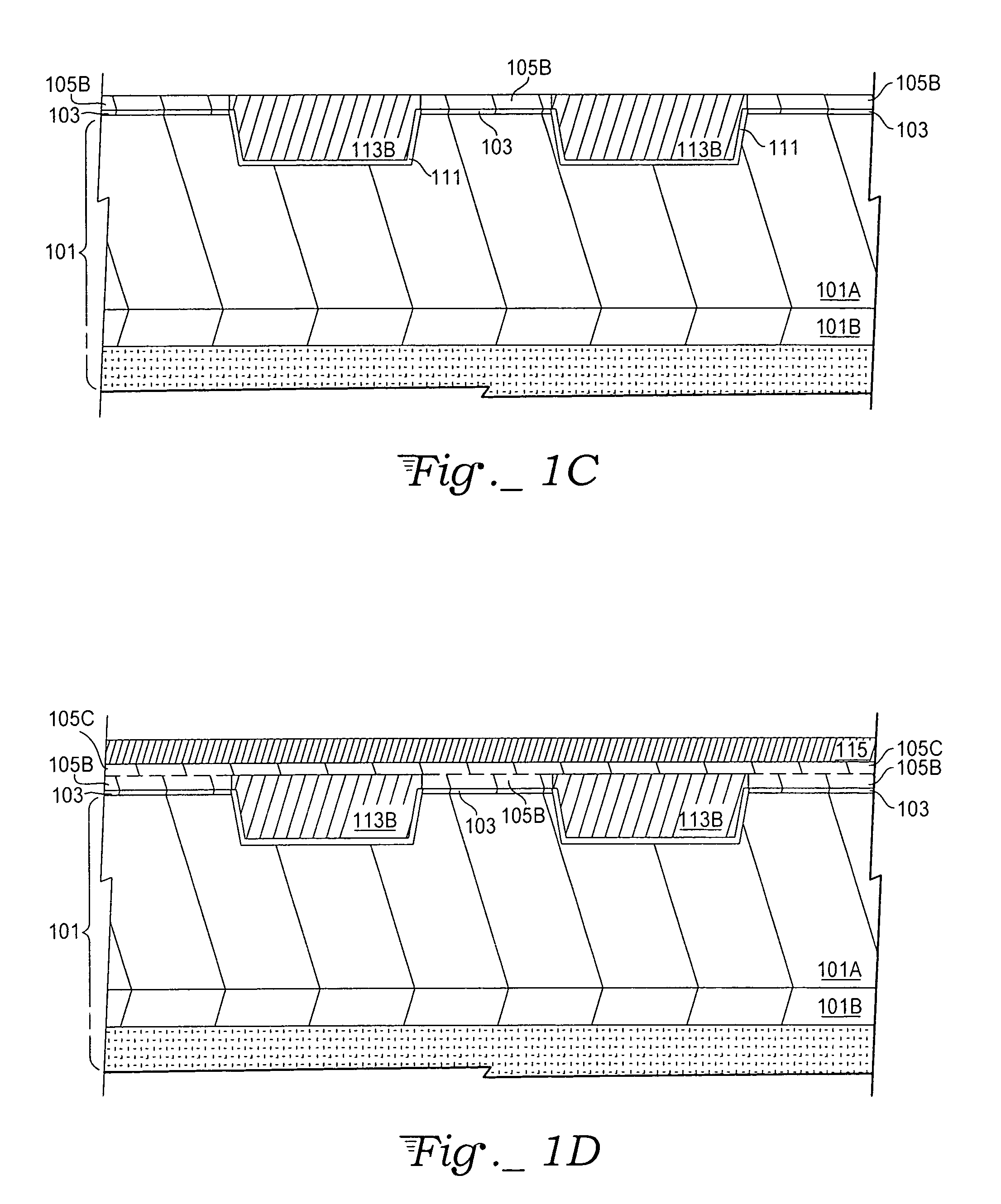

[0014]With reference to FIG. 1A, early exemplary fabrication steps of a deep trench isolation structure begin with a base substrate 101. In a specific exemplary embodiment, the base substrate 101 is a C-flat, silicon on insulator (SOI) over silicon substrate. In the specific exemplary embodiment, the silicon cap layer 101A is approximately 2 μm (2000 nm) in thickness and is bonded to an SOI insulator layer 101B. In other embodiments, the base substrate 101 may be a silicon wafer. Alternatively, another elemental group IV semiconductor or compound semiconductor (e.g., group III-V) may be selected for the base substrate 101. In a case where the base substrate 101 is a semiconductor wafer, the wafer may contain a buried oxide layer (not shown) placed below a polysilicon layer (not shown) to prevent transport of carriers through the underlying bulk semiconducting material. The polysilicon is then treated at an elevated temperature to reform crystalline (i.e., non-amorphous) silicon. In ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More