High speed analog envelope detector

an envelope detector, high-speed technology, applied in the direction of pulse manipulation, pulse technique, instruments, etc., can solve the problems of increasing the number of wires required and the weight and size of cables, affecting the power efficiency of the system, and increasing the amount of wires required

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

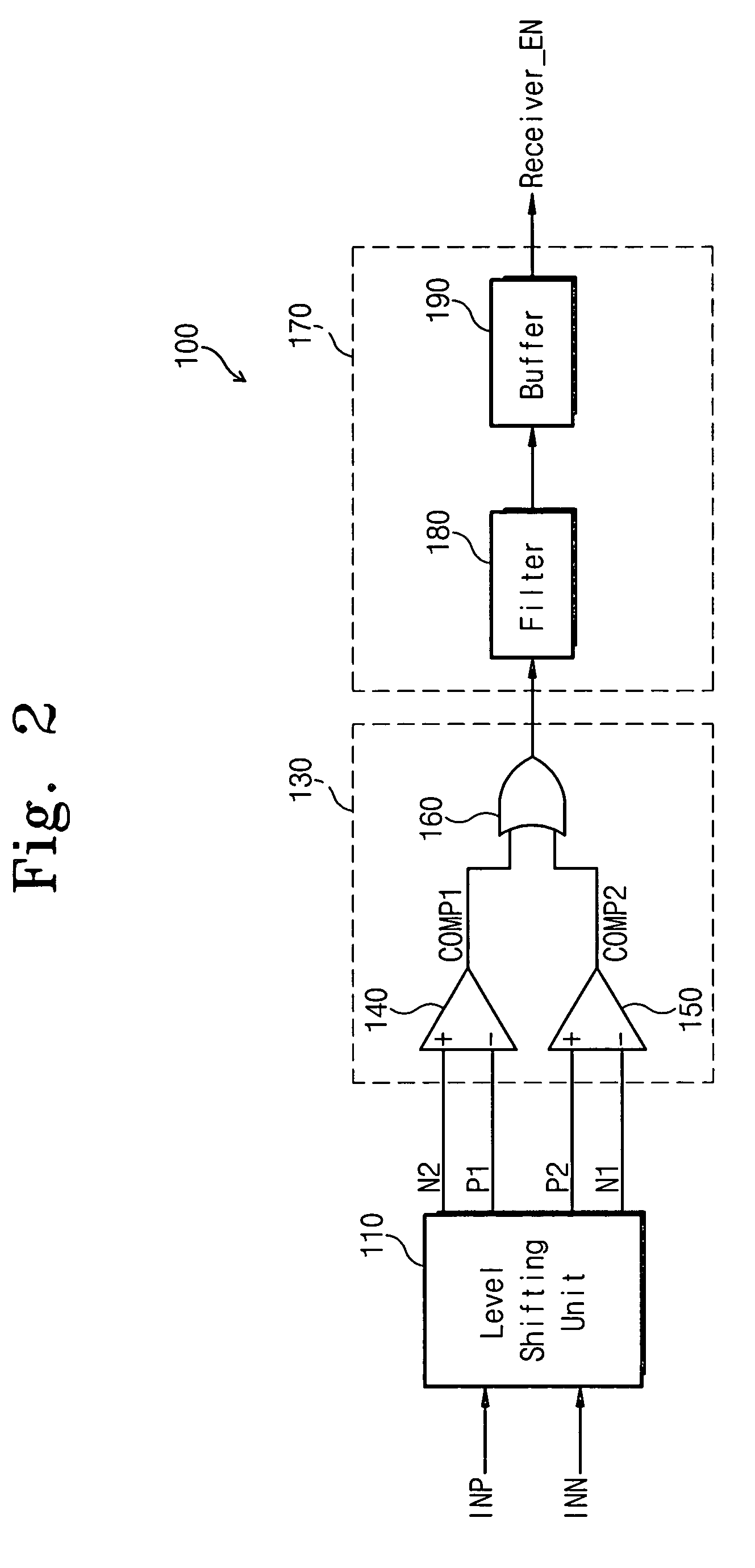

[0036]FIG. 2 is a block diagram of a transmission envelope detector 100 in accordance with a preferred embodiment of the invention.

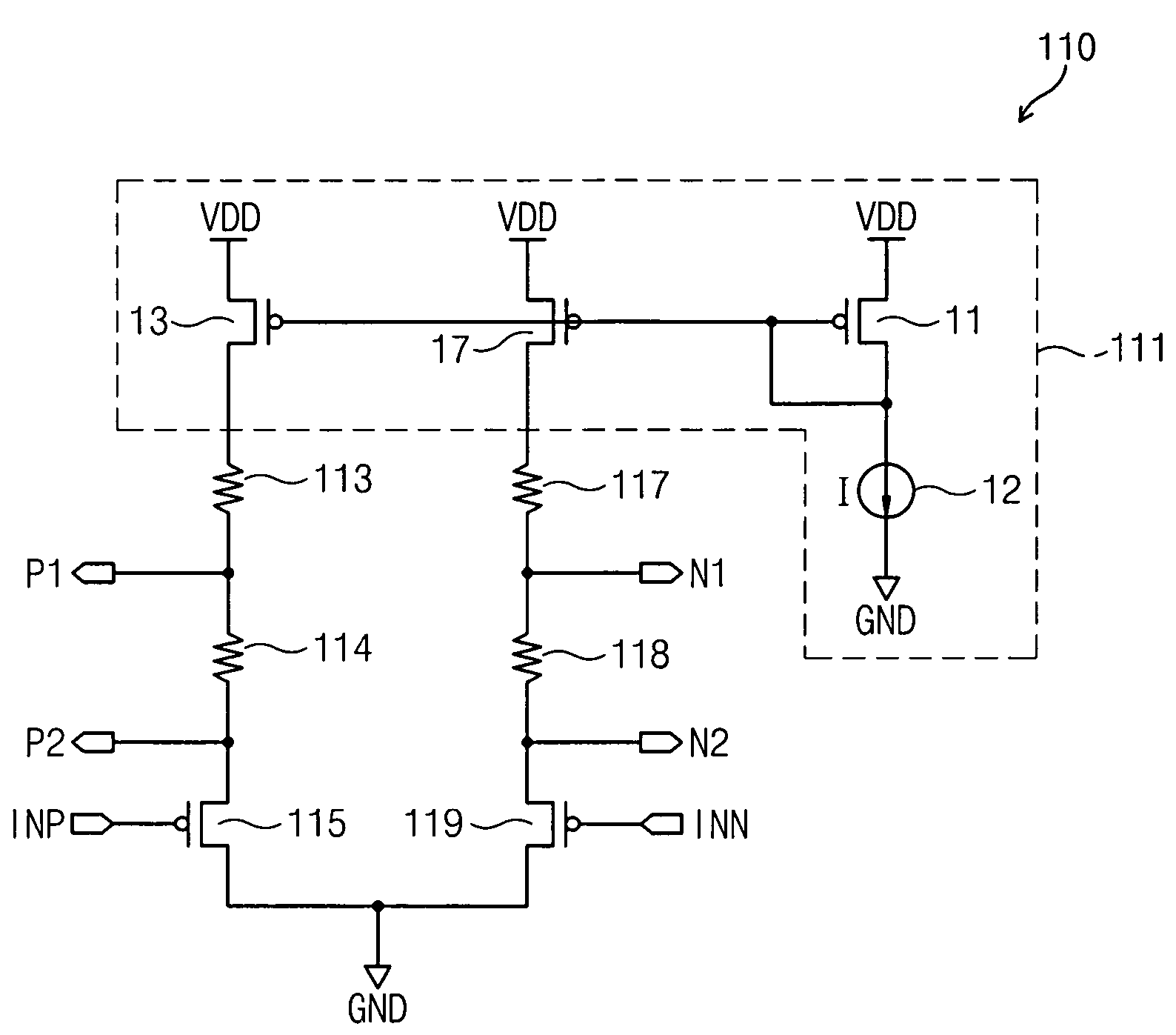

[0037]Referring to FIG. 2, the envelope detector 100 is comprised of a level shifting unit 110, a comparing circuit 130, and an output signal conditioning circuit 170. The level shifting unit 110 generates first through fourth level-shifted signals P1, P2, N1, and N2 having voltage levels higher than differential input signals INP and INN, in responds to the differential input signals INP and INN that are received (e.g., from an external device via USB cables).

[0038]The first and second level-shifted signals P1 and P2 are generated in response to the differential input signal INP having a positive value. The third and fourth level-shifted signals, N1 and N2, are generated in response to the differential input signal INN having a negative value. The first level-shifted signal P1 has a voltage level higher than that of the second level-shifted signal P2. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More