Method for realizing kernel-mode programe verification in user-mode random verification of microprocessor

A random verification, microprocessor technology, applied in the field of core state program verification, can solve the problems of complex combination of core state instructions and control register states, inability to complete the full verification of processor core state instructions, and difficulty in uniform coverage of handwritten test vectors, etc. To achieve the effect of comprehensive verification, high efficiency and high verification efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

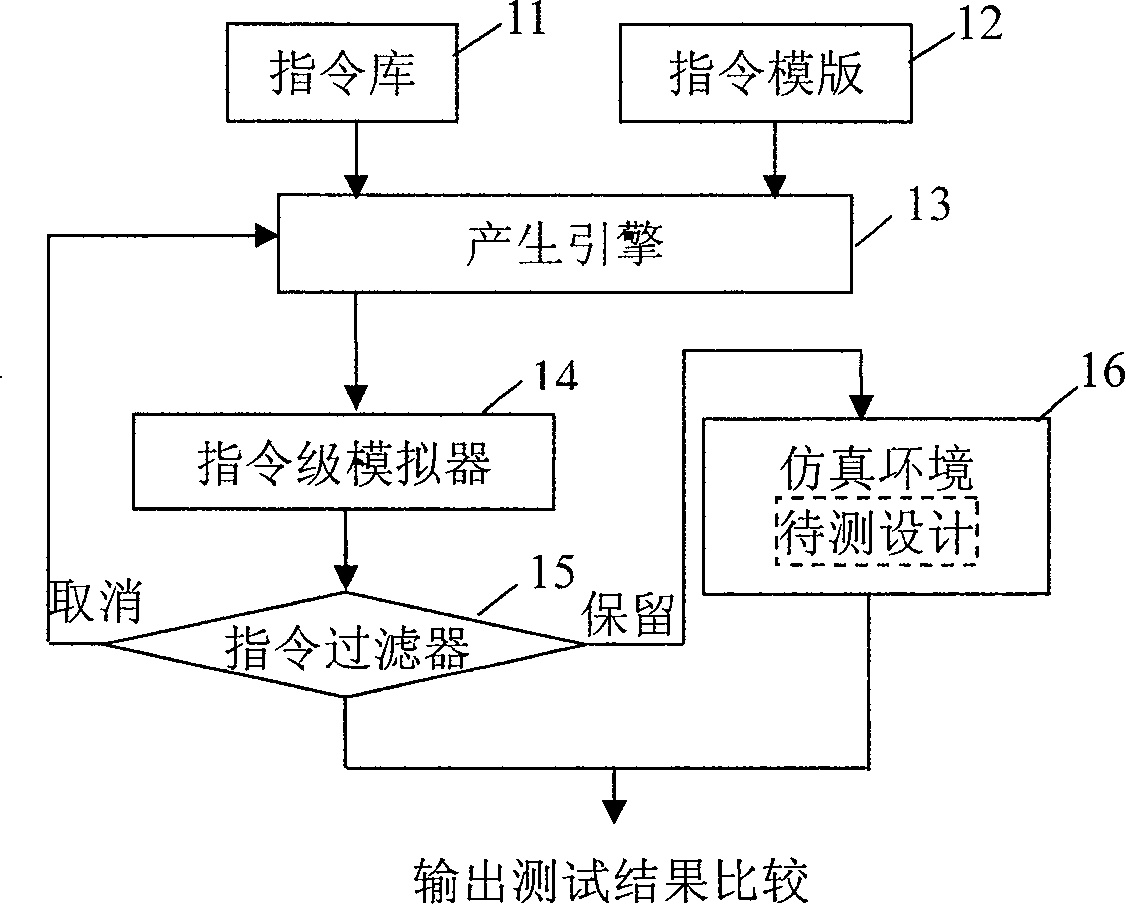

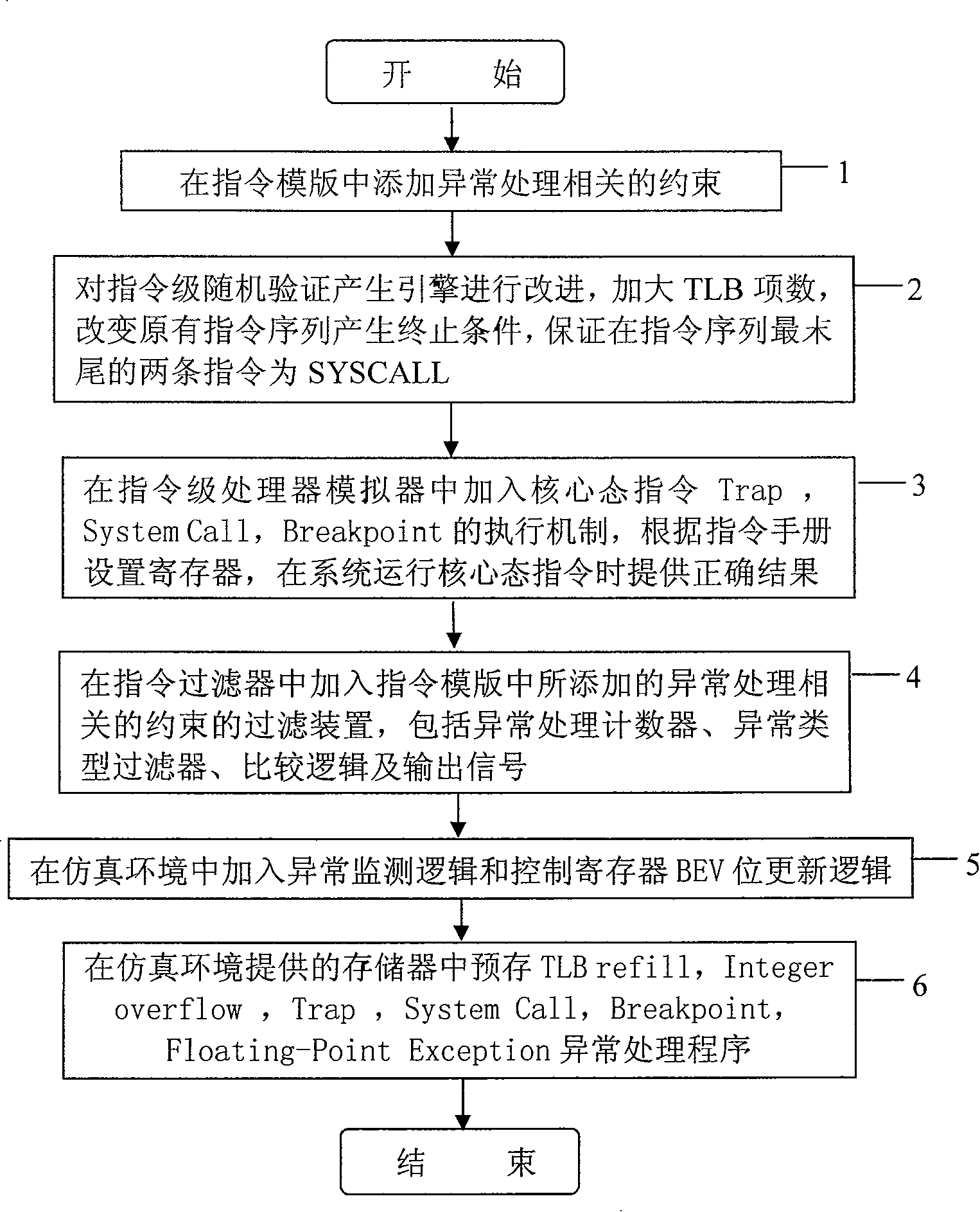

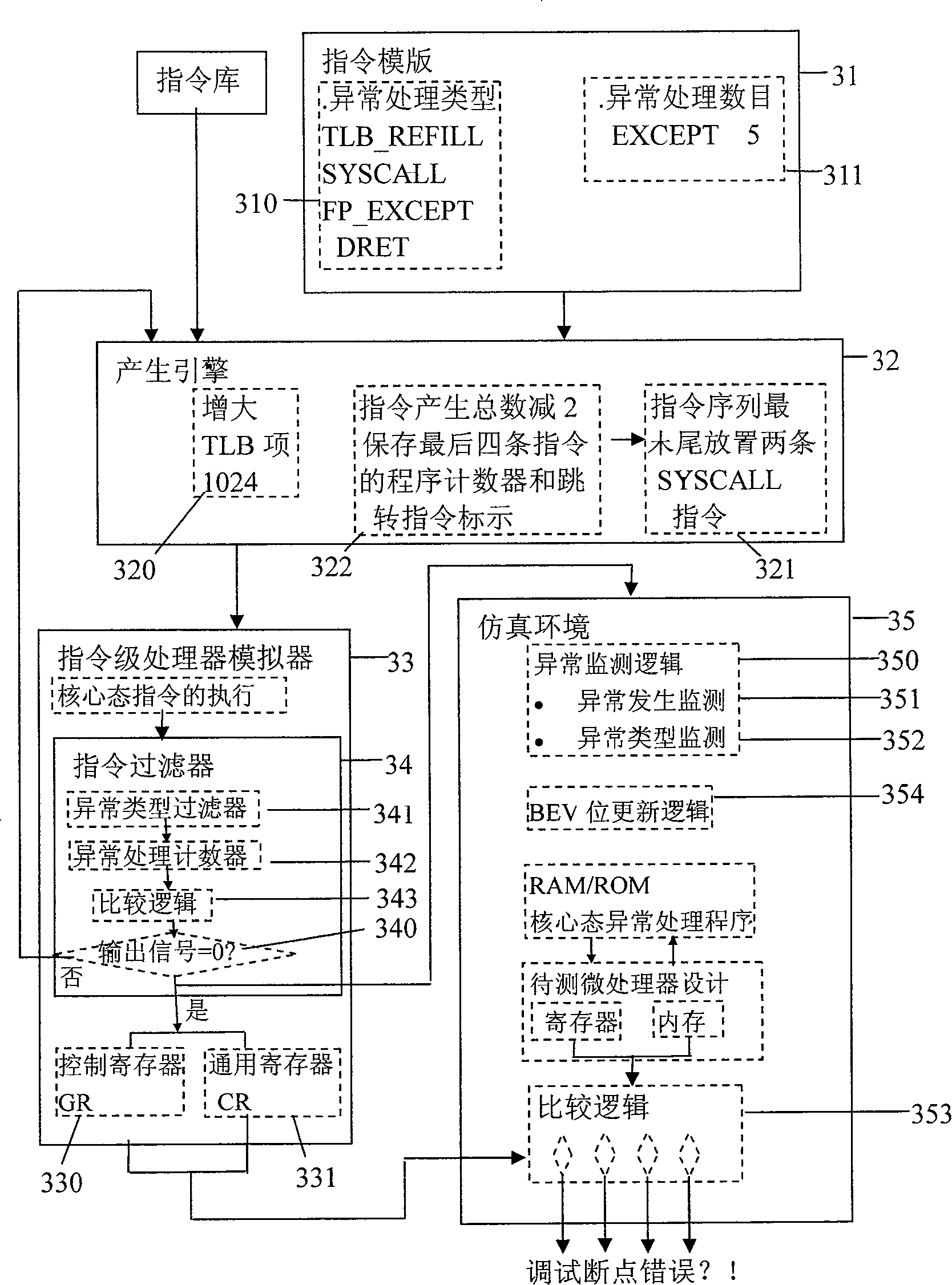

[0046] like figure 2 Shown, a kind of method that realizes kernel state program verification in microprocessor user state random verification, comprises the following steps:

[0047] Step 1, add exception handling-related constraints in the instruction template, including the type and number of exception handling allowed;

[0048] Step 2, improve the instruction-level random verification generation engine, increase the number of TLB items, change the termination condition of the original instruction sequence generation, and ensure that the two instructions at the end of the instruction sequence are SYSCALL;

[0049] Step 3, add the execution mechanism of the core state instructions Trap, System Call, and Breakpoint to the instruction-level processor simulator, set the registers according to the instruction manual, and provide correct results w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More