Asynchronous bridge and data transmission

A data transmission and asynchronous bridge technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of affecting the bus bandwidth, low bus efficiency, unable to really support burst transmission, etc., and achieve the effect of improving bus efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

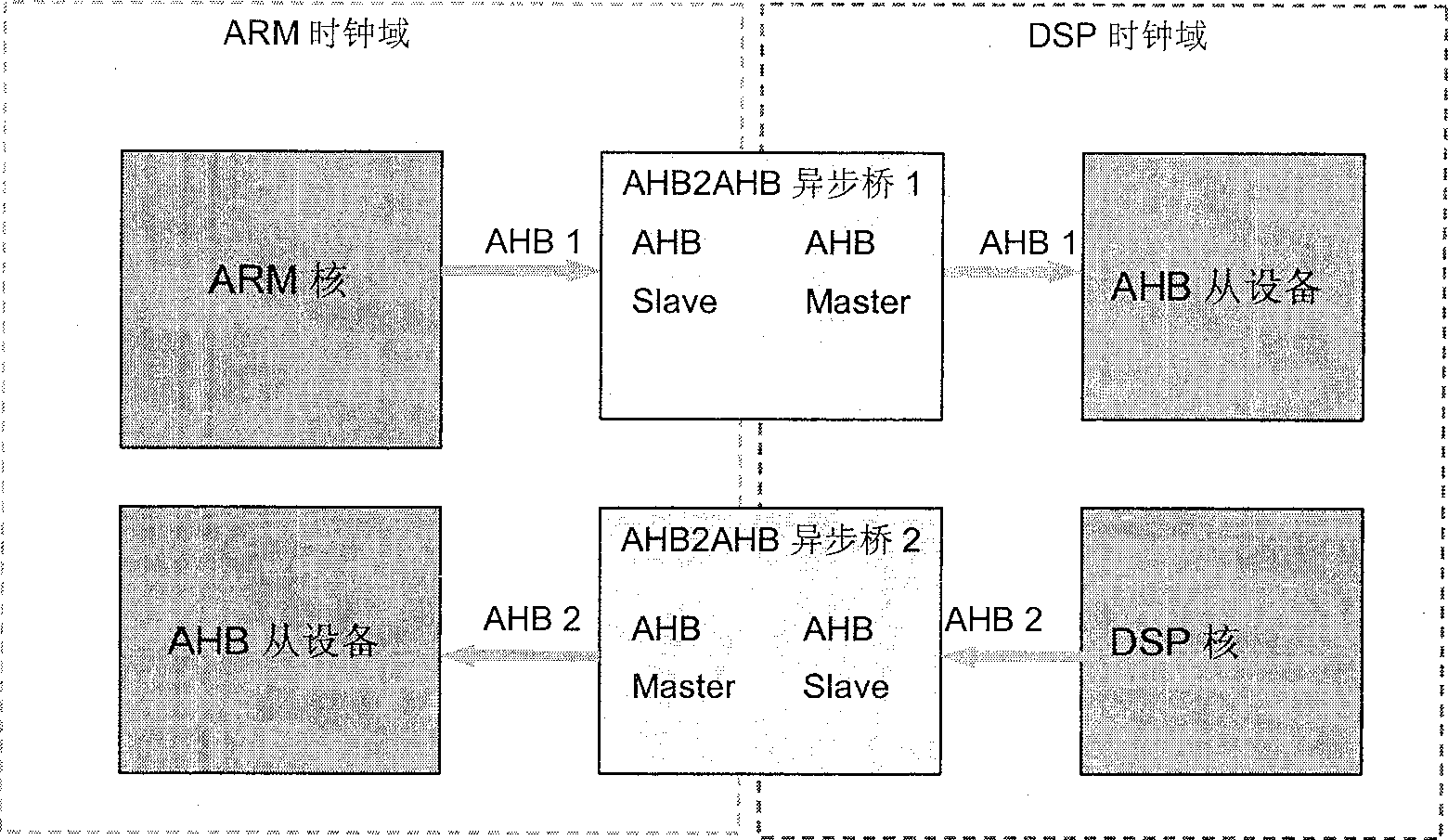

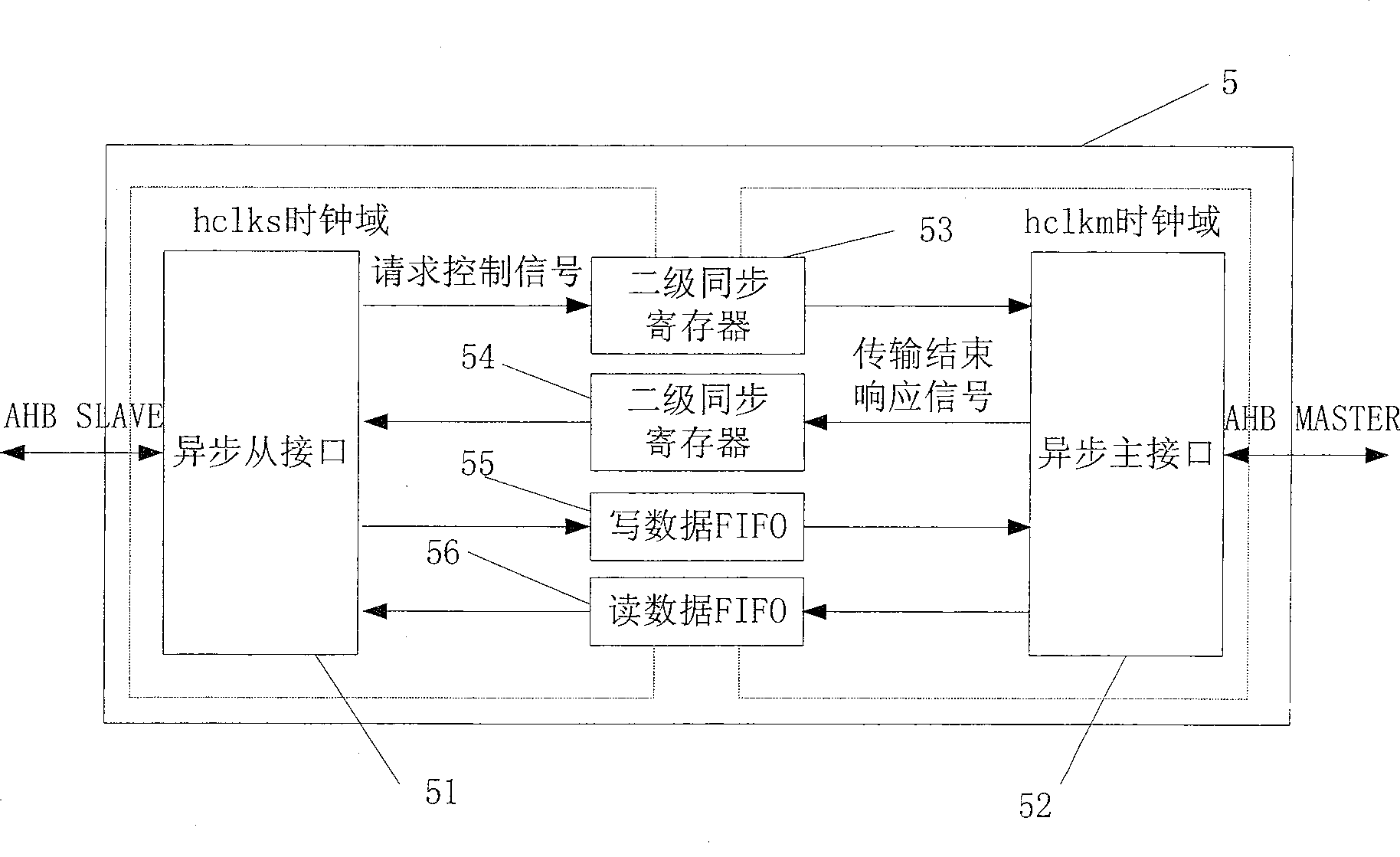

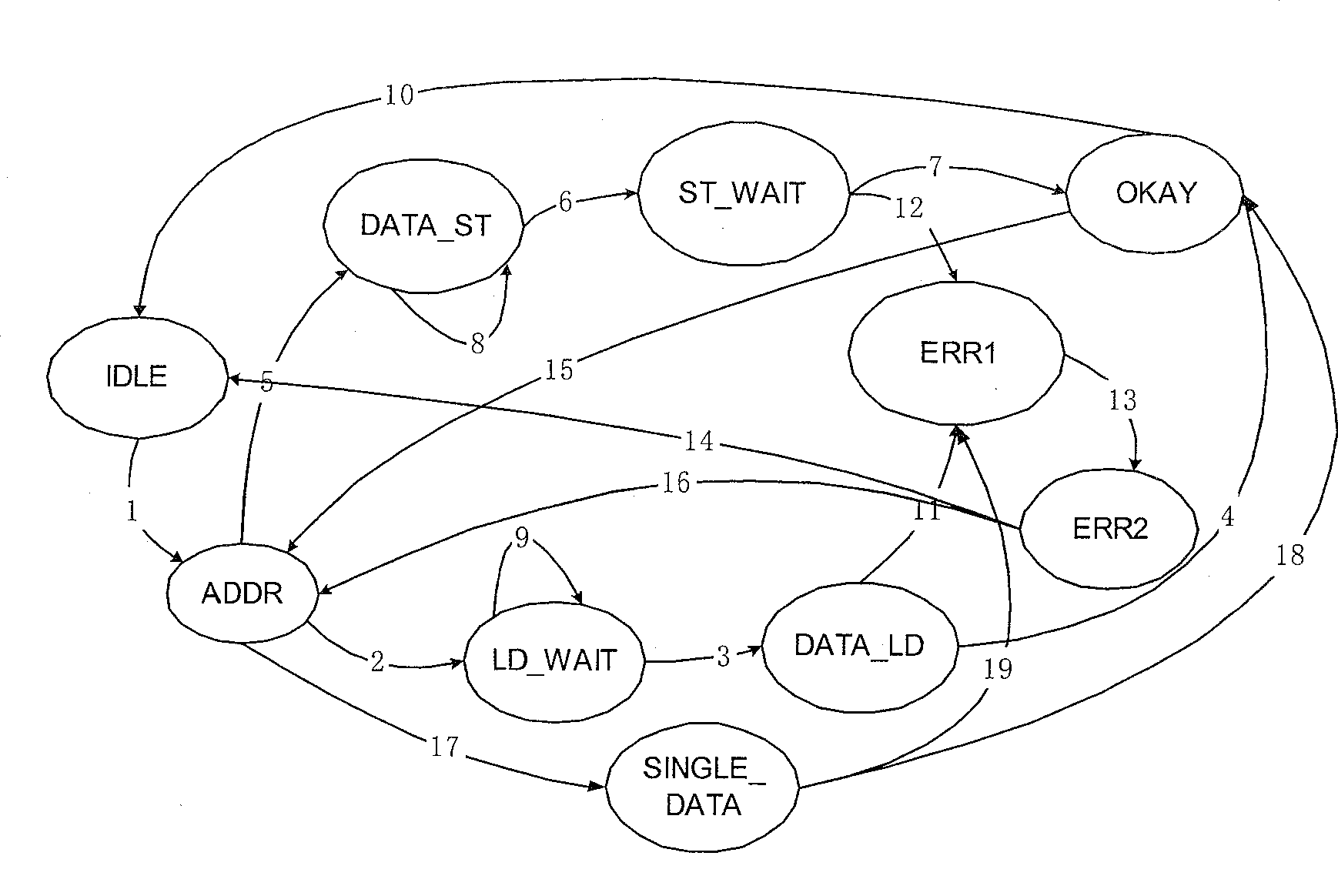

[0027] The invention provides an asynchronous bridge and a communication method thereof to solve the problem that the asynchronous bridge in the prior art needs to convert the AHB bus burst transmission into a single transmission for processing, thereby causing the bus efficiency to be too low. In the present invention, a bidirectional memory is added to the asynchronous bridge. Since the bus only processes one transmission (read transmission or write transmission) at a time, the read and write operations in burst transmission will not occur at the same time, so only one bidirectional memory can meet the needs. One end of the two-way memory is connected to the asynchronous slave interface, and the other end is connected to the asynchronous master interface for storing data signals during burst transmission of the AHB bus. The asynchronous slave interface and the asynchronous master interface communicate with each other through the two-way The memory performs read and write control...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More