Patents

Literature

43results about How to "Improve bus efficiency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

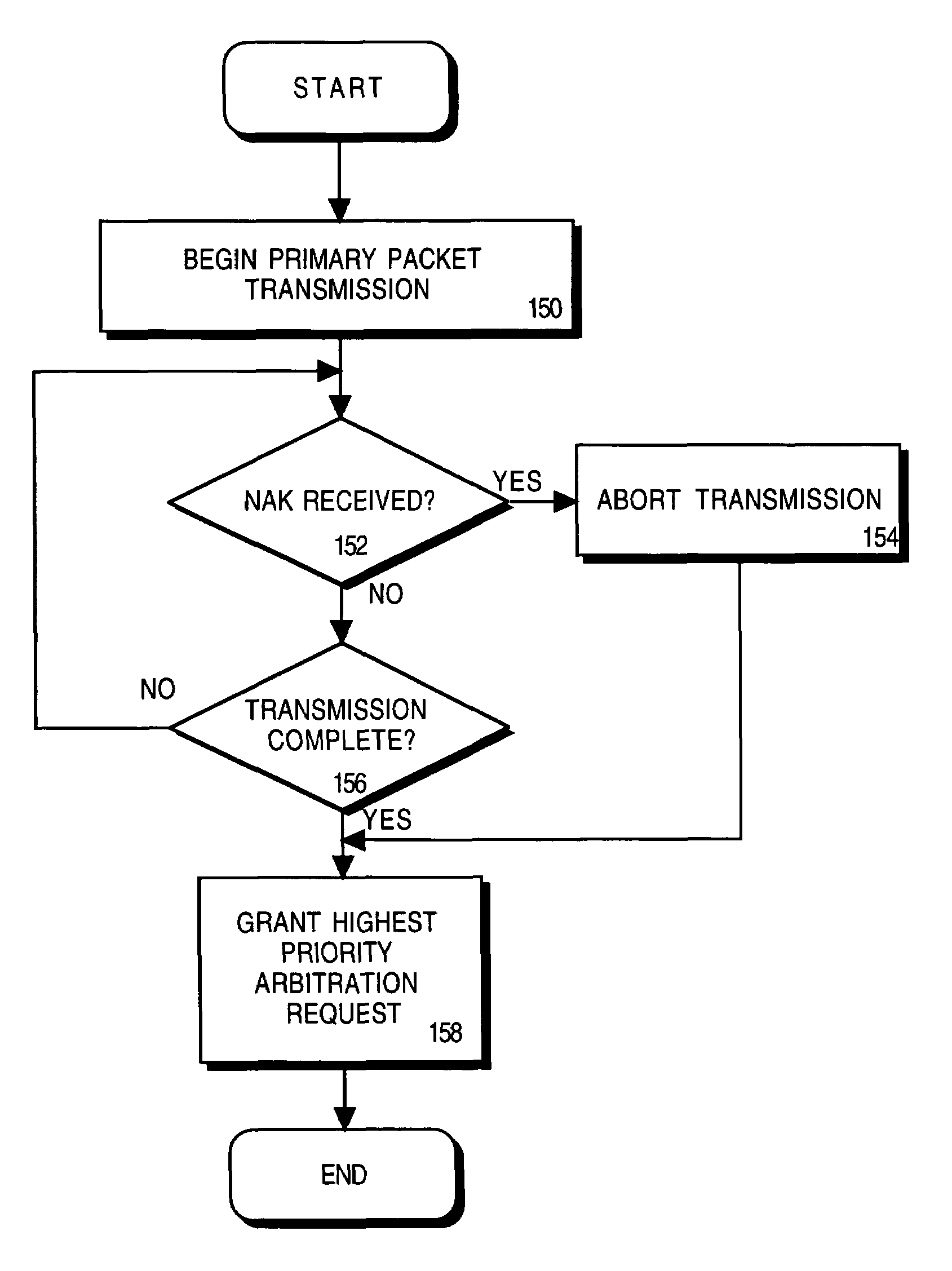

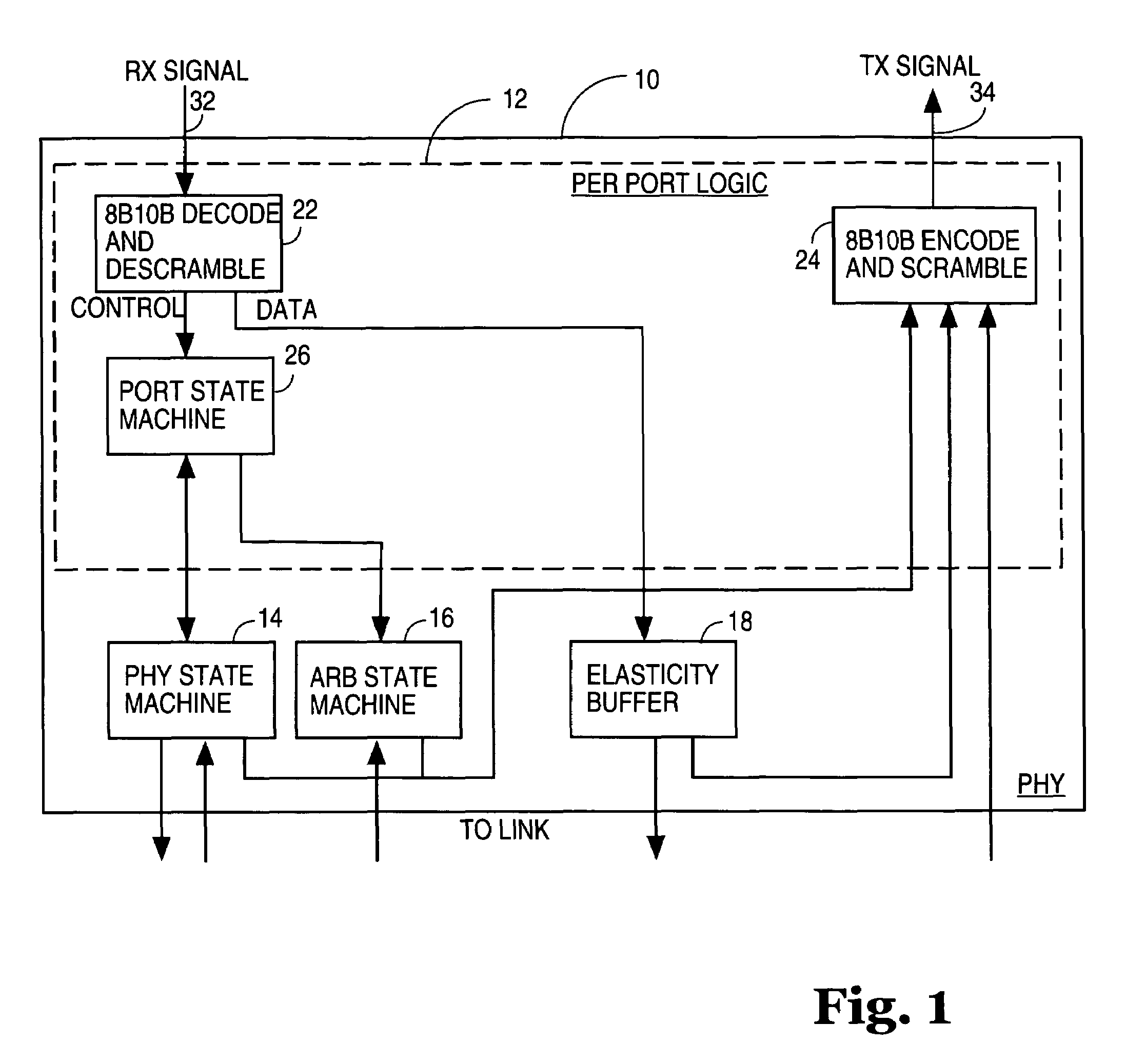

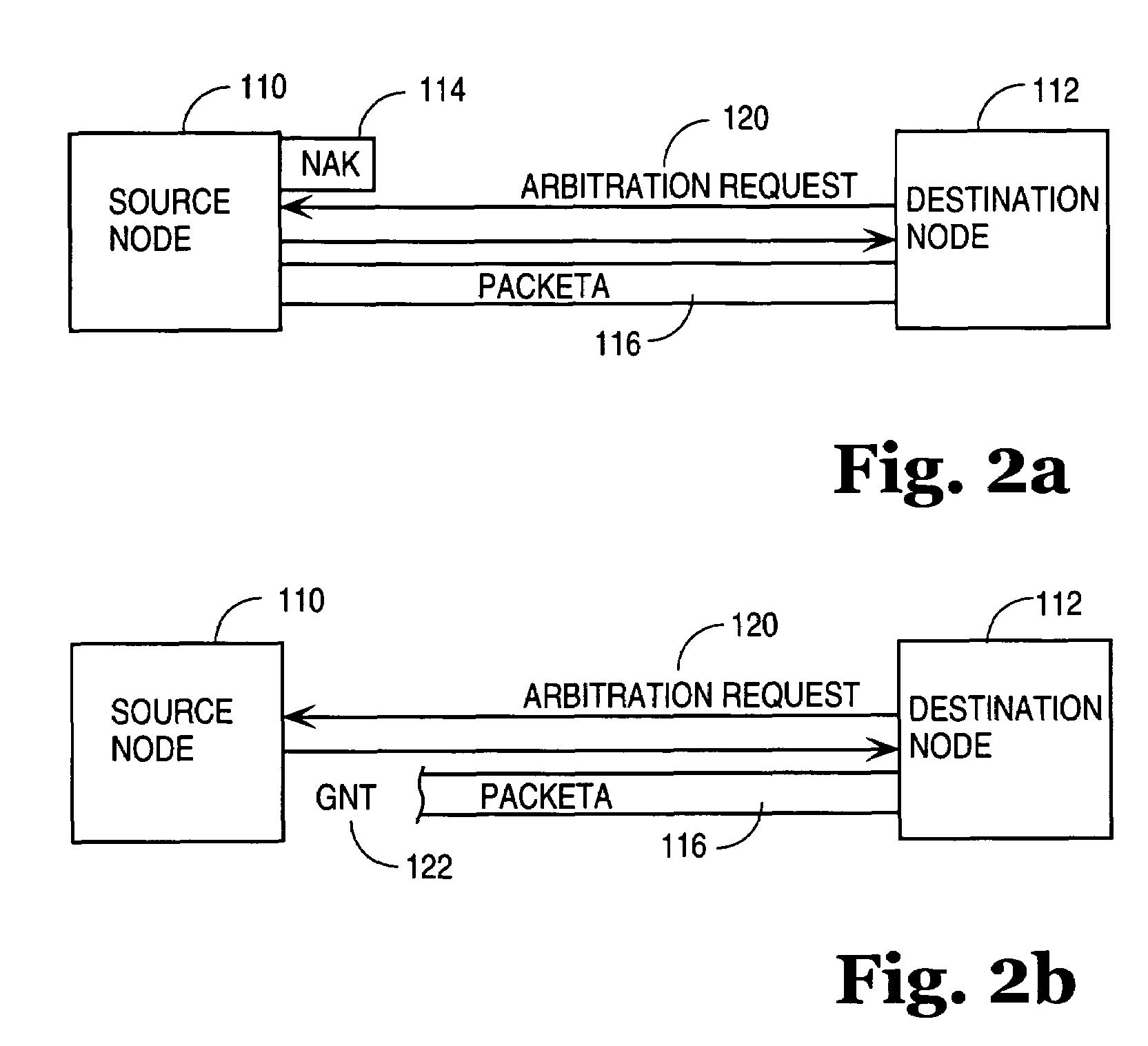

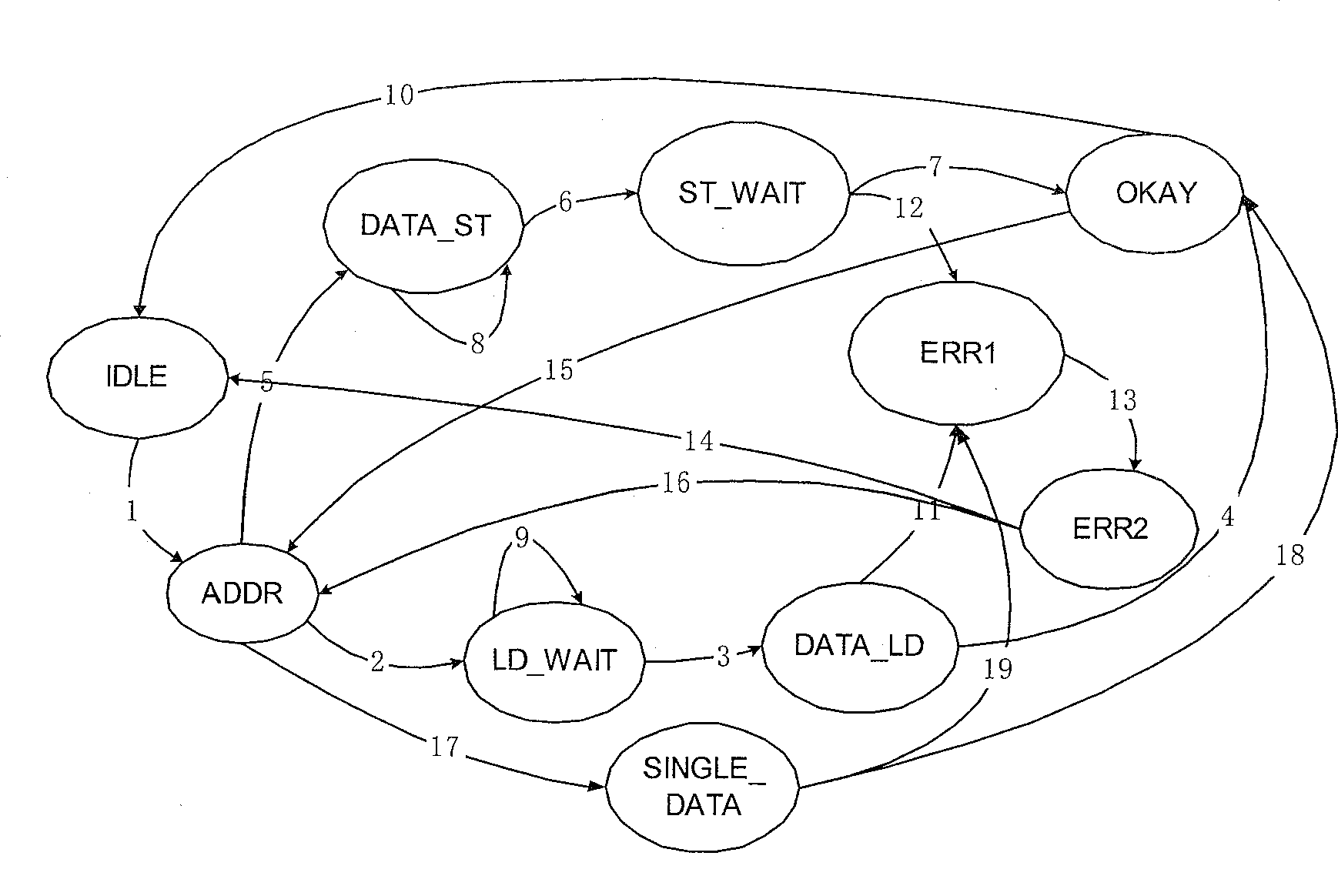

Early acknowledgement of primary packets

InactiveUS7076716B1Improve bus efficiencyError prevention/detection by using return channelTransmission systemsSodium-potassium alloyPacket transmission

A method and apparatus for reclaiming bus bandwidth on a full duplex bus. A source node sends a primary packet toward a destination node along a full duplex bus. If the destination node identifies an inability to accept the primary packet, it sends a NAK in the opposite direction along the full duplex bus towards the source node. Upon receiving the NAK, the source node aborts packet transmission of the primary packet which by virtue of the NAK has been identified as futile. Accordingly, the bandwidth, which would have otherwise have been used for the futile packet transmission, can be reclaimed and used for some other purpose.

Owner:INTEL CORP

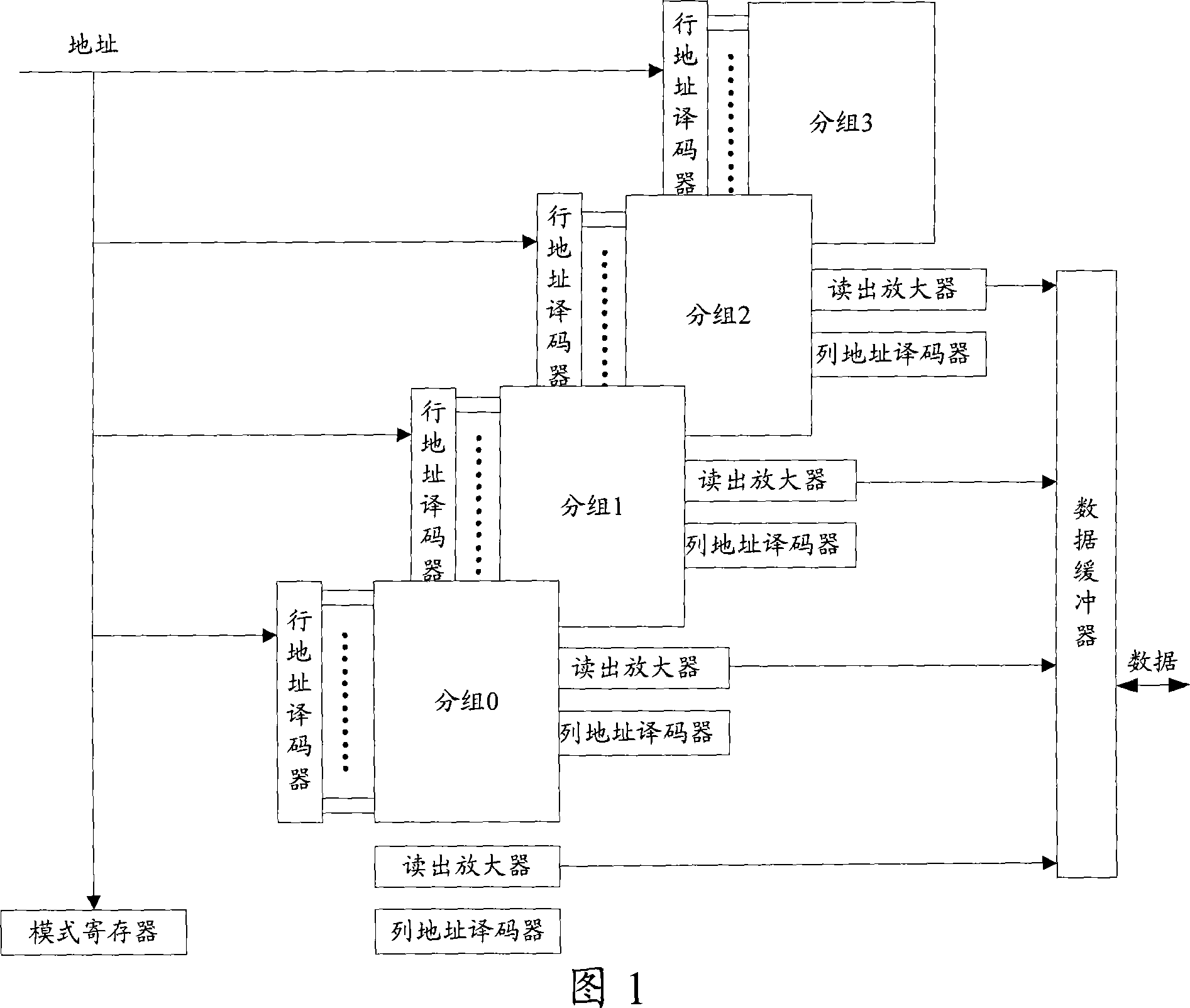

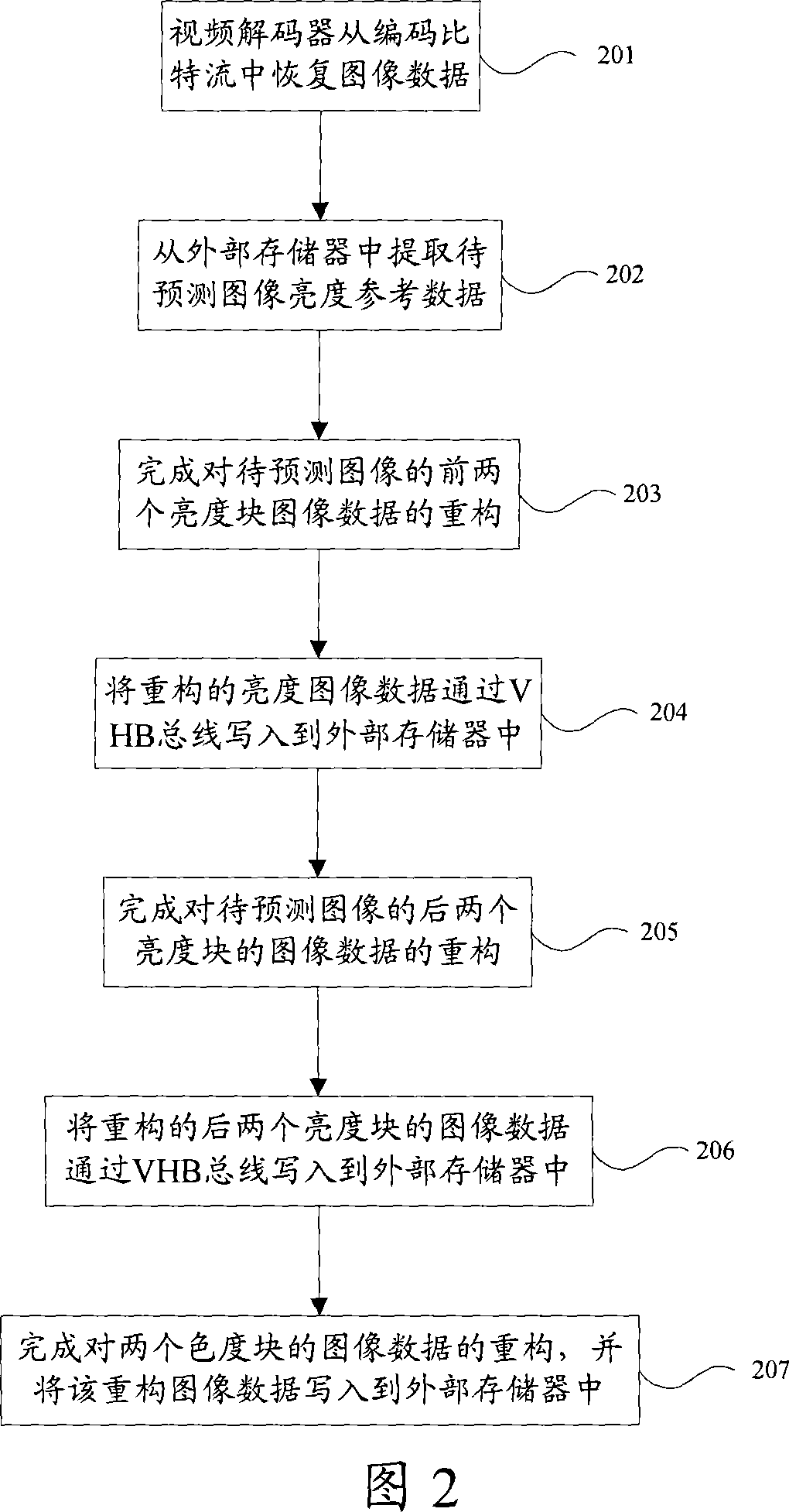

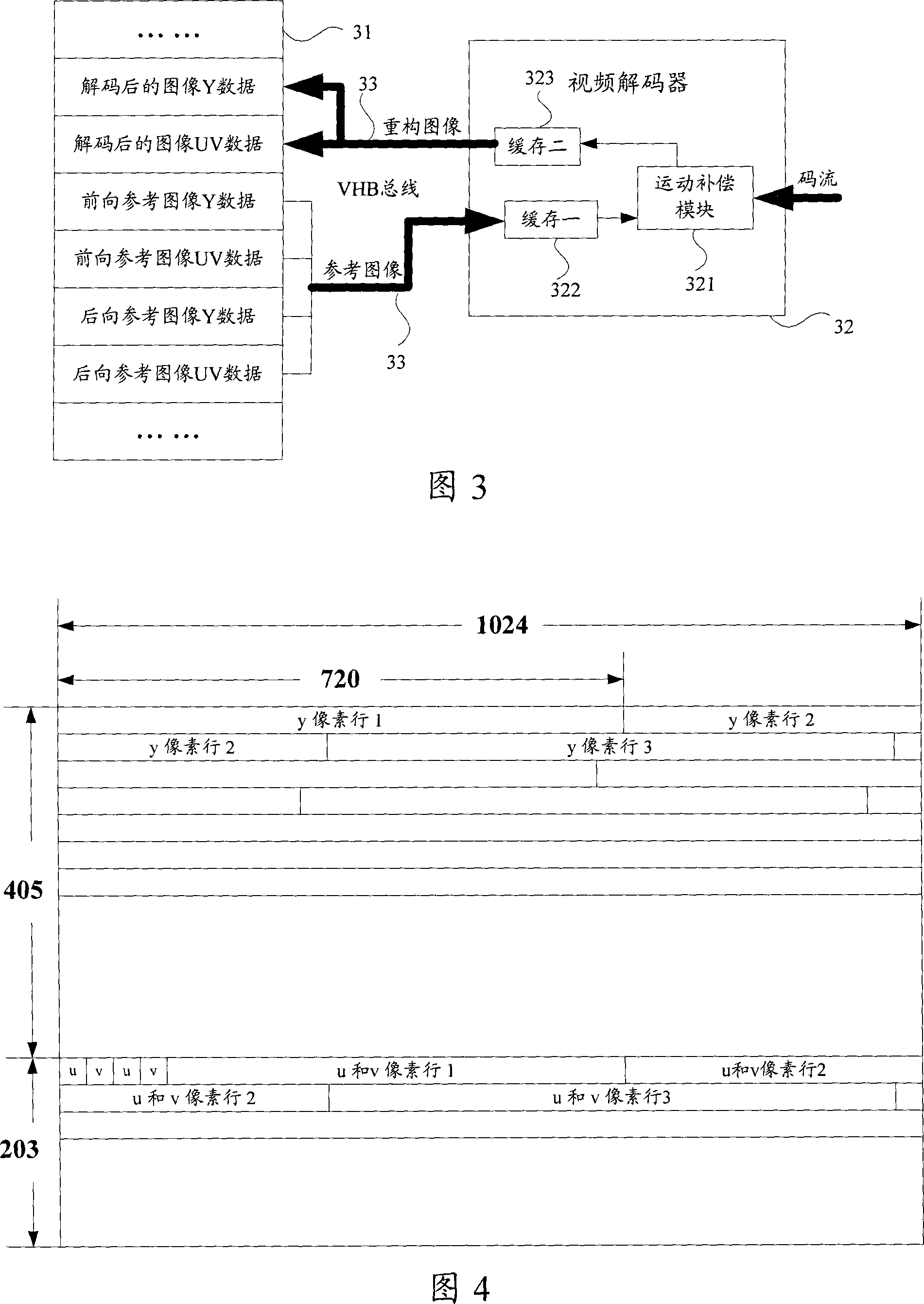

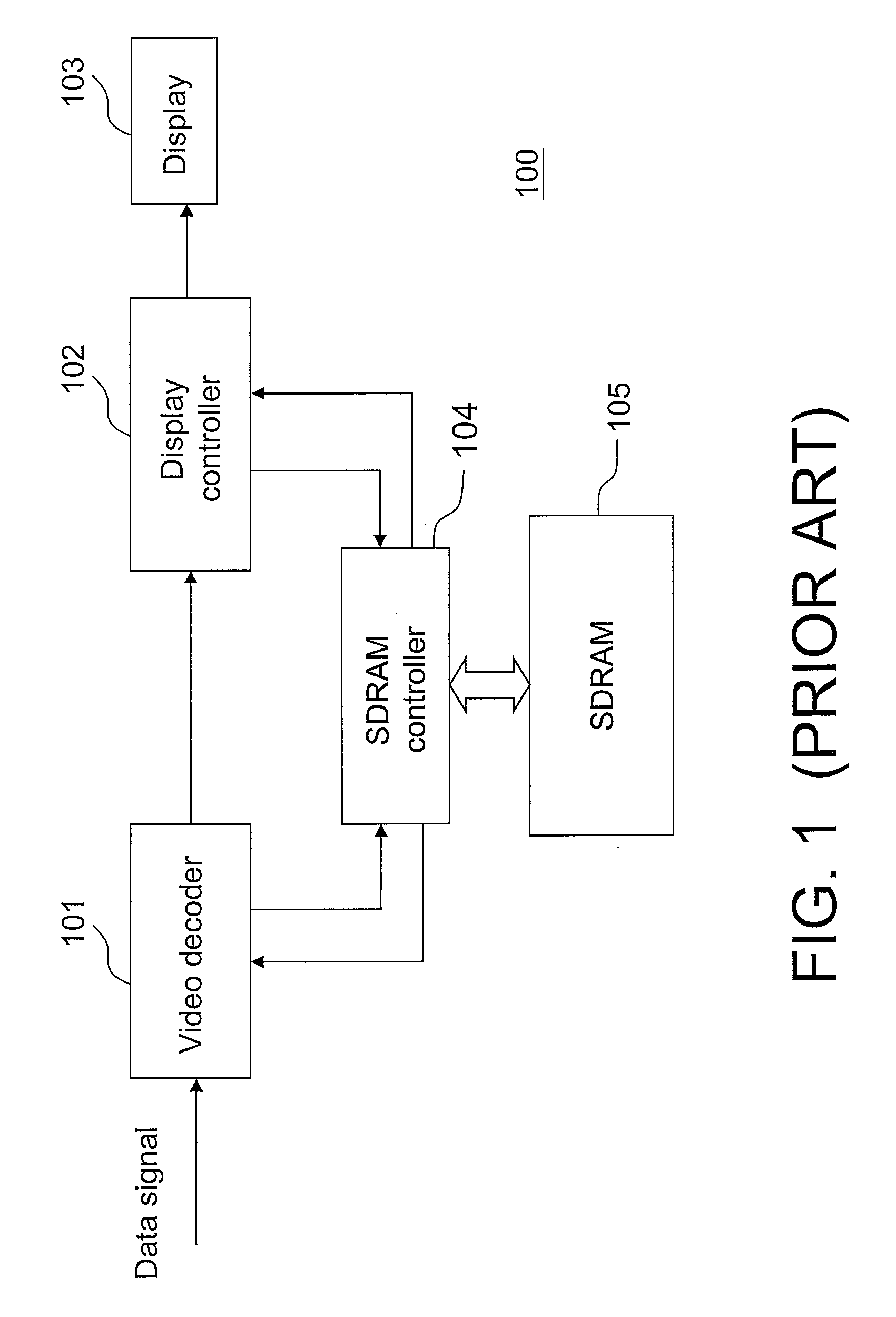

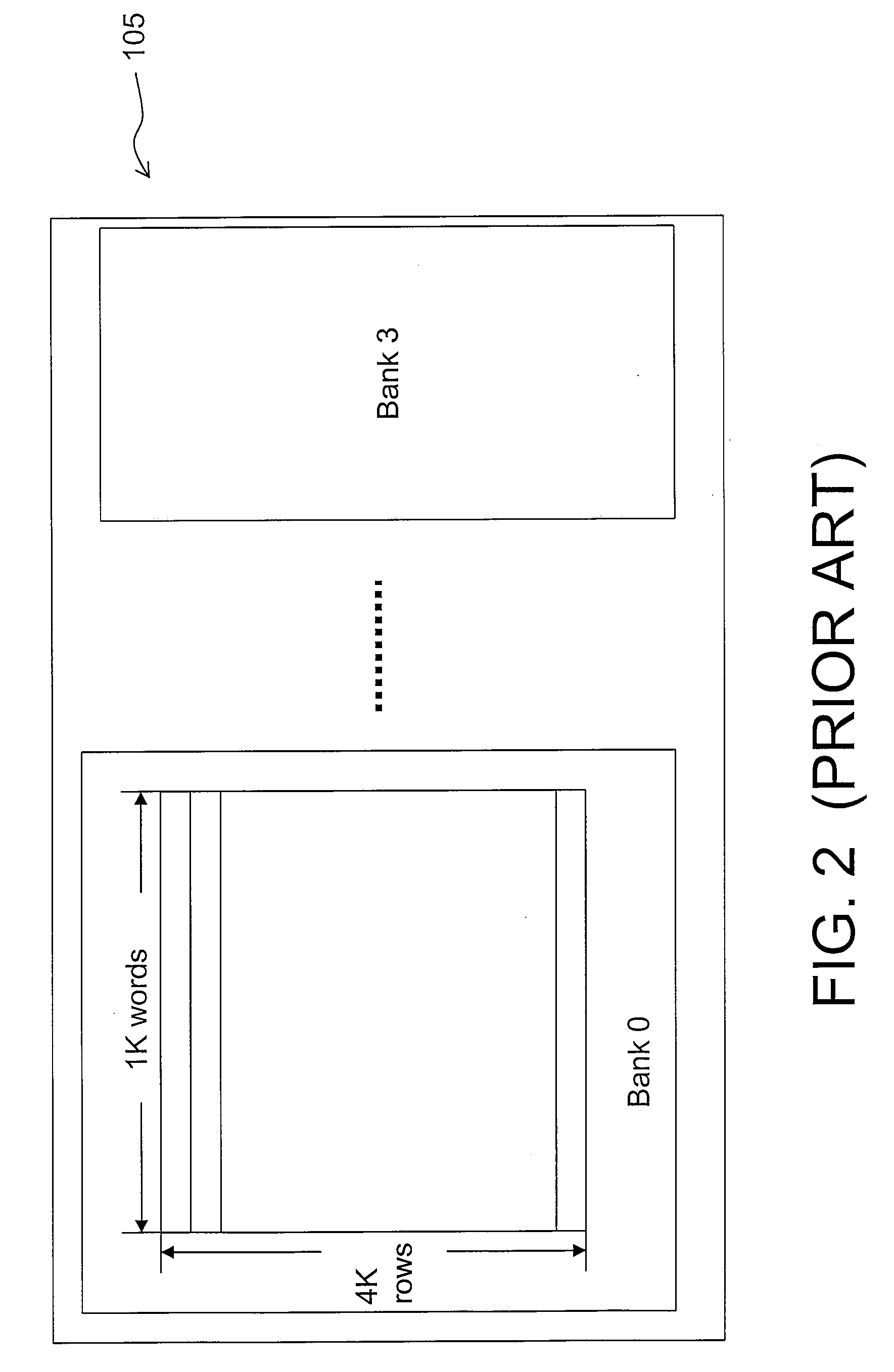

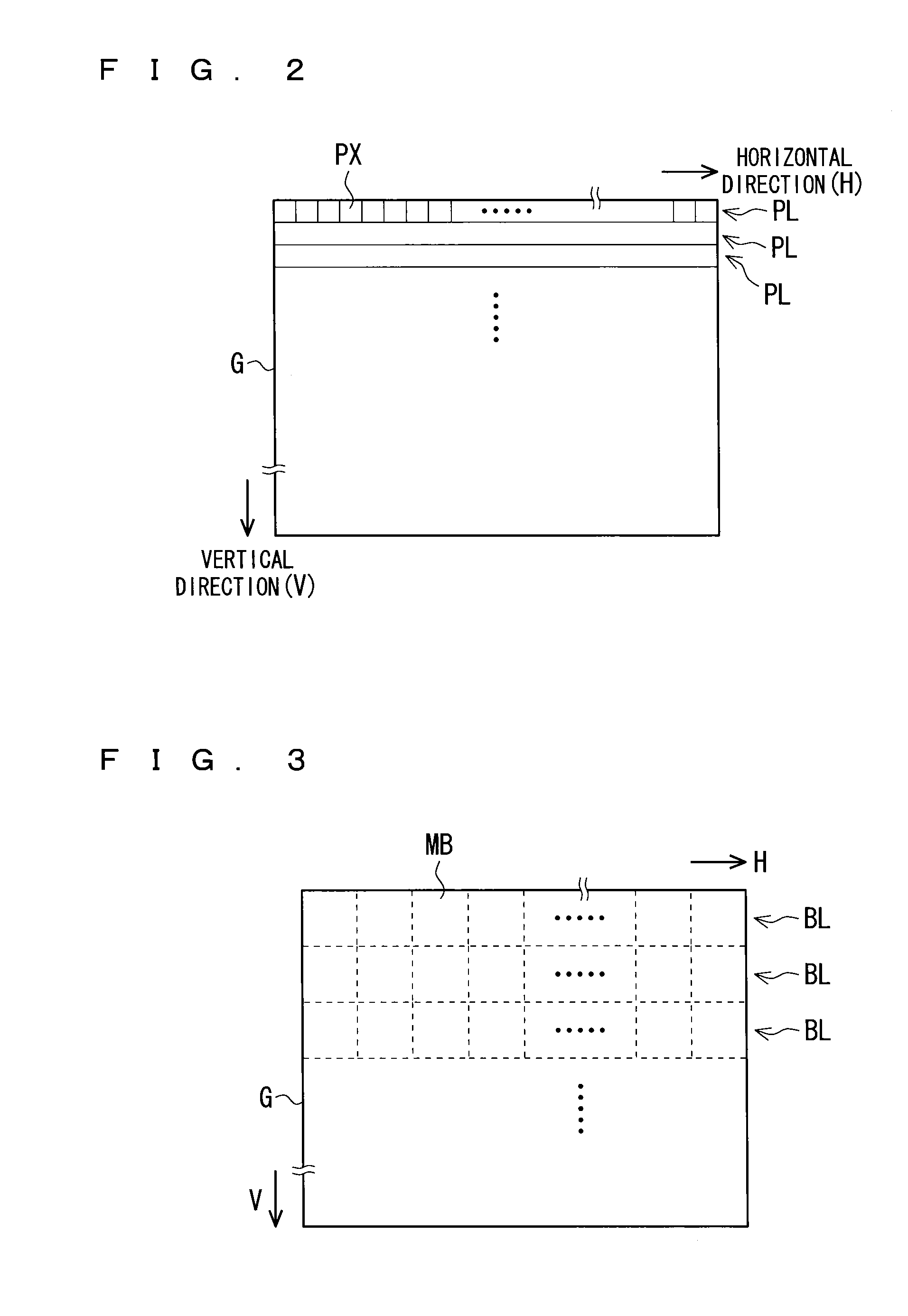

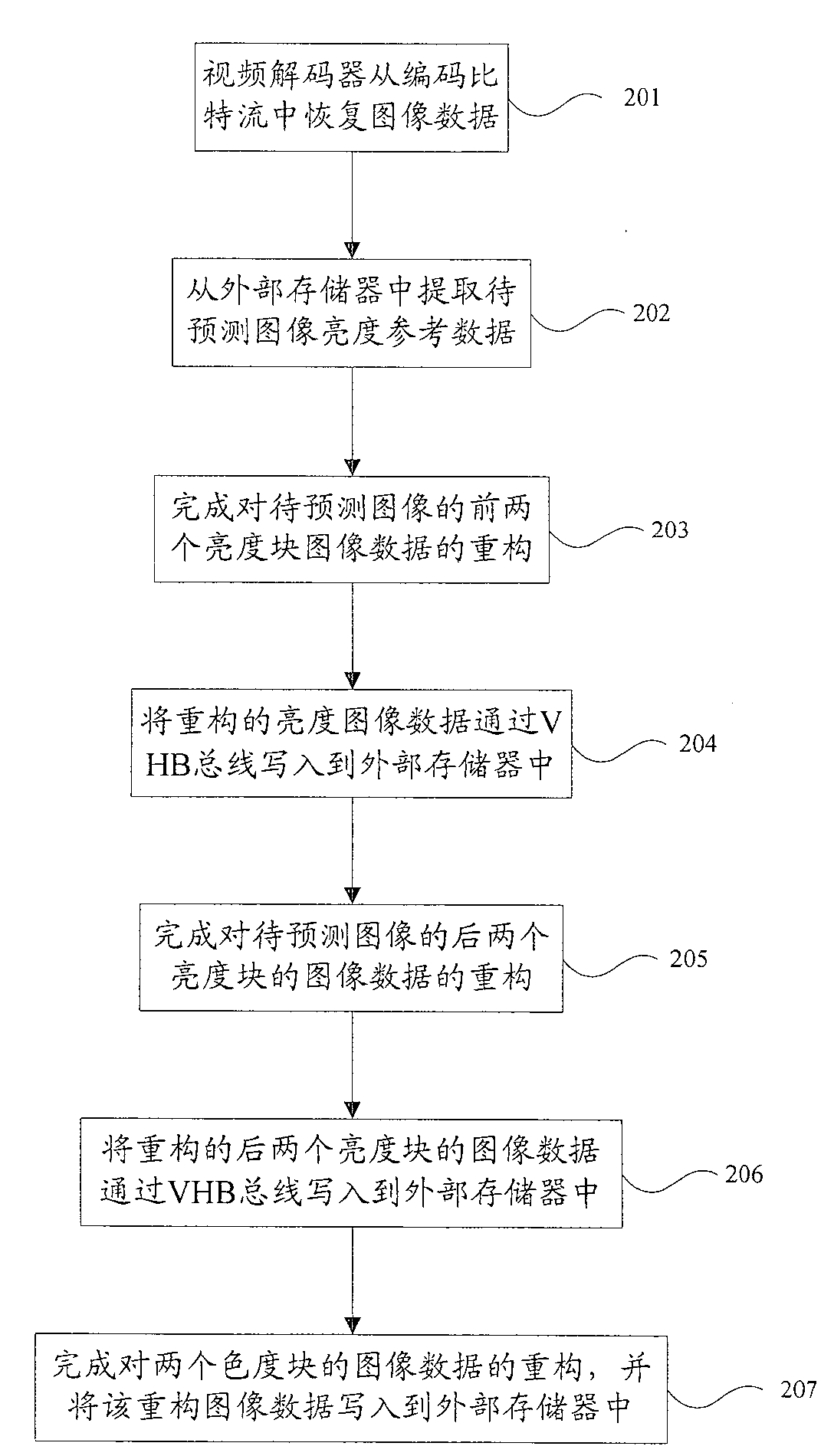

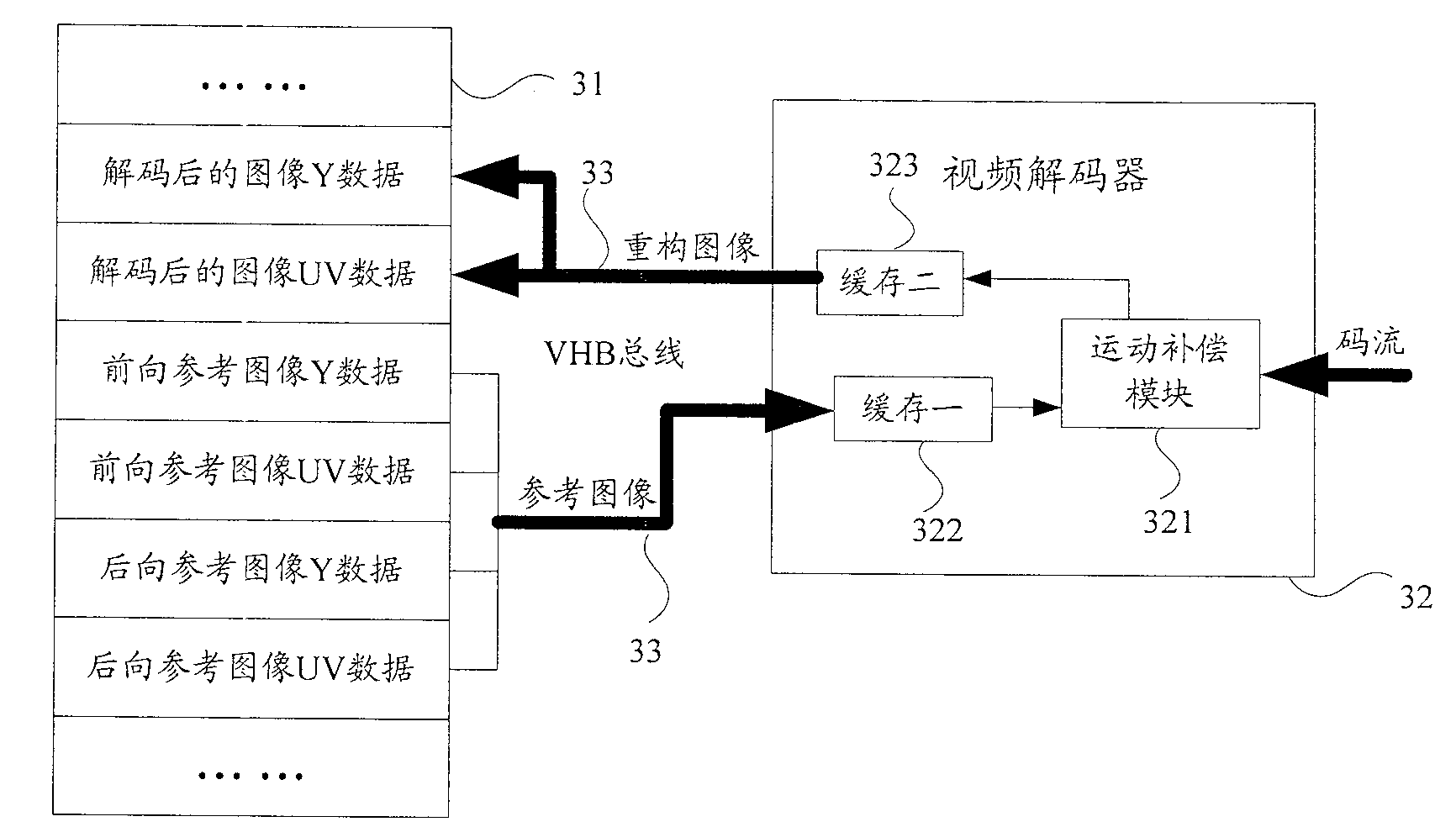

Image data accessing and decoding method and decoding device

ActiveCN101022553AIncrease profitReduce areaColor signal processing circuitsBrightness and chrominance signal processing circuitsAccess methodVideo decoder

An access method of image data includes storing multiple pixel line of image block into one line of storage space, automatically switching line when storage edge in met and calculating composite address of said image block, continuously storing data of the other image block at blank position of this line storage space if a line space in not fully occupied by data of said image block, picking up data of said image block according to composite address of said image block. Two decoding methods of image data and their devices are also disclosed.

Owner:HUAWEI TECH CO LTD

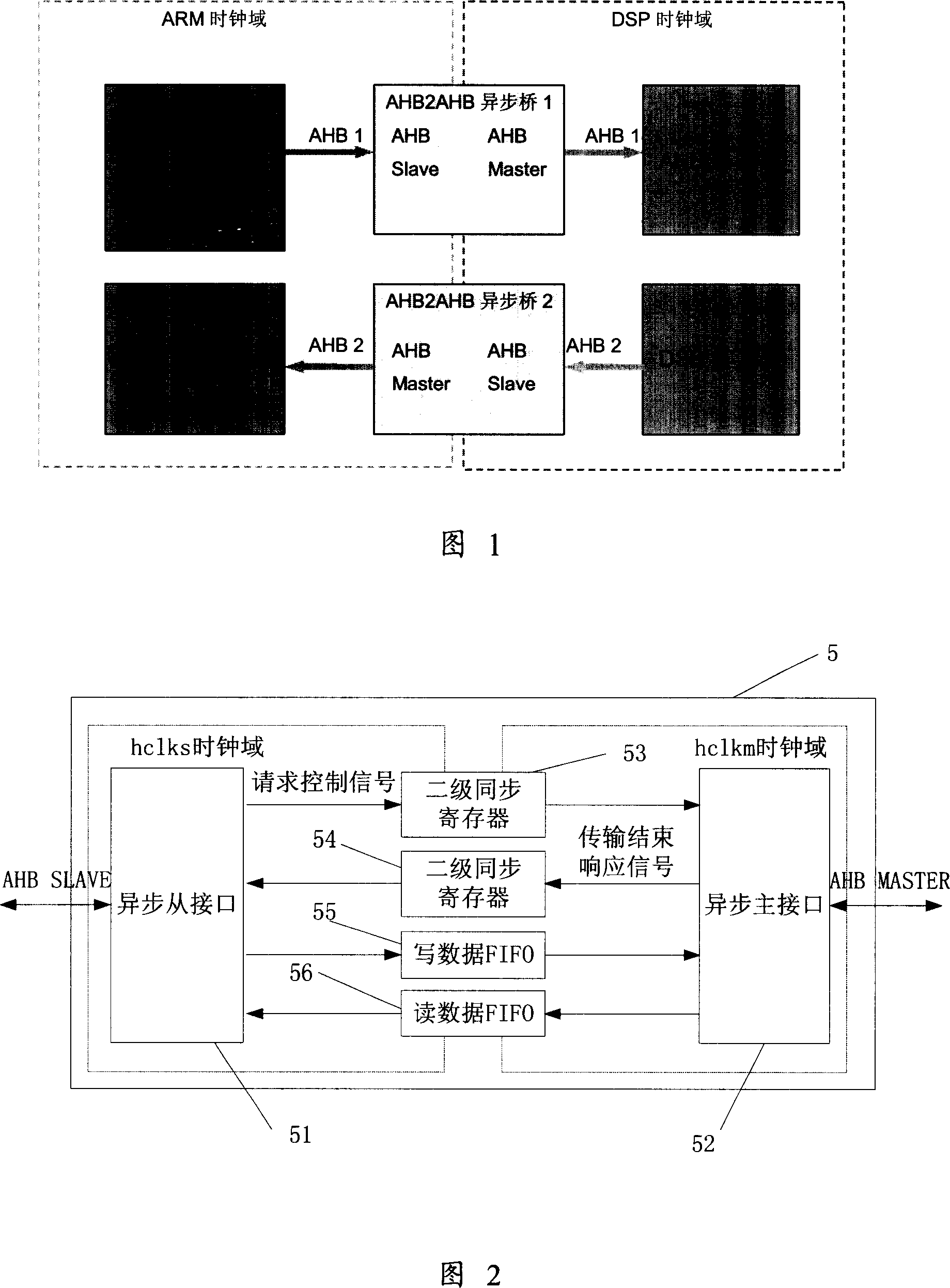

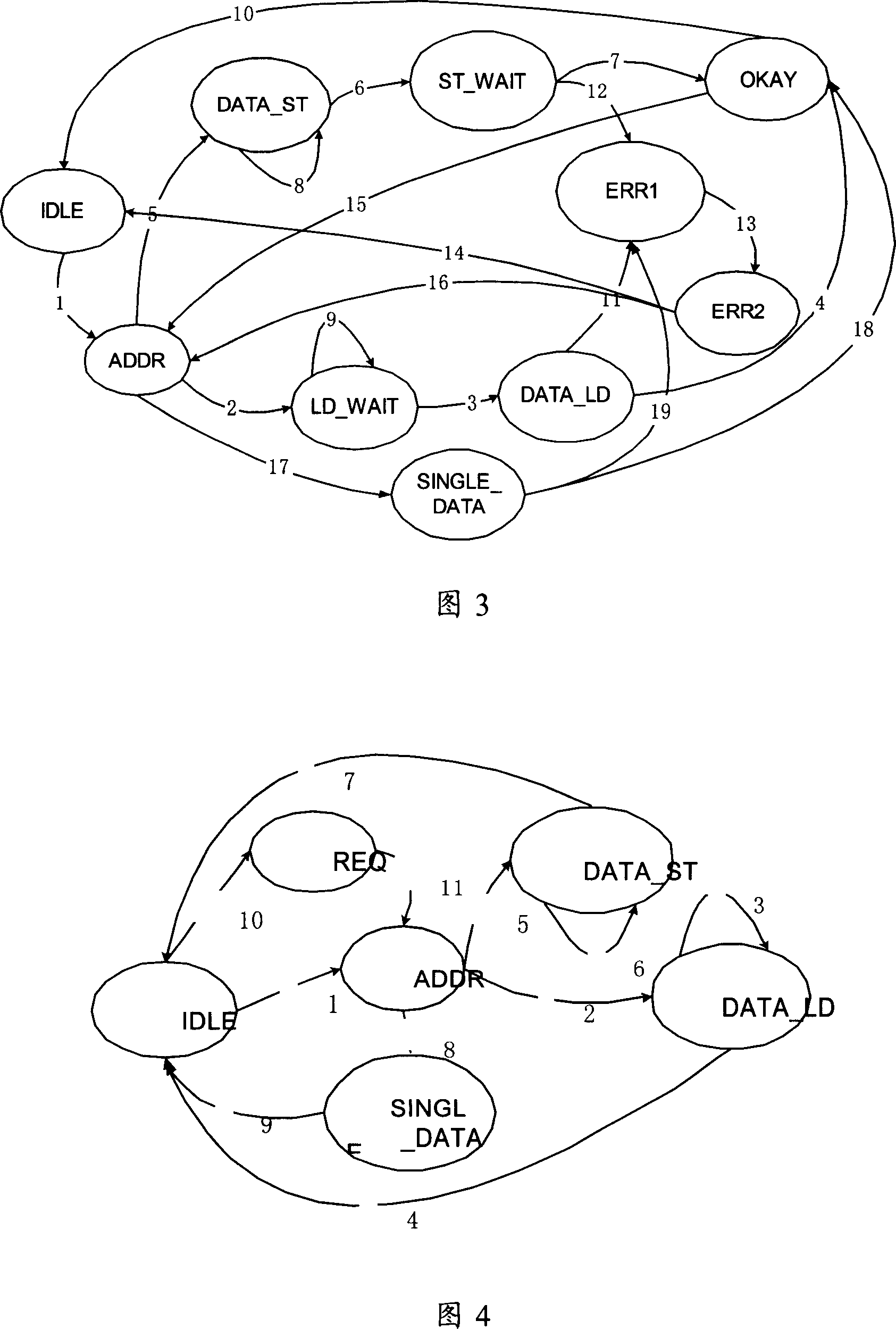

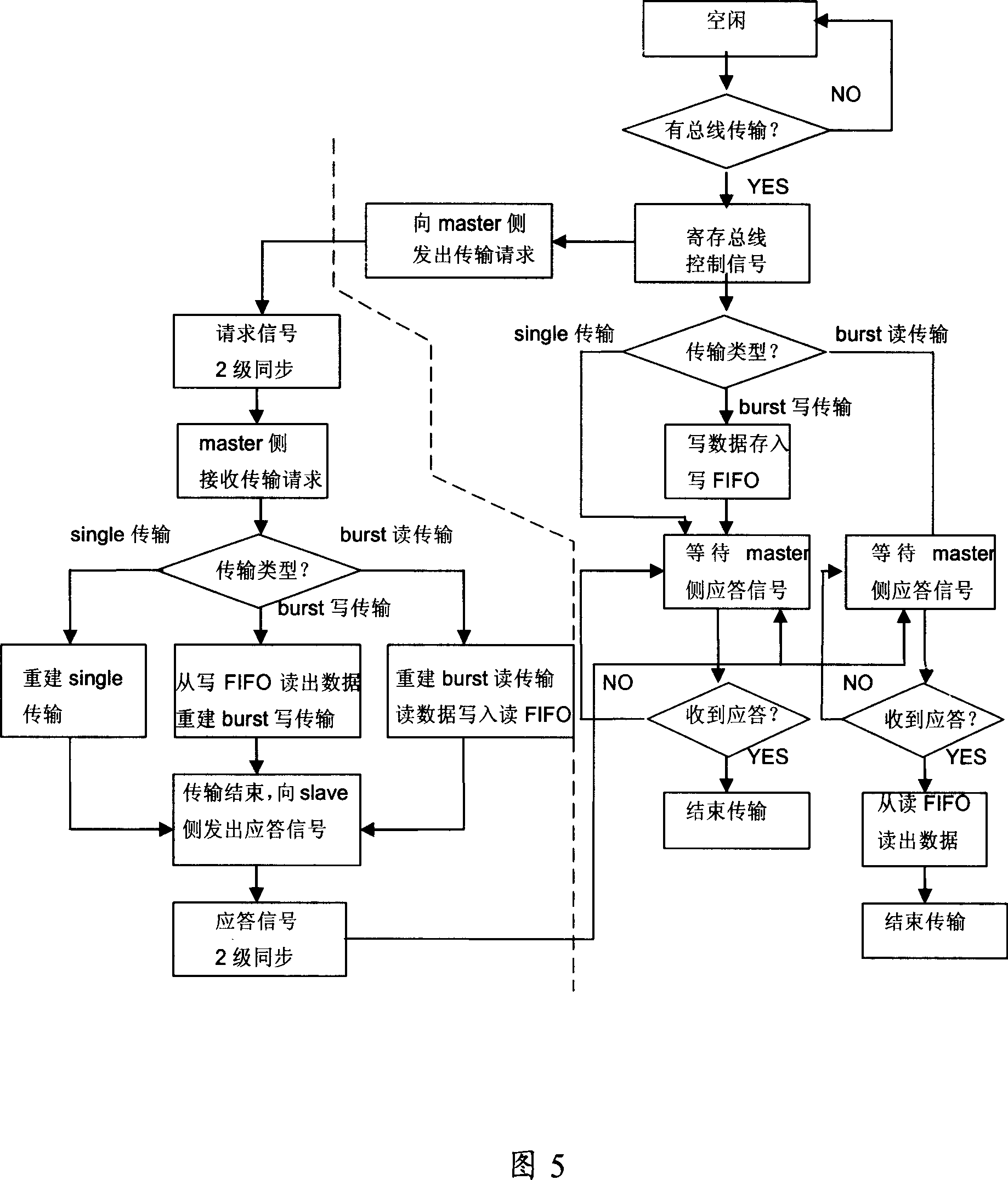

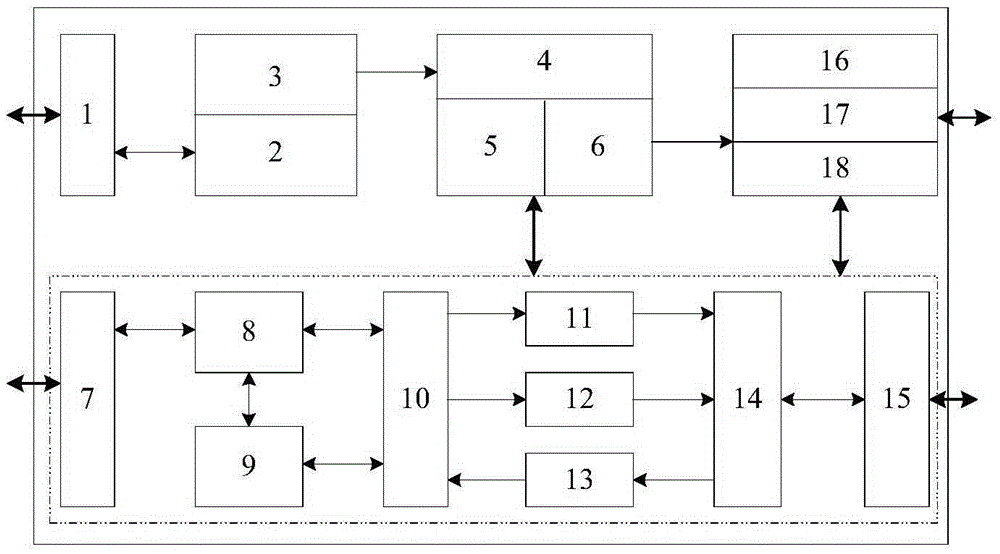

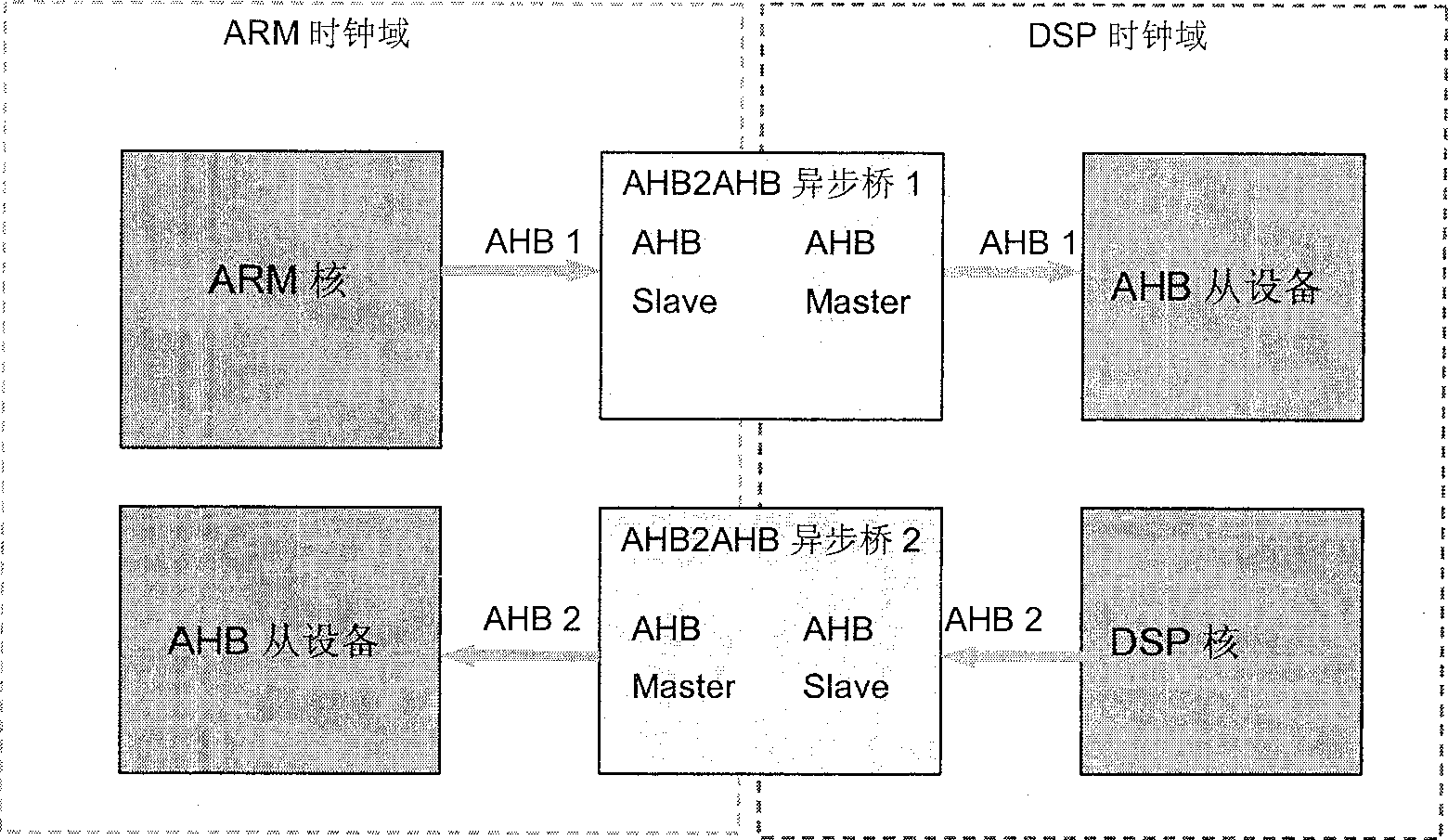

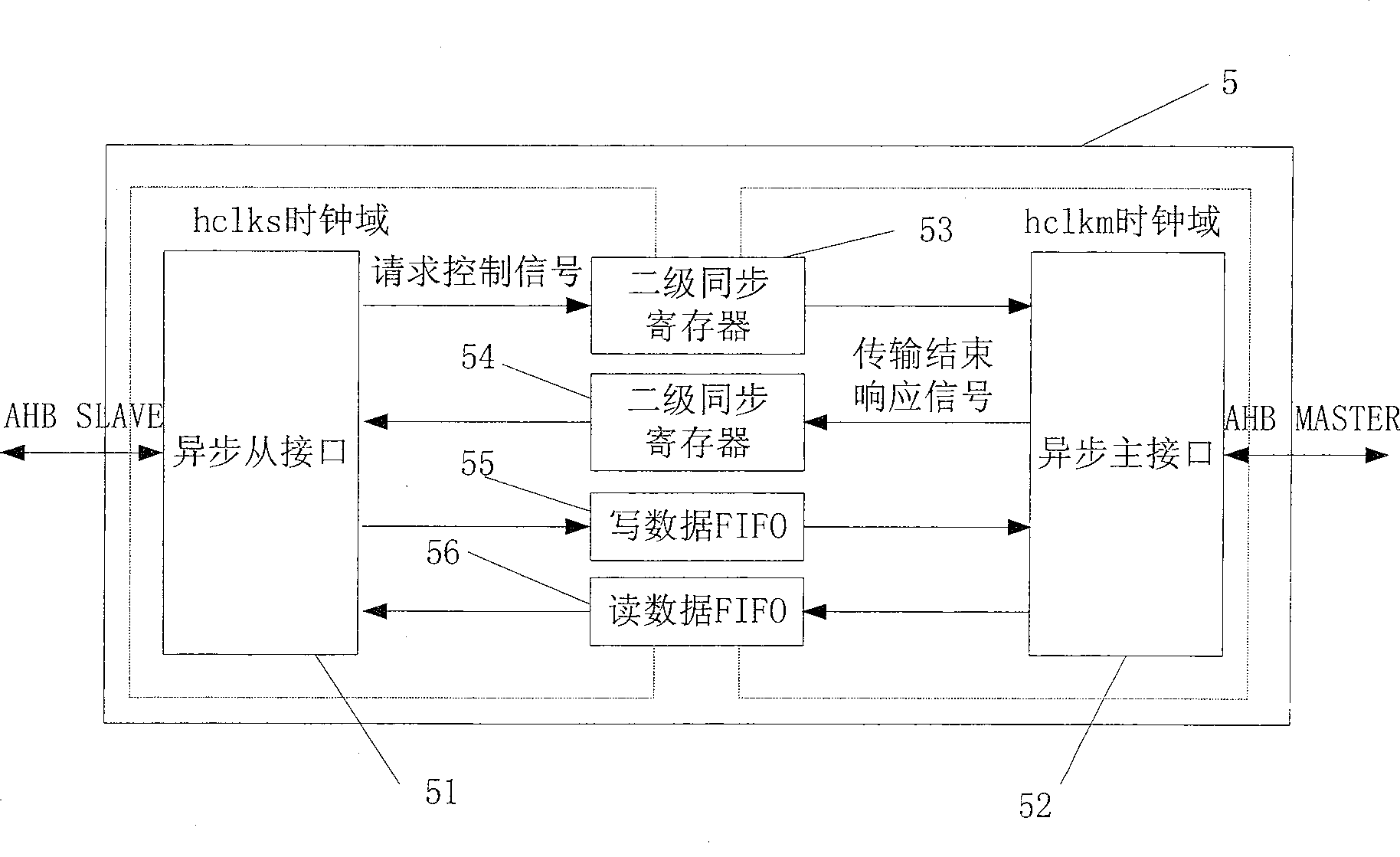

Asynchronous bridge and data transmission

ActiveCN1983223AImplementation supportImprove bus efficiencyElectric digital data processingBurst transmissionData signal

A asynchronous bridge consists of asynchronous slave interface for emitting transmission request signal, secondary synchronous unit for secondary-synchronizing said transmission request signal, asynchronous master interface for setting up bus transmission of the second clock domain, two-way storage with its one end being connected to asynchronous slave interface and another end being connected to asynchronous master interface for storing data signal of bus burst transmission. Its data transmitting method is also disclosed.

Owner:HUAWEI TECH CO LTD

PCI (Peripheral Component Interconnect) bus controller and control method thereof

ActiveCN105224488AFlexible useMeet different requirementsElectric digital data processingProgrammable read-only memoryDirect memory access

The invention discloses a PCI (Peripheral Component Interconnect) bus controller and a control method thereof. Through SPI (Serial Peripheral Interface) signal multiplexing, two configuration information initialization ways including EEPROM (Electrically Erasable Programmable Read-Only Memory) loading or unloading are provided so as to be flexible in use; and through the arrangement of a plurality of interface modules, a SPI bus, a PCI bus, a Local bus and corresponding pin interfaces can be realized. The PCI bus controller can be used as PCI master / slave equipment, has a wide application range and meets different requirements of a system; and when the PCI bus controller is used as the PCI master equipment, DMA (Direct Memory Access) data transmission is carried out, CPU (Central Processing Unit) intervention is avoided, and system efficiency is improved. When the PCI bus controller is used as the PCI bus master equipment to initiate a bus operation, data interaction between system memory and Local equipment is finished; and during non DMA transmission, the PCI bus controller is used as the PCI bus slave equipment to response to the bus operation. The PCI bus controller provides 8-bit, 16-bit, 32-bit multiplex / non-multiplex Local bus interfaces, can configure and realize various working ways including emergency, prefetching, internal waiting, external waiting, write cycle maintaining, read-write gating delay, big end and small end alignment, local chip selection, local interruption and the like, and is high in universality.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

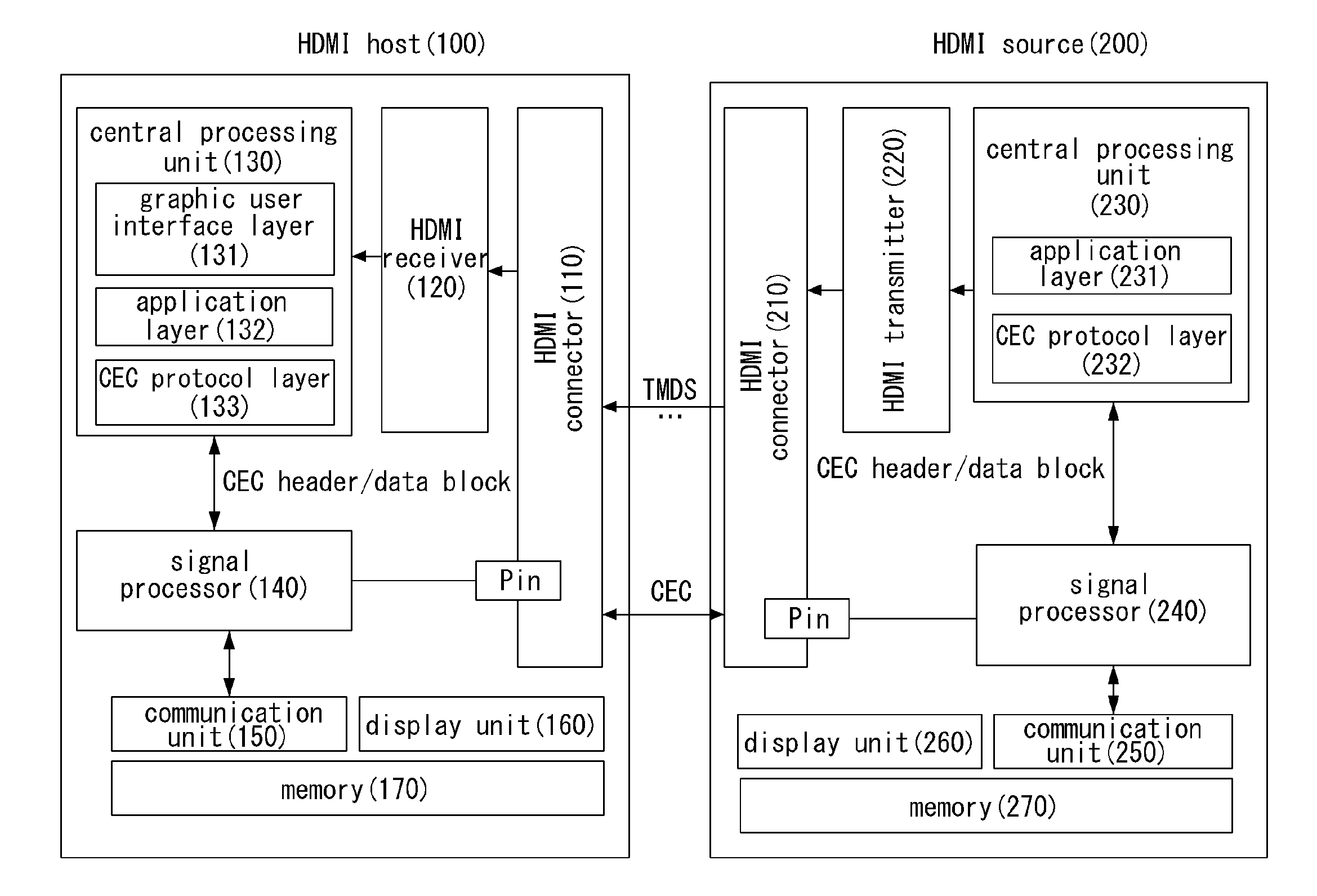

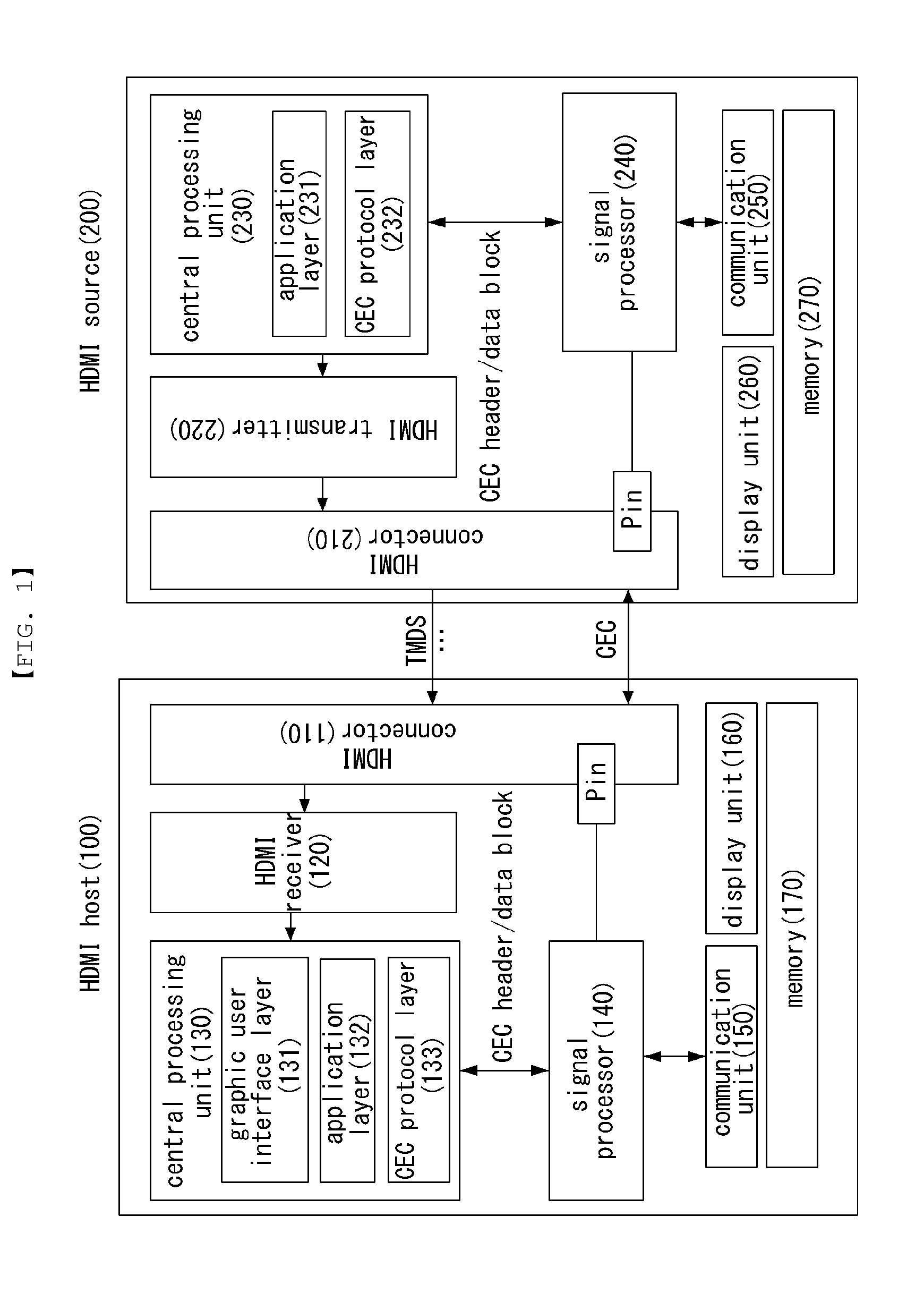

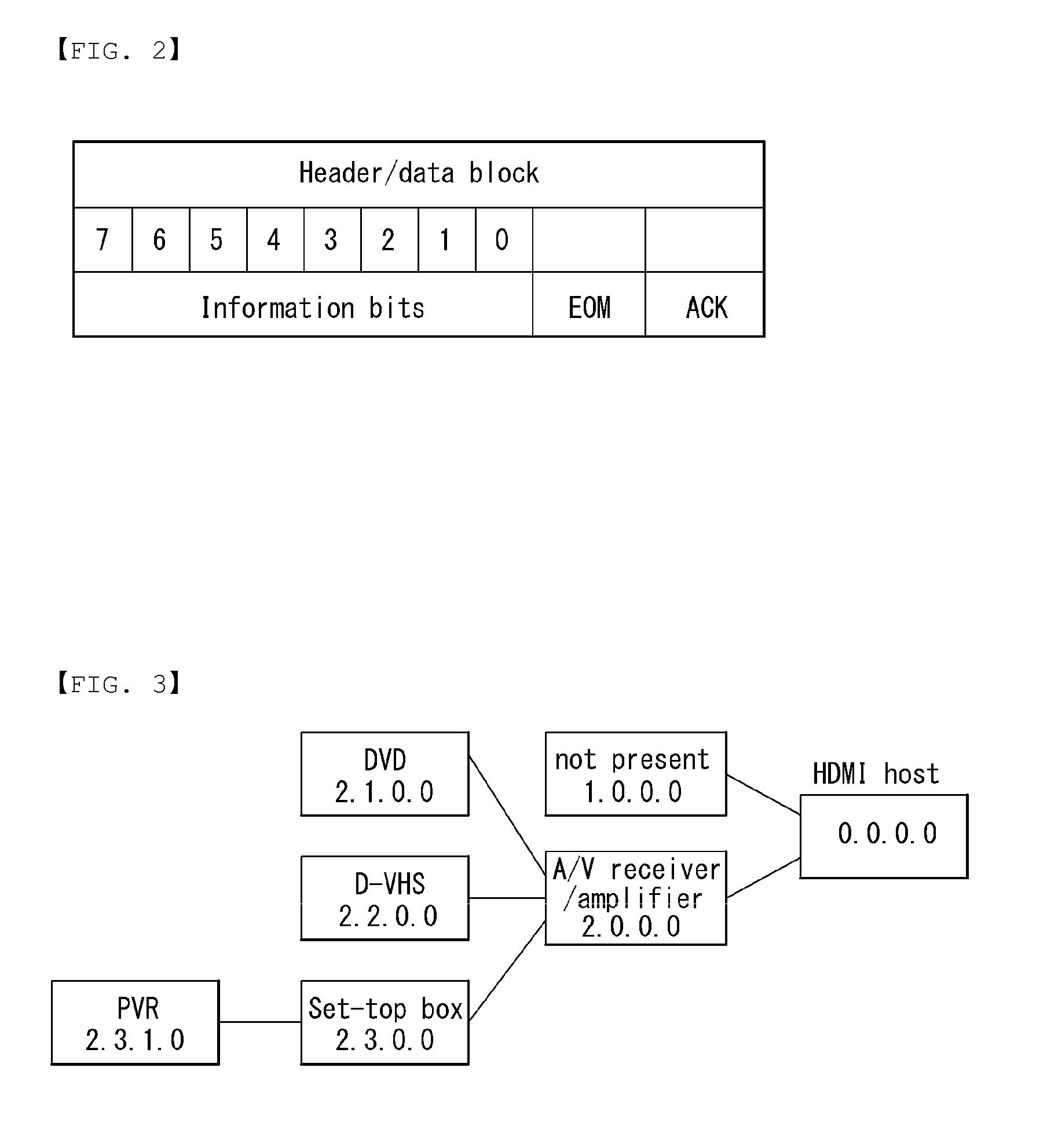

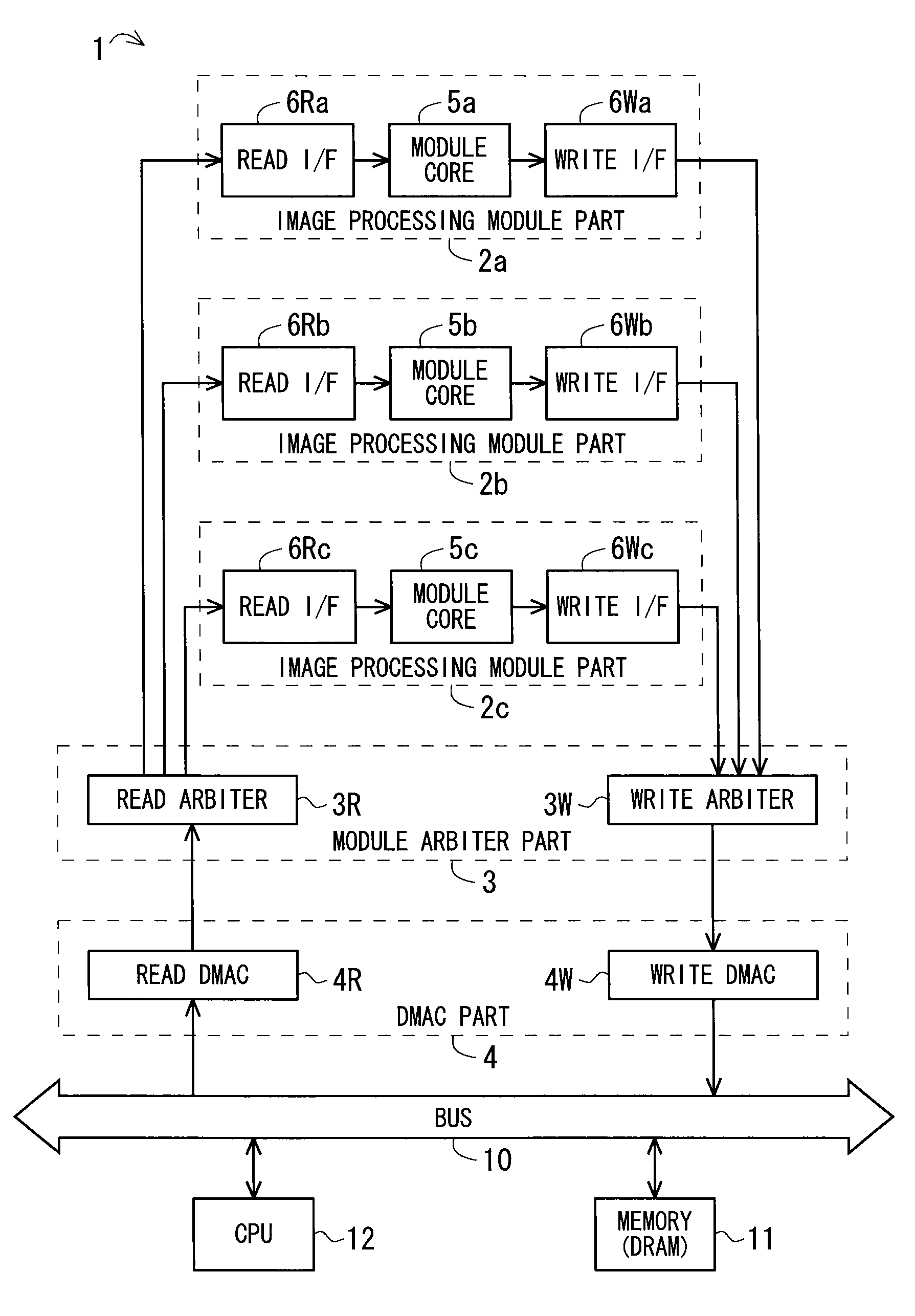

System for improving HDMI cec performance, and method for controlling same

InactiveUS20150134860A1Reduce unnecessary useImprove bus efficiencyCathode-ray tube indicatorsSelective content distributionComputer hardwareDevice type

The present invention provides a method for controlling a HDMI CEC device on HDMI CEC network including a plurality of devices, the method comprising: receiving a message for requesting a physical address allocation of a new device when the new device is connected to the HDMI CEC network; allocating a physical address of the new device based on the received message; and allocating a plural logical addresses of the new device when the physical address of the new device is valid, the plural logical addresses corresponding to the plural device types of the new device, wherein at least one of the plural logical addresses is set by using a flag bit.

Owner:LG ELECTRONICS INC

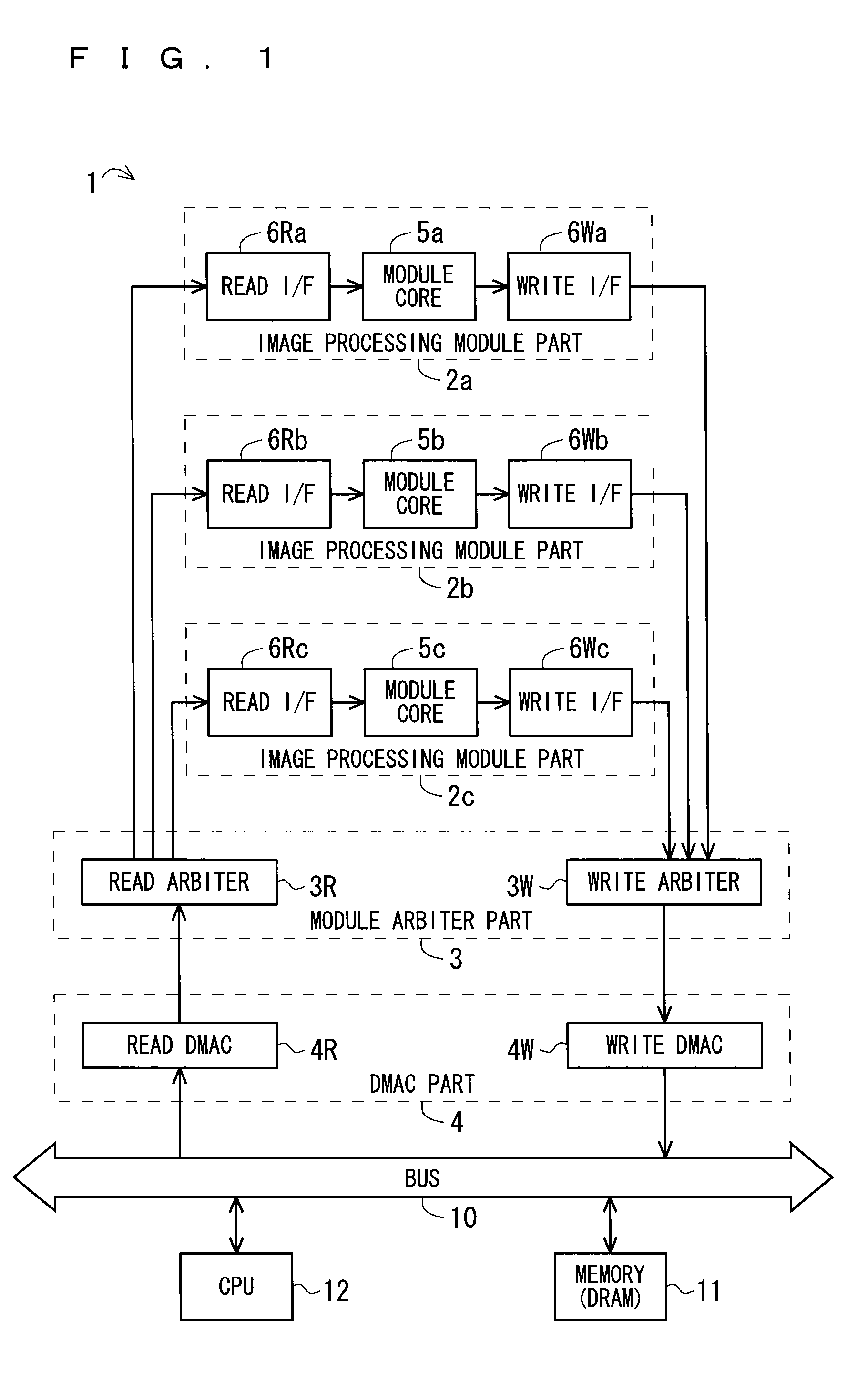

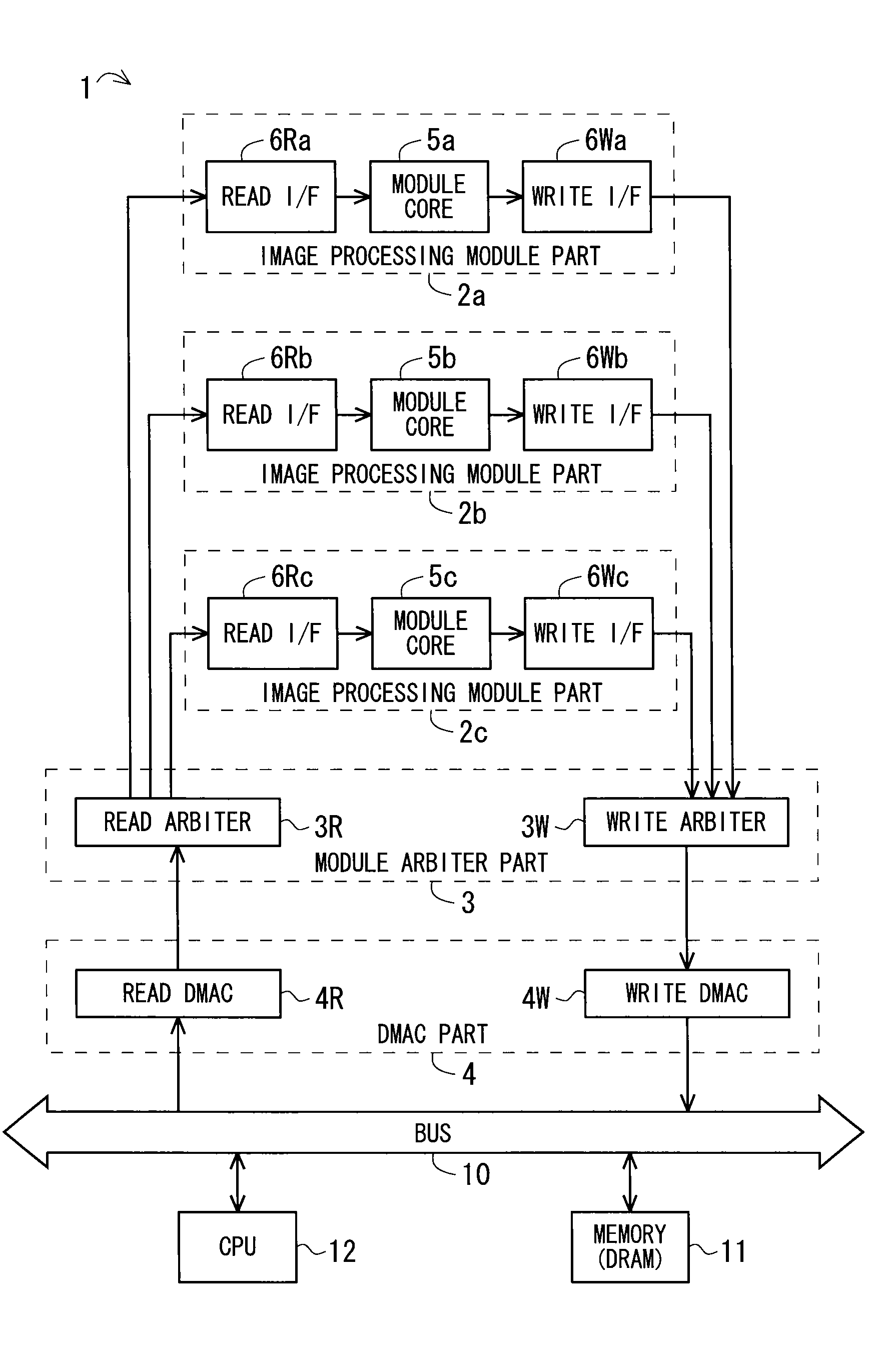

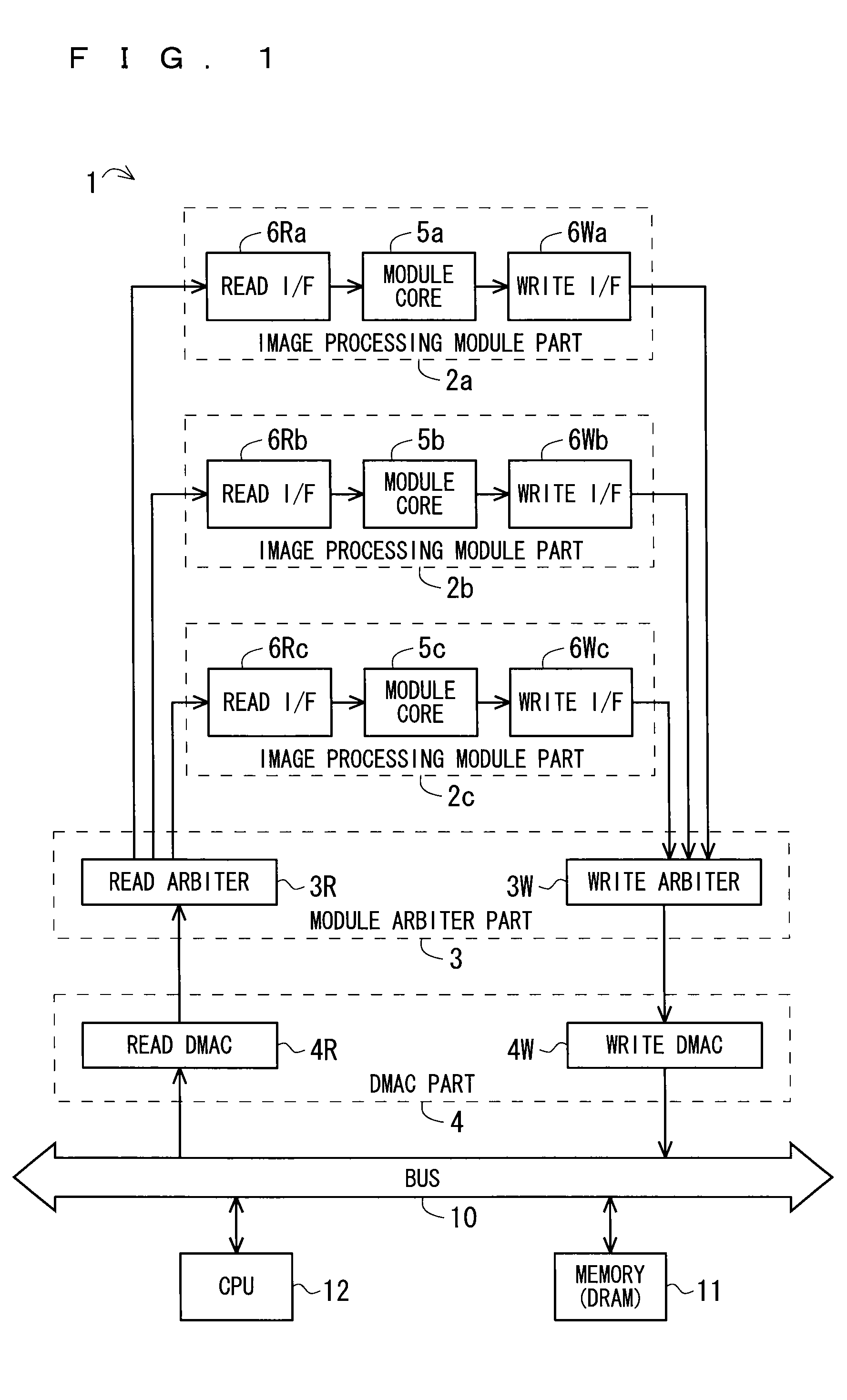

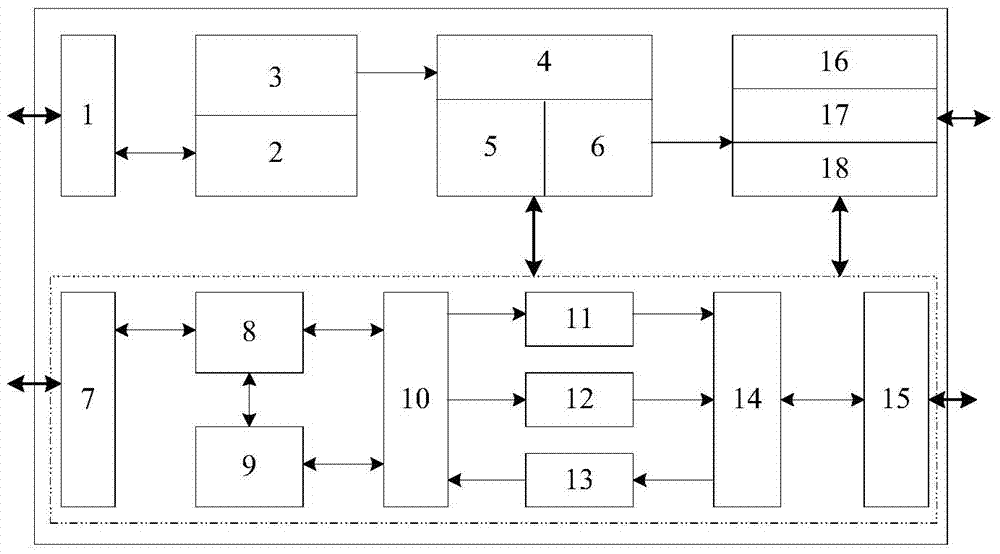

Image processing apparatus and image processing interface circuit

ActiveUS20140043343A1Improve bus efficiencyImage memory managementMultiple digital computer combinationsDirect memory accessImaging processing

An image processing apparatus includes a plurality of image processing module parts, a module arbiter part, and a DMAC (Direct Memory Access Controller) part. Each of the image processing module parts includes a module core for executing a predetermined image processing. The plurality of image processing module parts is connected to the module arbiter part. The module arbiter part arbitrates memory access which is given by the plurality of image processing module parts through a bus. The DMAC part is connected between the module arbiter part and the bus, and executes memory access related to the arbitration result obtained by the module arbiter part.

Owner:MEGACHIPS +1

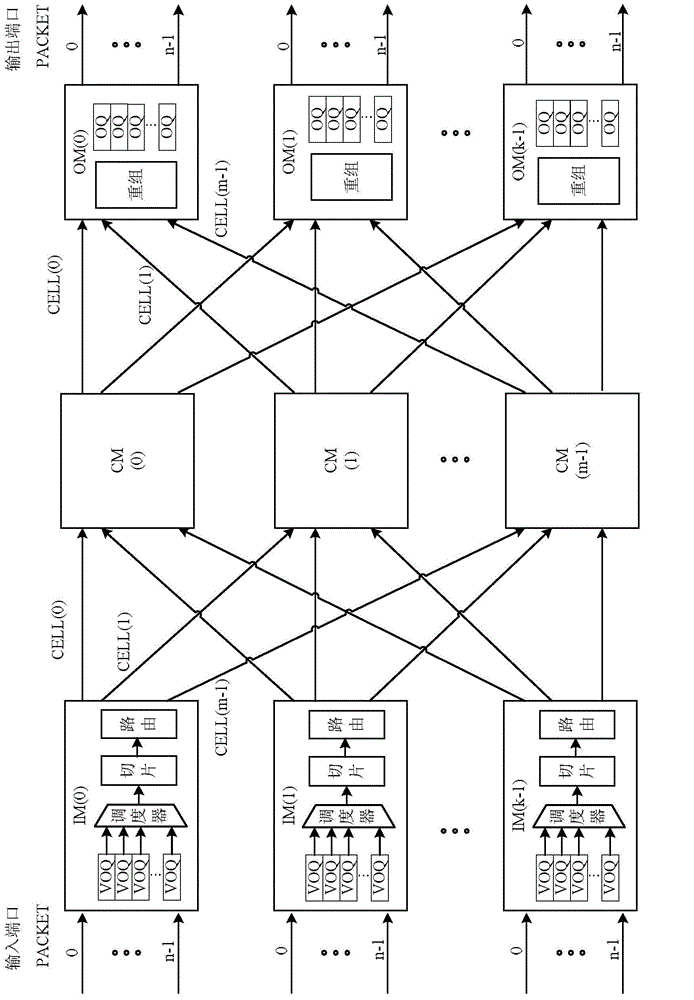

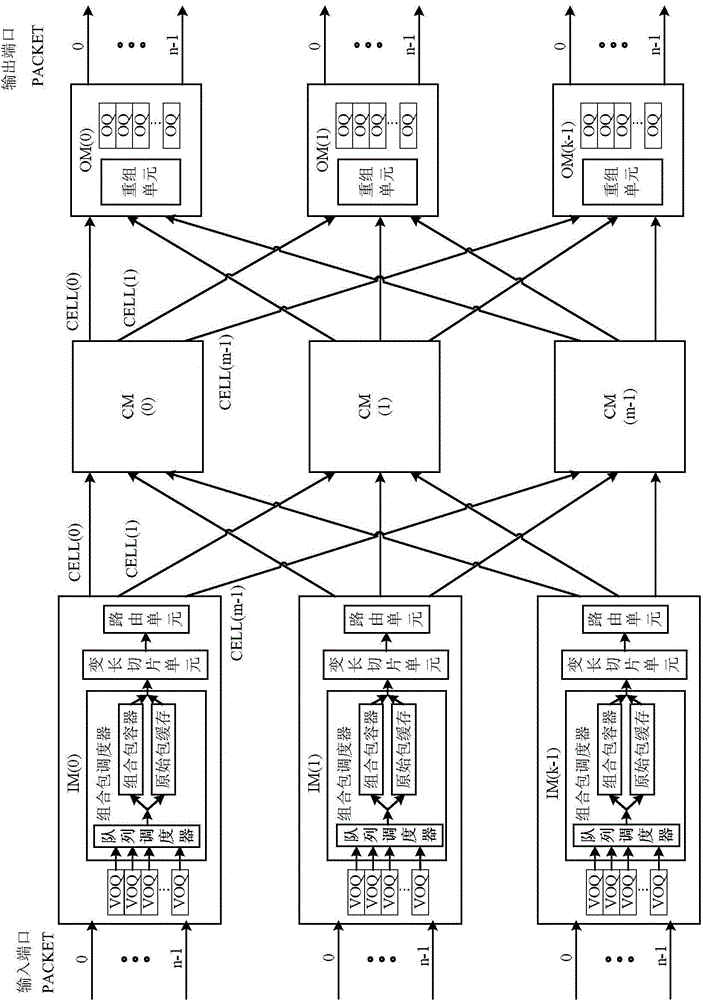

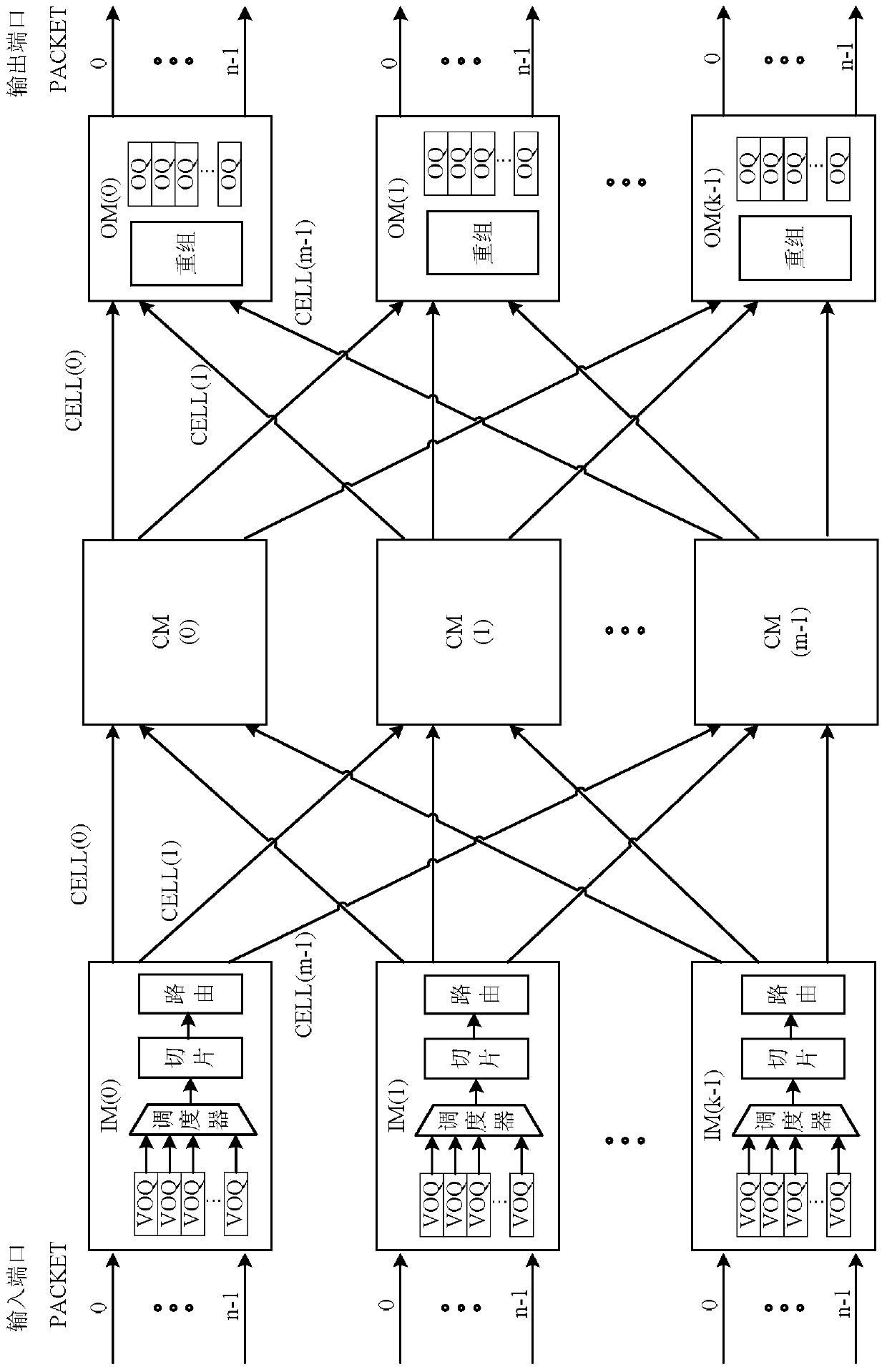

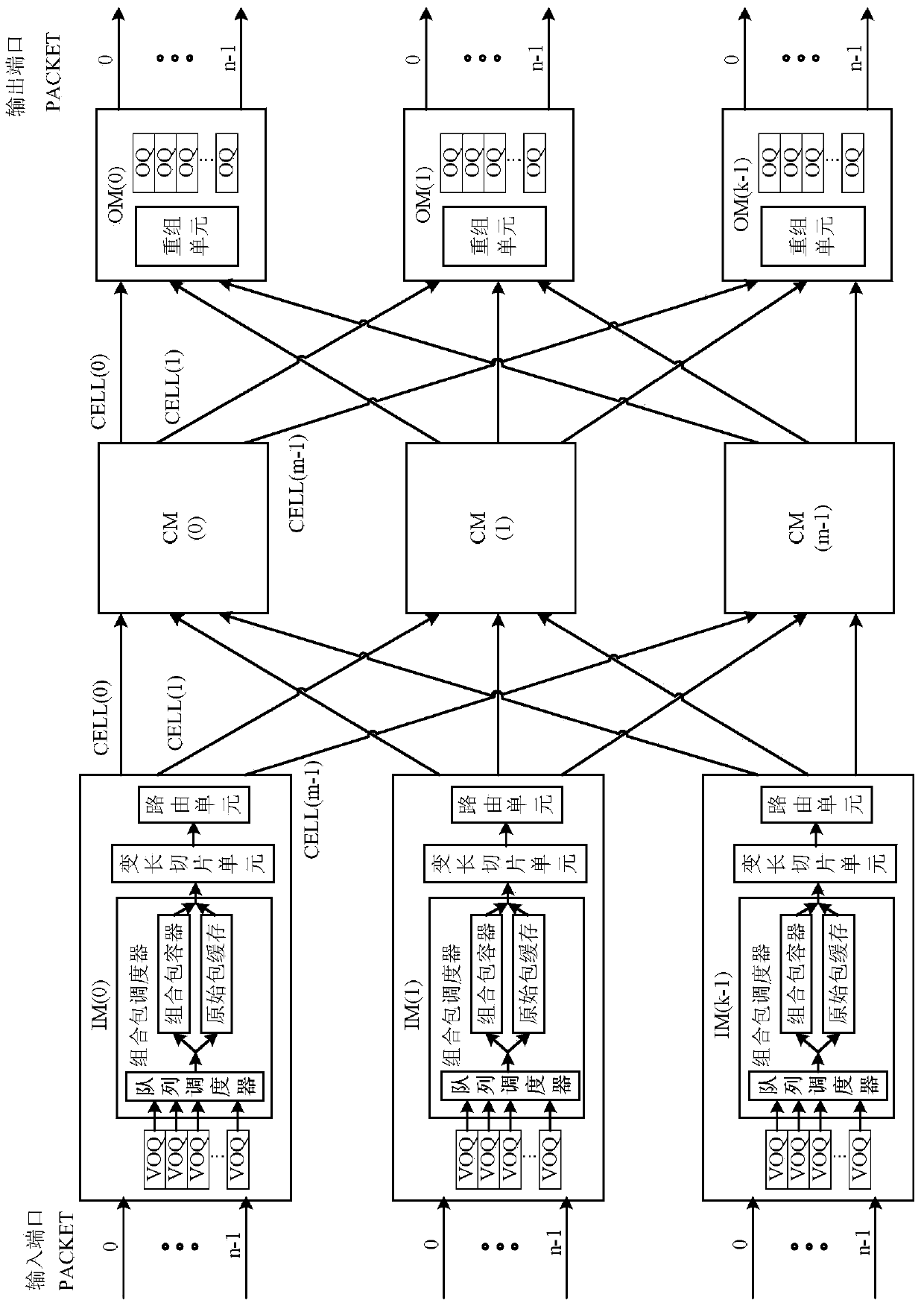

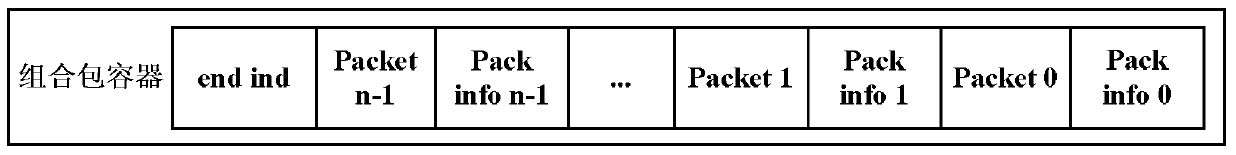

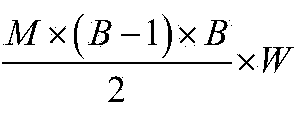

System and method for segmenting and regrouping data packets on basis of CLOS (Chinese library of science) switch network

ActiveCN104954292AImprove bus efficiencyImprove throughputData switching networksComputer scienceThroughput

The invention discloses a system and a method for segmenting and regrouping data packets on the basis of a CLOS (Chinese library of science) switch network, and relates to the technical field of communication. The CLOS switch network comprises a plurality of input modules IM, a plurality of central modules CM and a plurality of output modules OM. Each central module CM is connected with each input module IM and each output module OM; each input module IM comprises a combined packet scheduler, a variable-length slicing unit and a routing unit; each output module OM comprises a regrouping unit. The system and the method have the advantages that the efficiency of buses can be improved, the throughput can be obviously enhanced for short packets and packets with special lengths under the conditions of identical widths of the buses and identical work efficiency of the buses, and the performance of the system can be obviously enhanced.

Owner:FENGHUO COMM SCI & TECH CO LTD +1

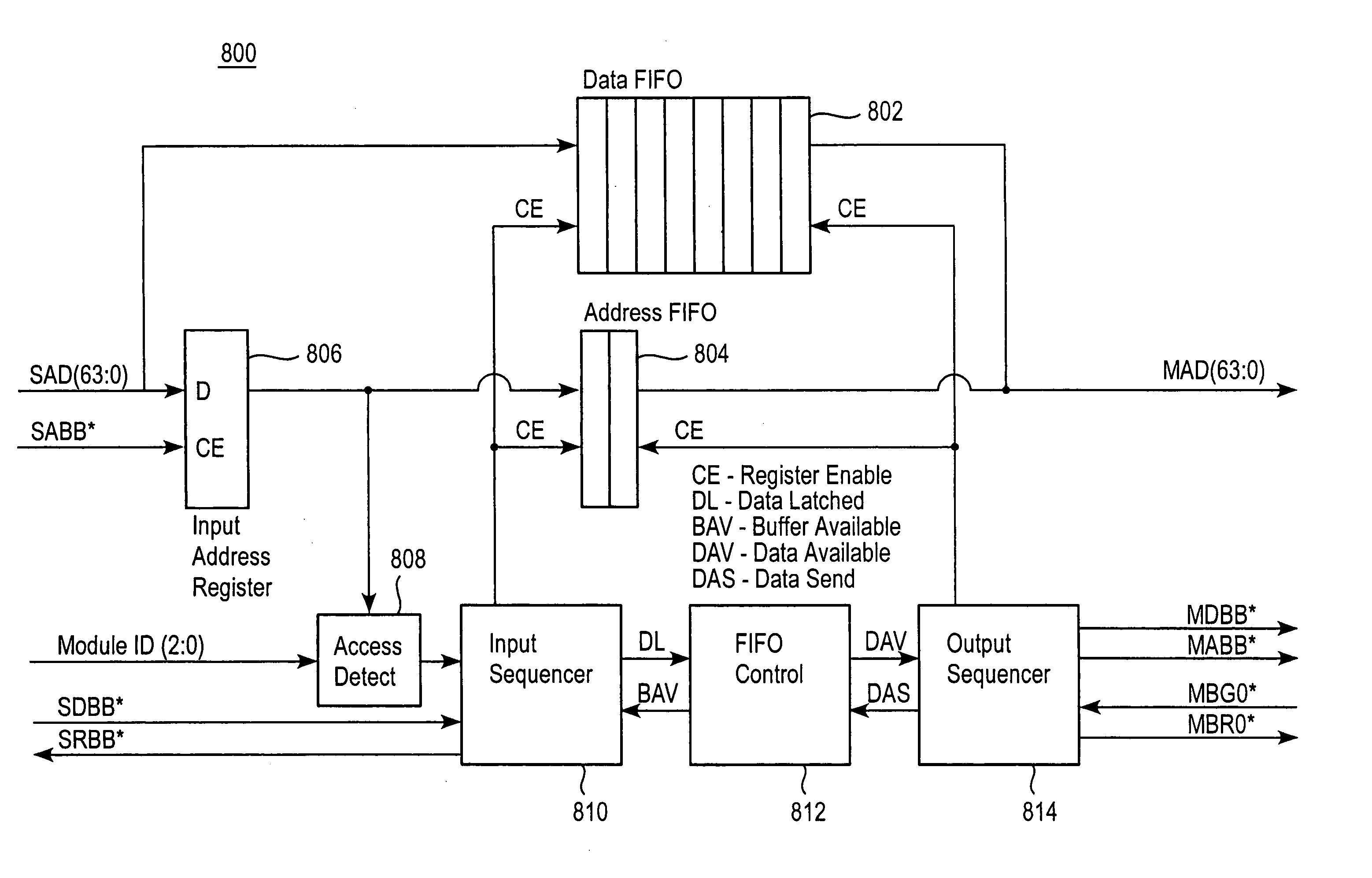

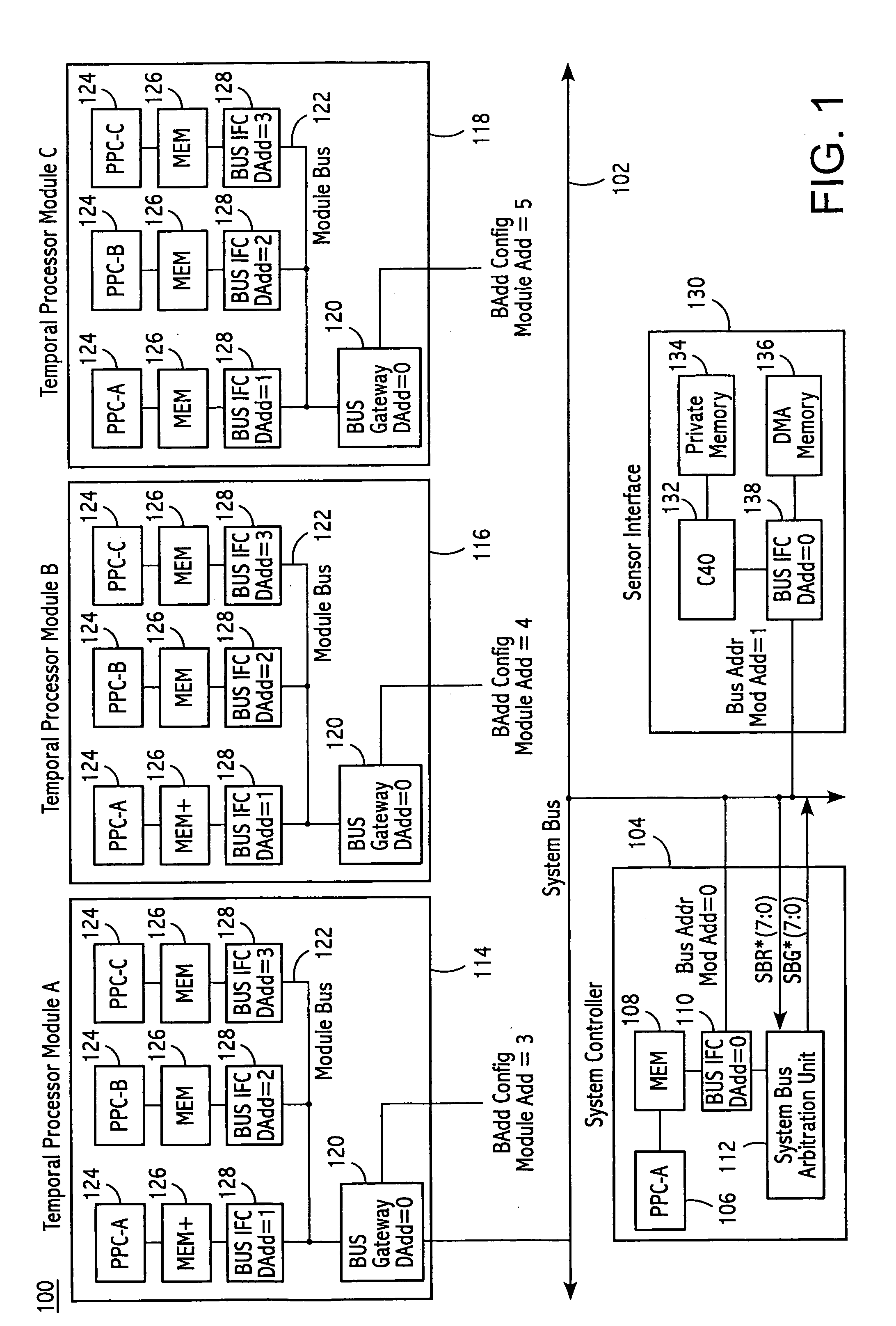

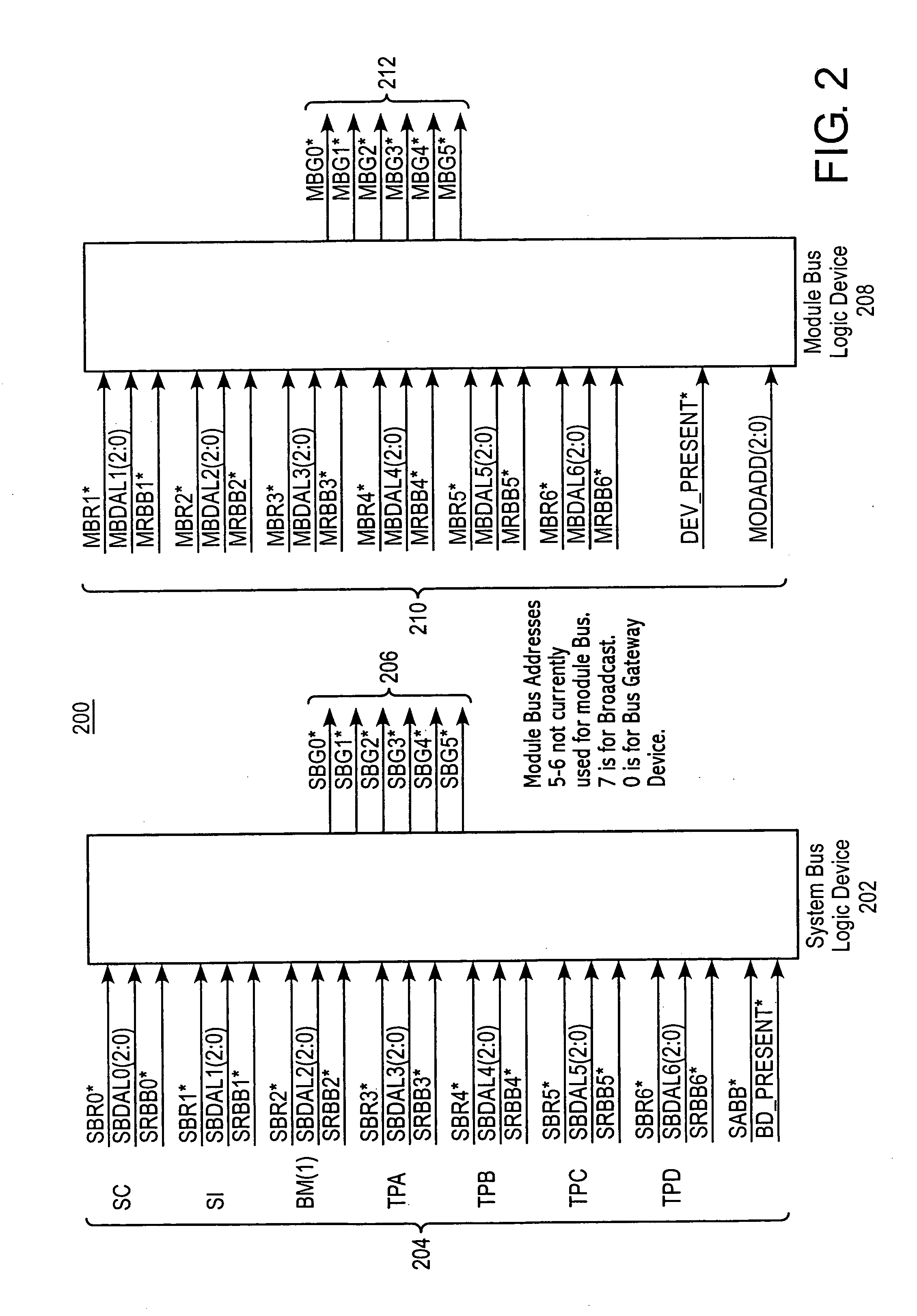

Two level multi-tier system bus

InactiveUS7191271B2Implemented in small amountImprove bus efficiencyGenerating/distributing signalsMemory systemsExecution controlSystem controller

The present invention is directed to a method and apparatus utilizing a two-level, multi-tier system bus. The multi-tier system bus of the present invention allows for the flow of information to be managed among plural processors by connecting processors within modules on a local bus, which is then connected to the system bus by way of a gateway. A system controller and arbitrator is provided for arbitrating access to the system bus by the various modules. The present invention, by way of the system controller initiates and performs control actions and allows the system bus to be freed from transmission delays of prior approaches associated with transmitting data packets. The present invention accomplishes this by establishing a clear path segment between various modules or devices contained on the system bus, and processors contained within modules located on local buses such that delays associated with transmission of such data packets is greatly reduced, and processing speeds and rates are greatly increased. The present invention also avoids the complications of software arbitration, as all of the arbitration of the present invention is accomplished by hardware.

Owner:LOCKHEED MARTIN CORP

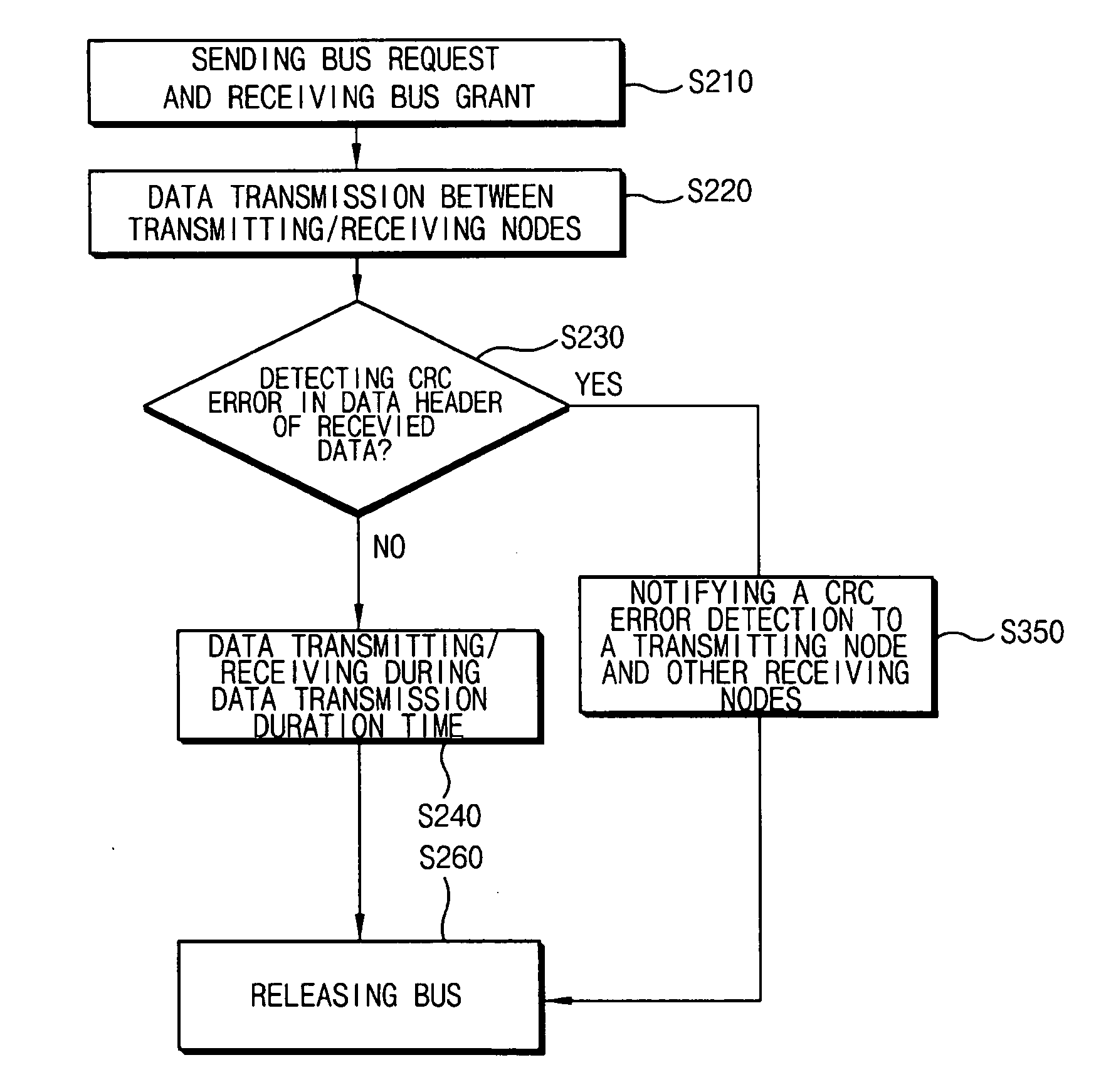

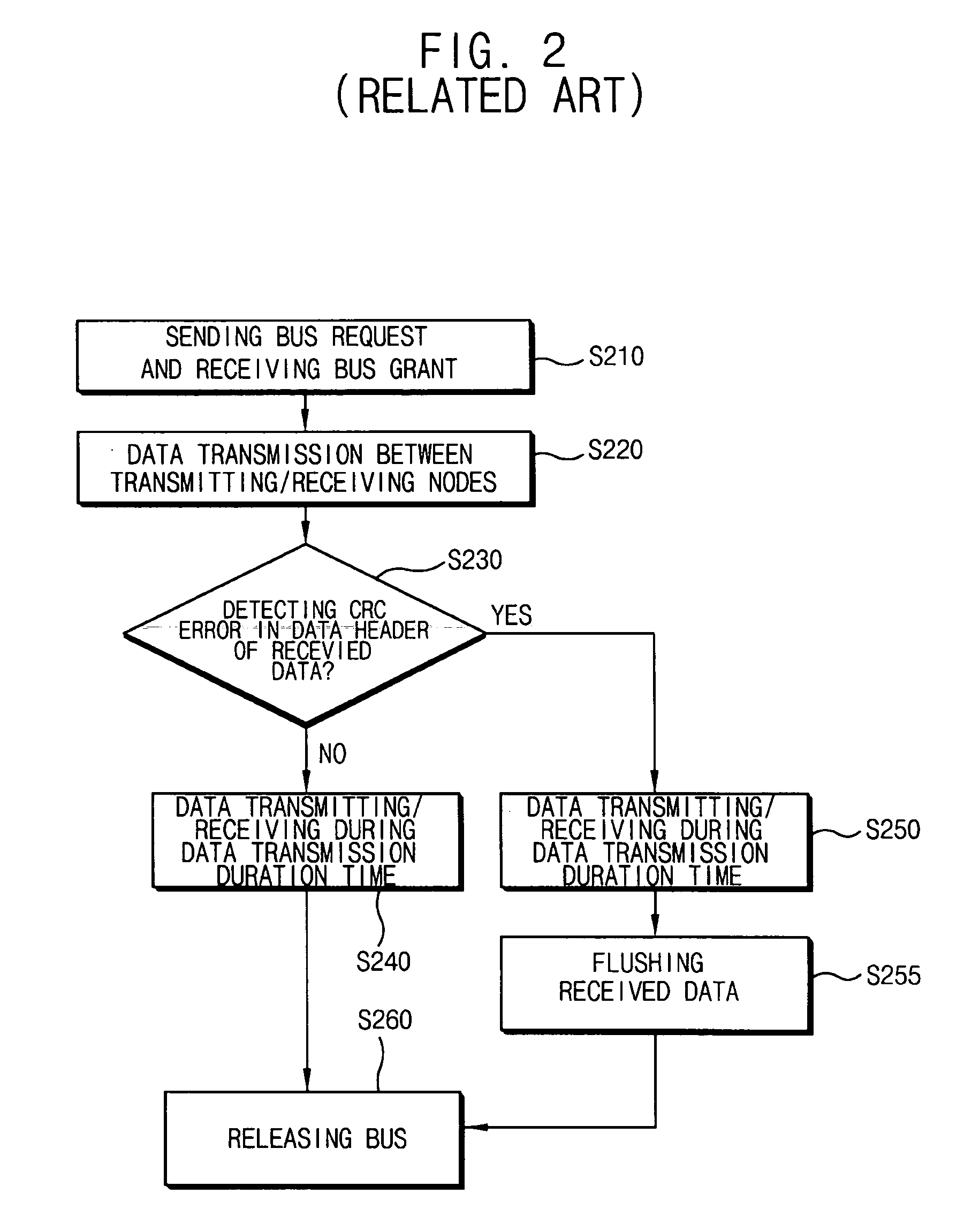

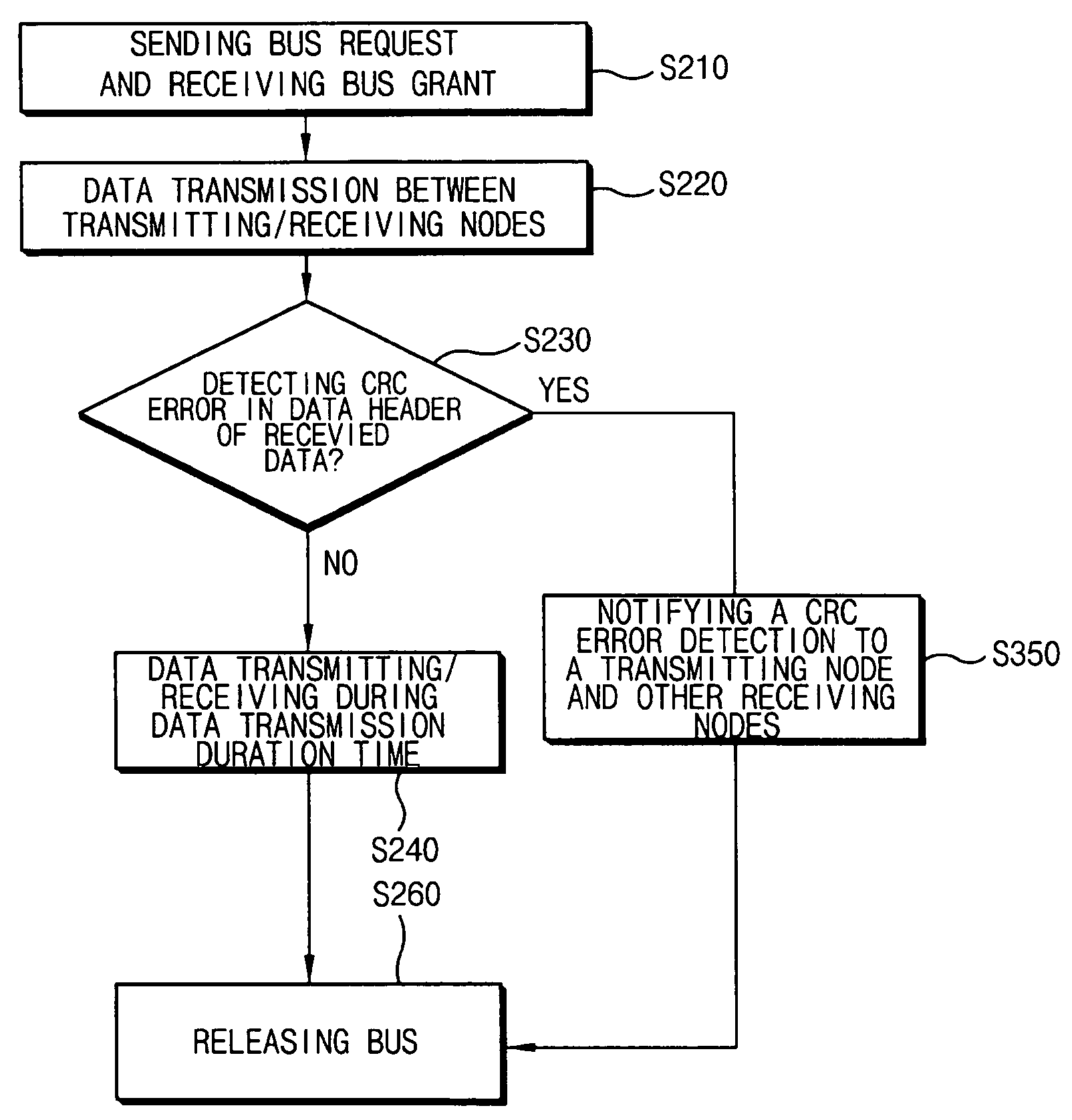

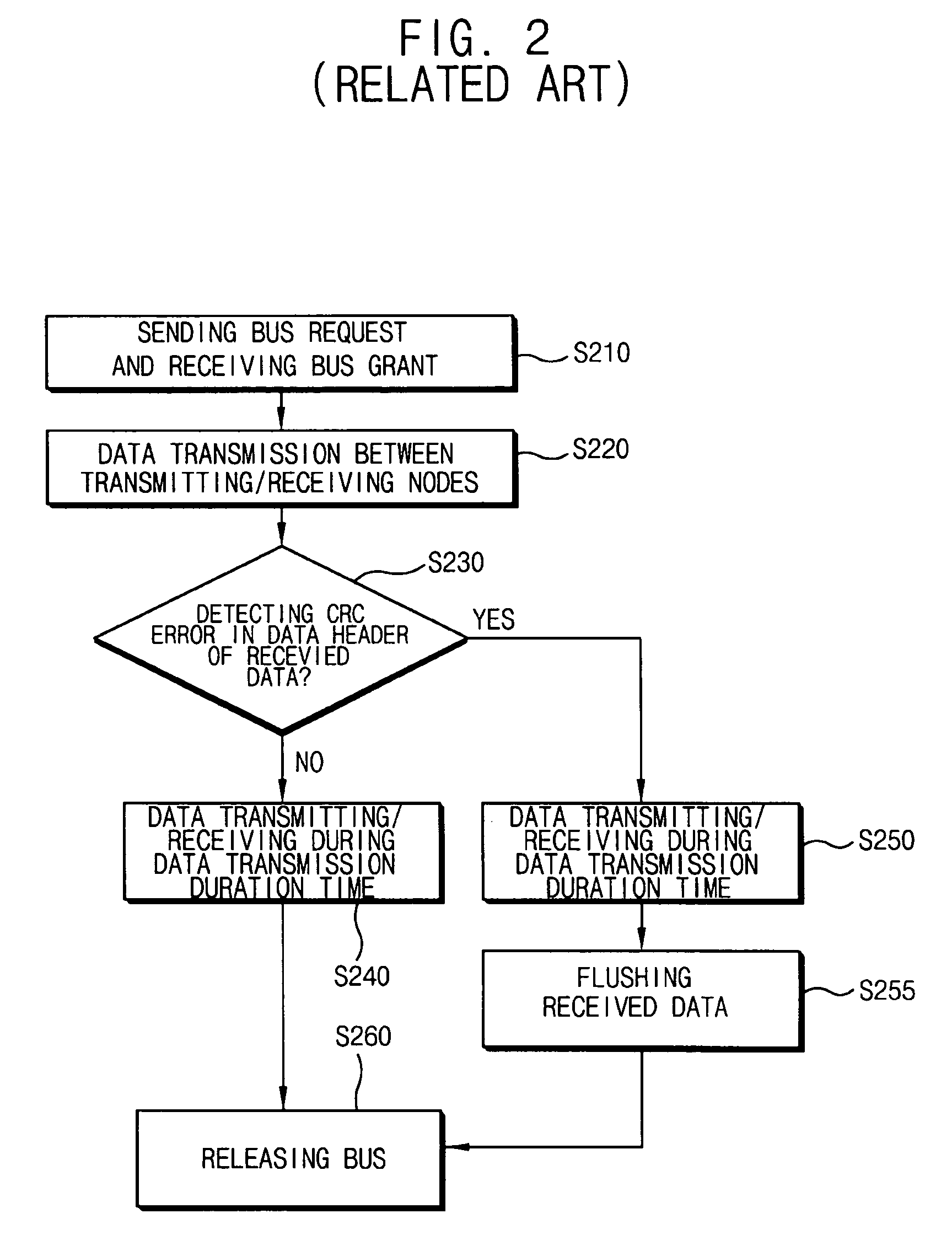

Bus systems, apparatuses, and methods of operating a bus

InactiveUS20060007853A1Solve the slow data transmission speedImprove bus efficiencyError prevention/detection by using return channelFrequency-division multiplex detailsError checkData transmission

Data transmission between transmitting / receiving nodes in a bus system may be controlled based on an error check of received data. When an error in the received data is detected, the transmitting node may cease data transmission, and other nodes, which may not have detected the error, may be notified of the detected error.

Owner:SAMSUNG ELECTRONICS CO LTD

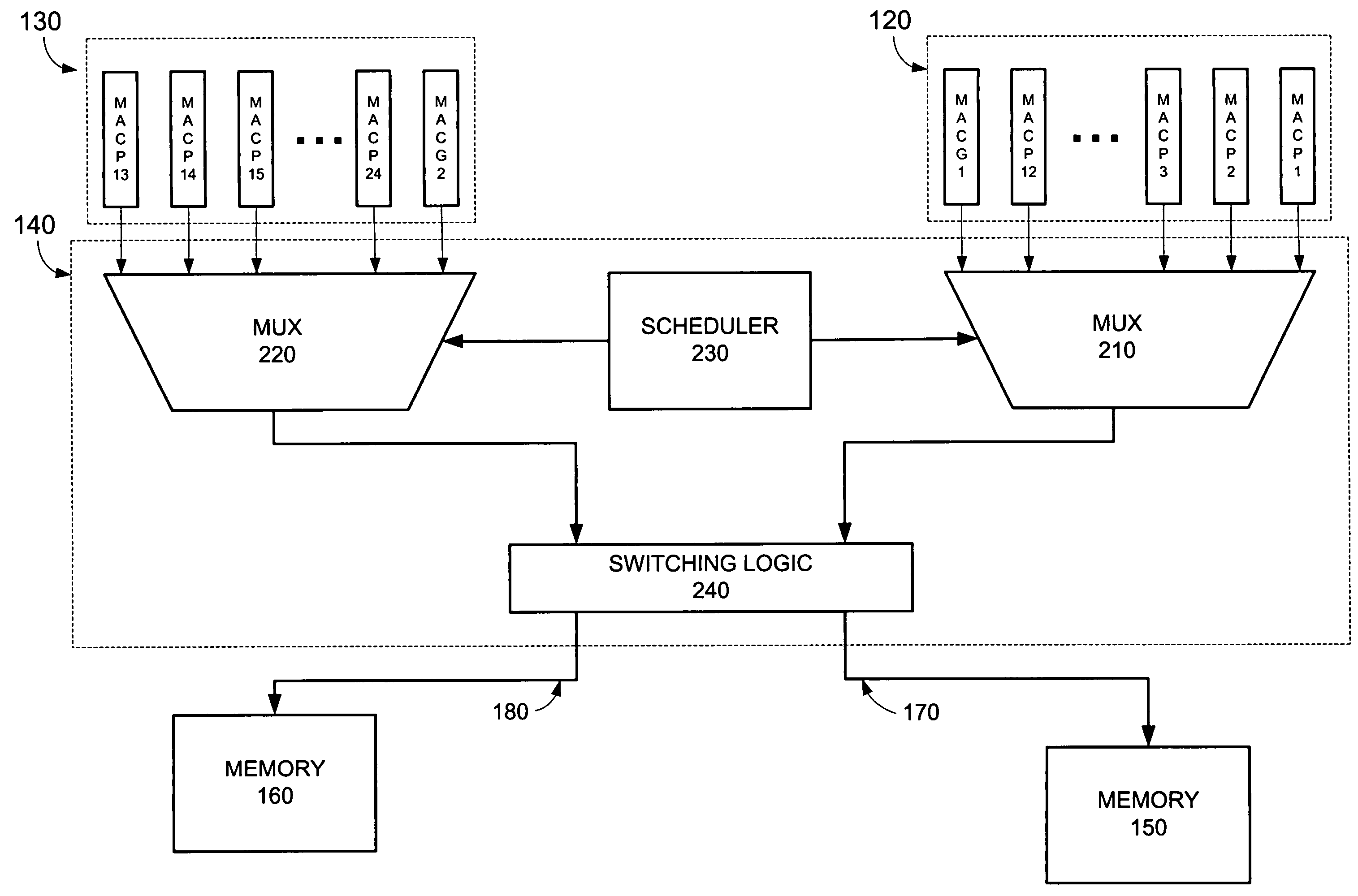

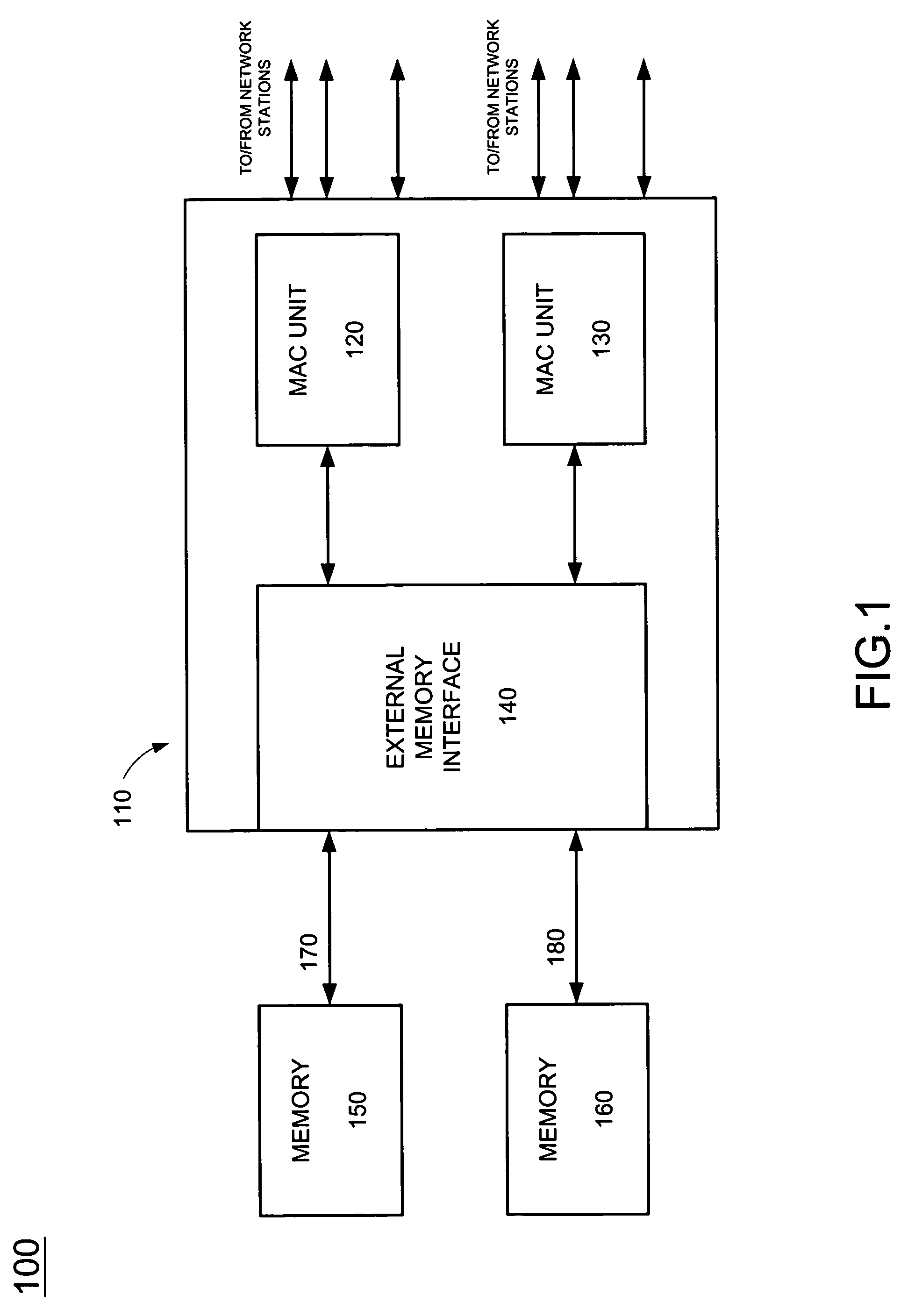

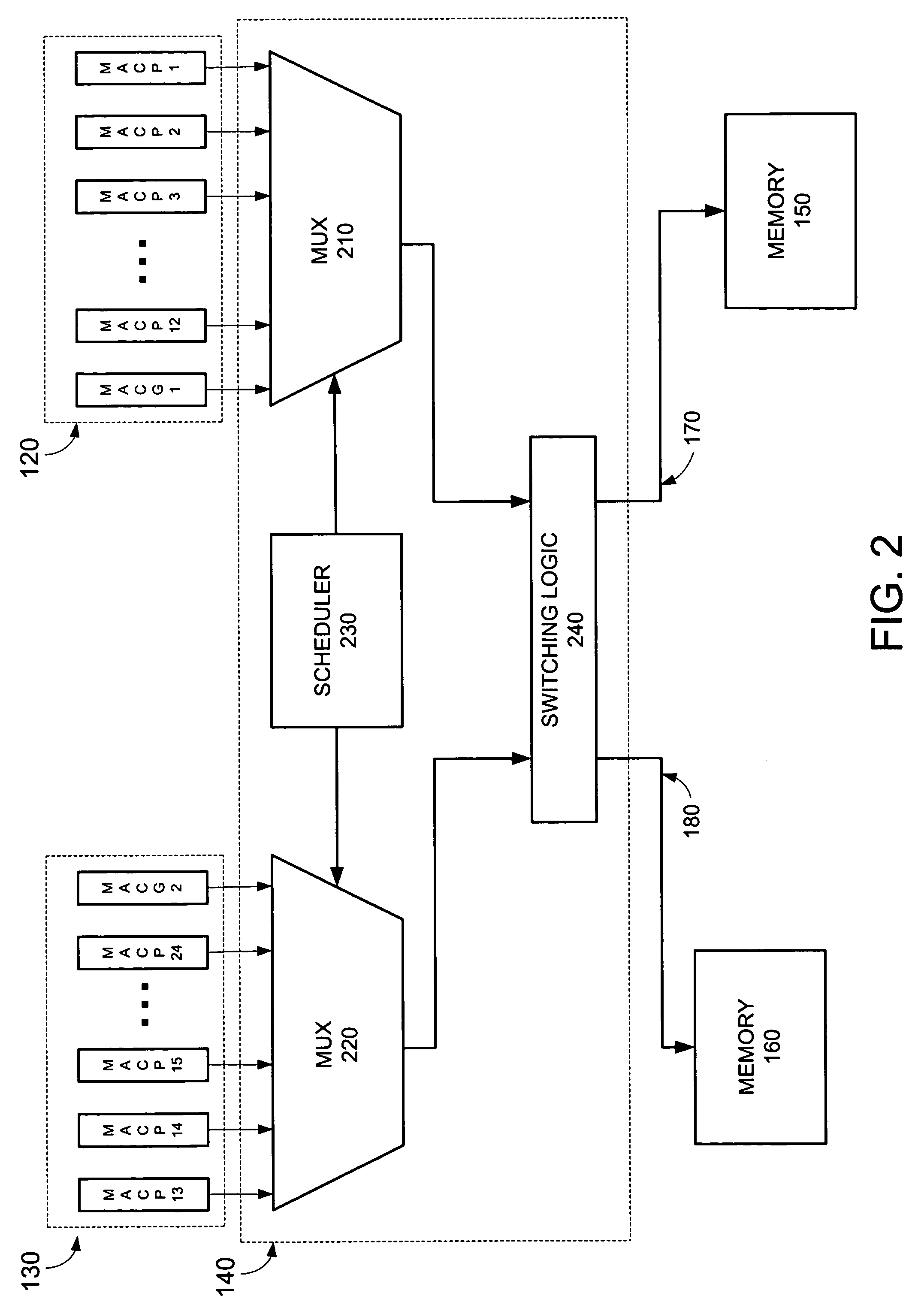

Method and apparatus for accessing external memories

ActiveUS7143185B1Increase efficiencyHigh data throughputMemory adressing/allocation/relocationMultiple digital computer combinationsExternal memory interfaceNetwork switch

A network switch that controls the communication of data frames between stations includes receive devices that correspond to ports on the network switch. The receive devices receive and store data frame information from the network stations. The network switch also includes an external memory interface that receives the data frame information from the receive devices and transfers the data frame information to multiple external memory devices.

Owner:ADVANCED MICRO DEVICES INC

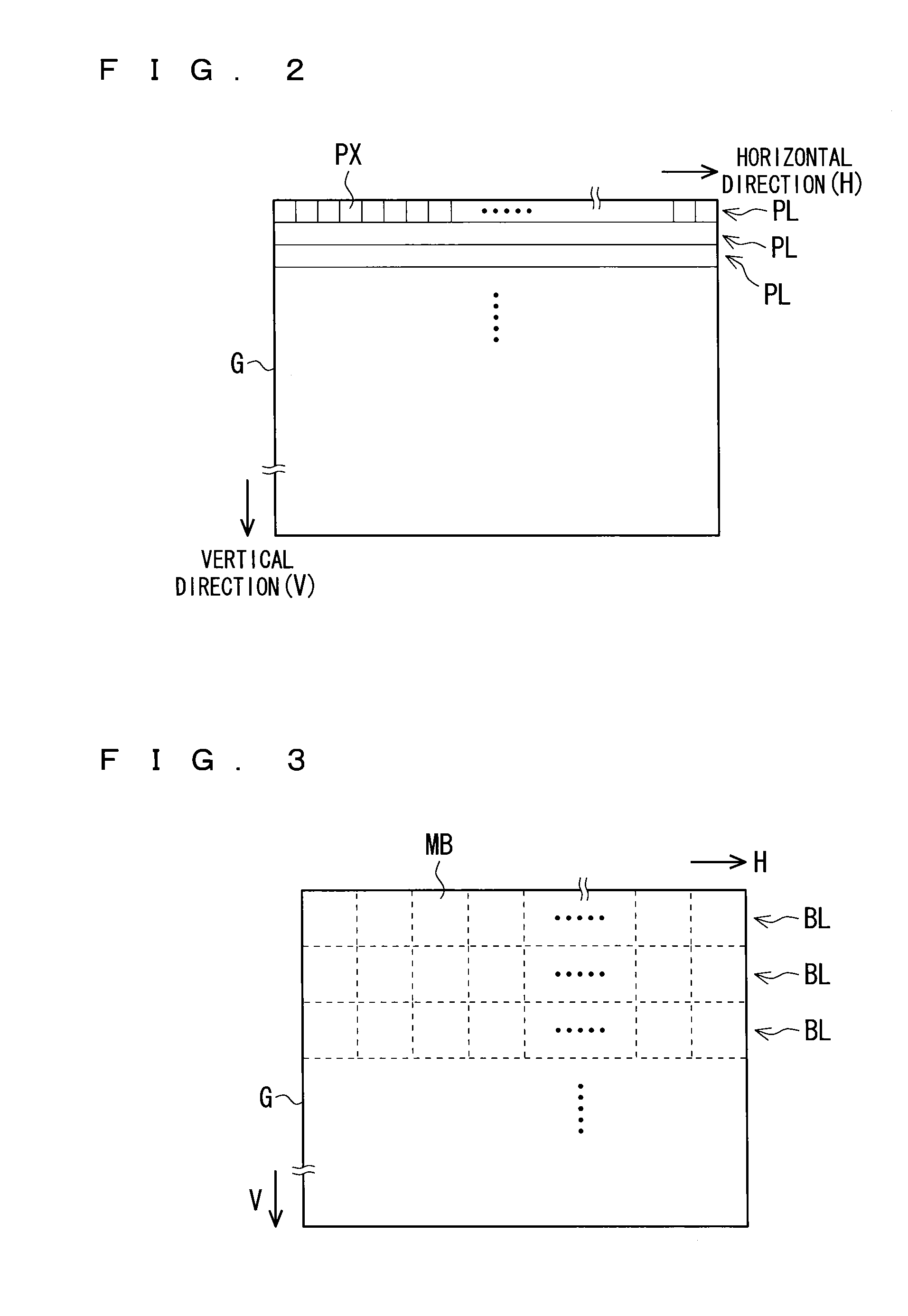

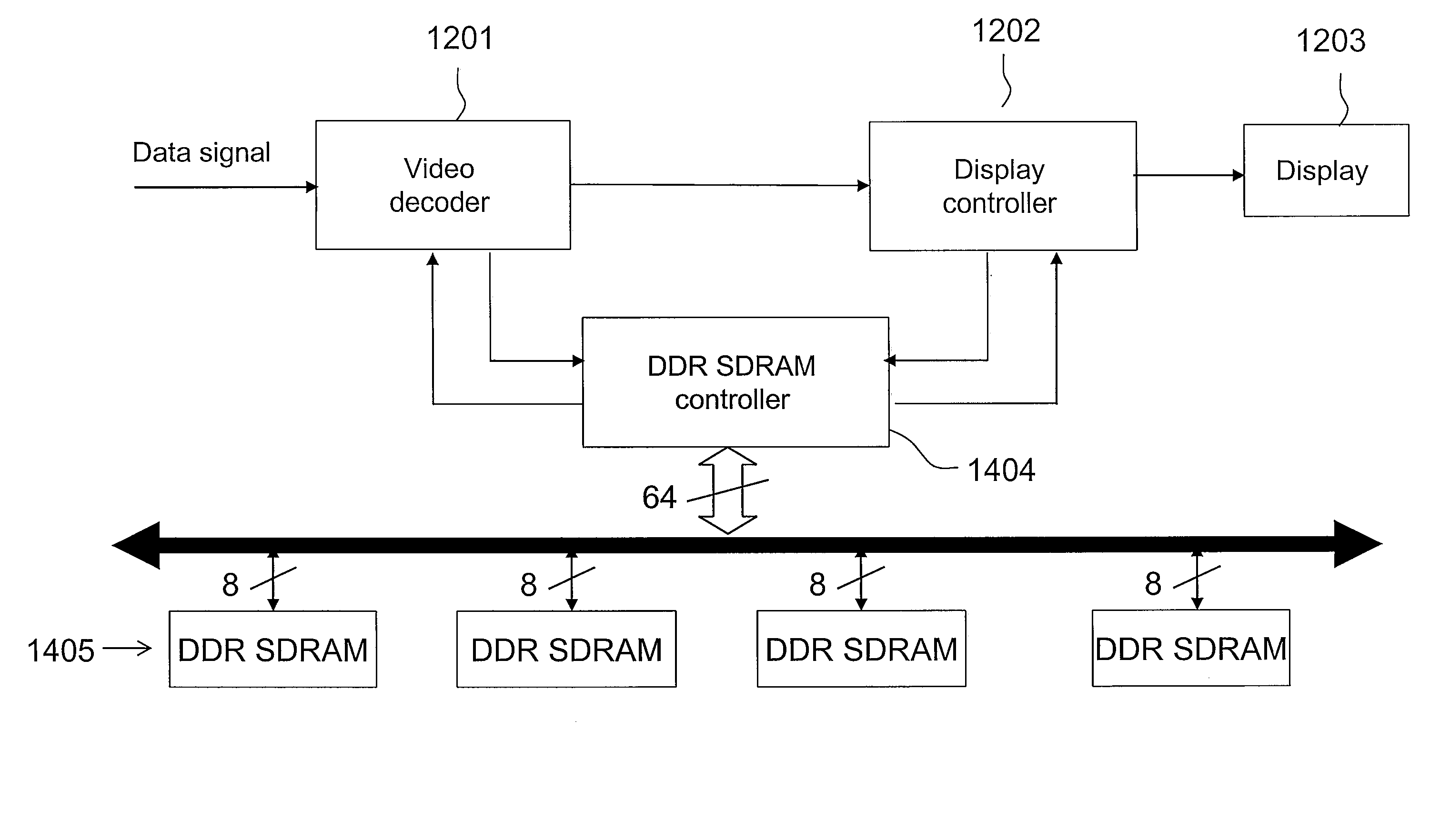

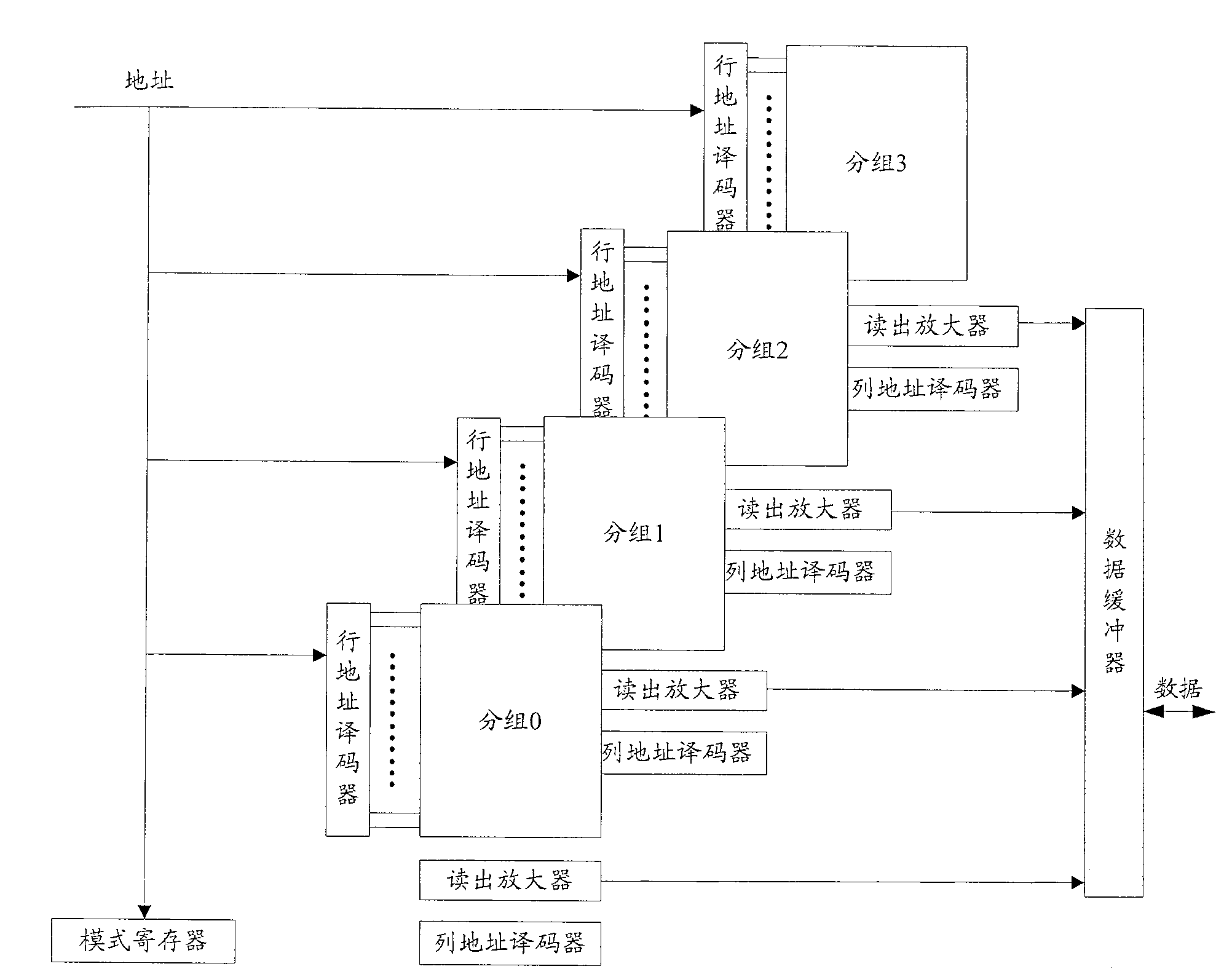

Method for mapping memory addresses, memory accessing apparatus and method thereof

ActiveUS20080089426A1Improve bus efficiencyImprove access efficiencyPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningMemory addressParallel computing

A memory accessing apparatus and a method thereof are provided, which are suitable for methods and apparatuses that access memory data in blocks, such as a video decoder. An advanced memory mapping method is adopted to generate the column address and row address of a data word in a memory based on the logic address of the data word in a video frame. Macroblocks are organized into clusters, macroblocks of the same cluster are stored in the same row of the memory, and the orders in which the video decoder reads and writes macroblocks are rearranged so as to reduce the number of row changes in memory access and improve the throughput of memory access. Furthermore, memory accesses between the video decoder and the display controller can be coordinated.

Owner:IND TECH RES INST

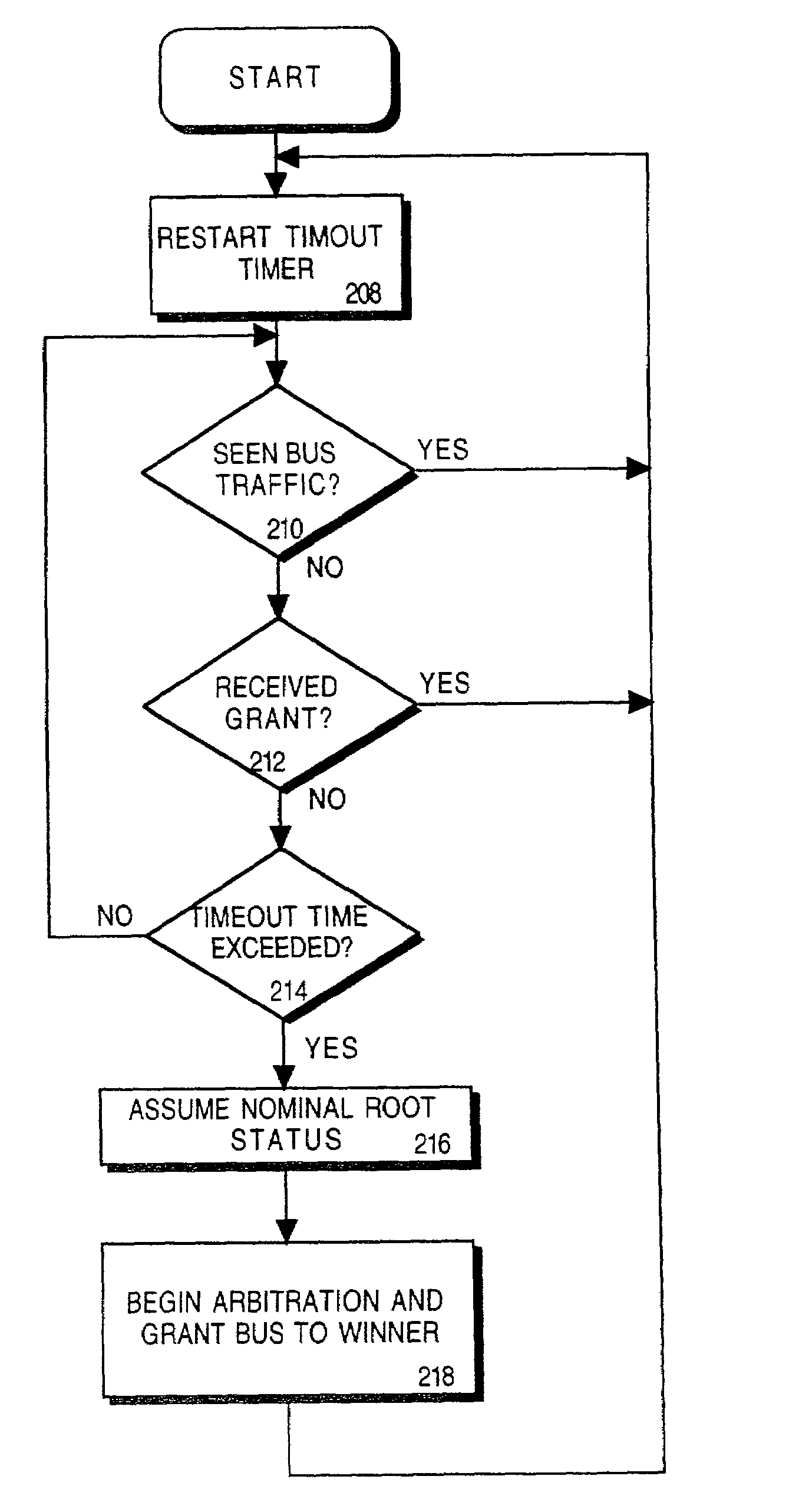

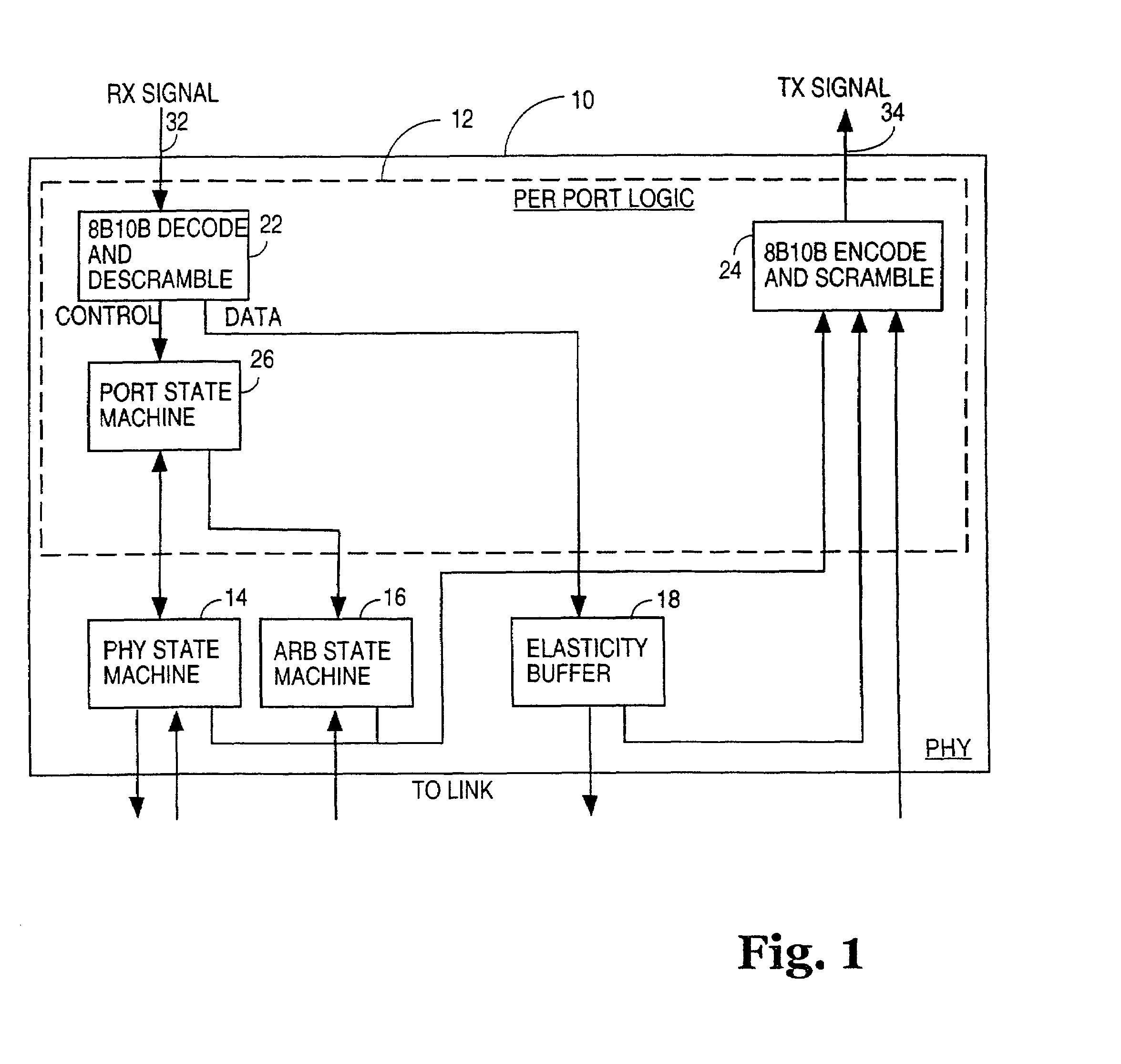

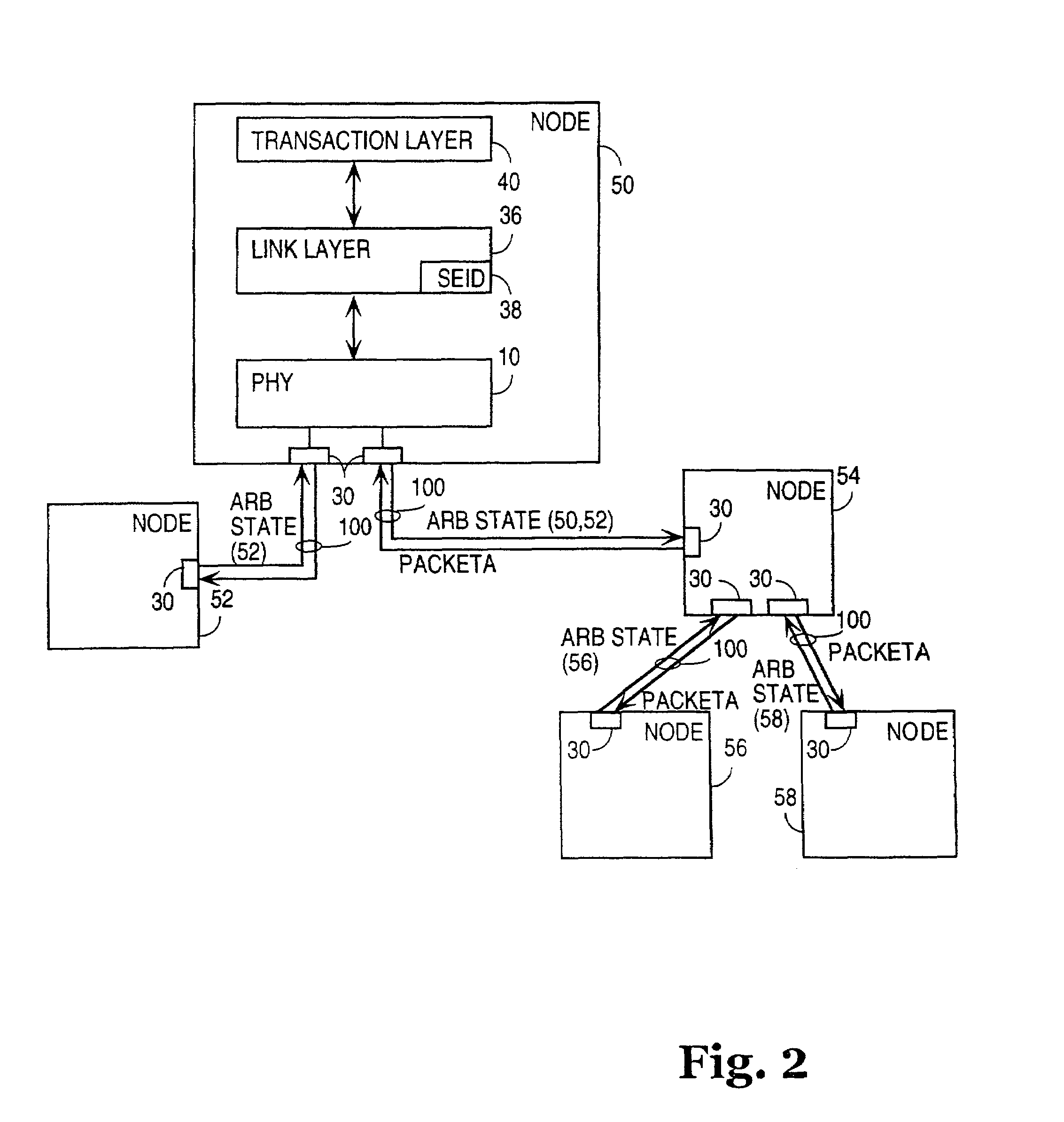

Distributed arbitration on a full duplex bus

Distributed arbitration in a full-duplex bus system. By distributing the arbitration function among the nodes of a tree topology full-duplex bus system such that arbitration at any particular time is handled by a node holding a grant of the bus at that time (the nominal root node), a reverse flow direction towards the nominal root node is available for arbitration flow. This allows the discrete arbitration phase to be eliminated and generally improves bus efficiency.

Owner:INTEL CORP

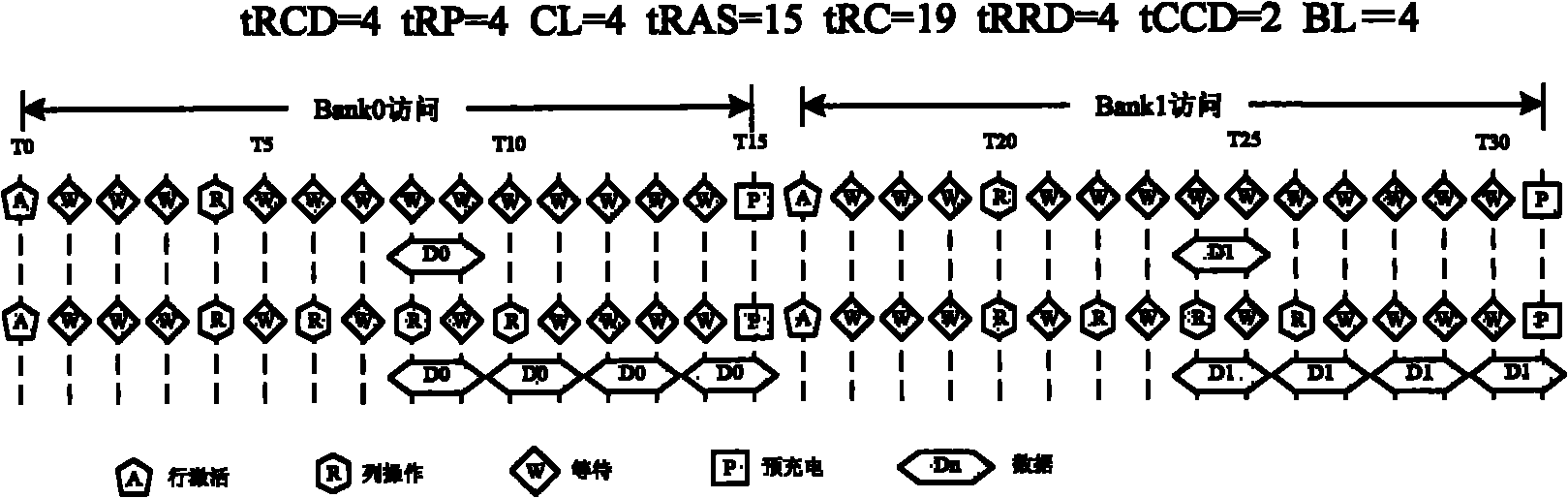

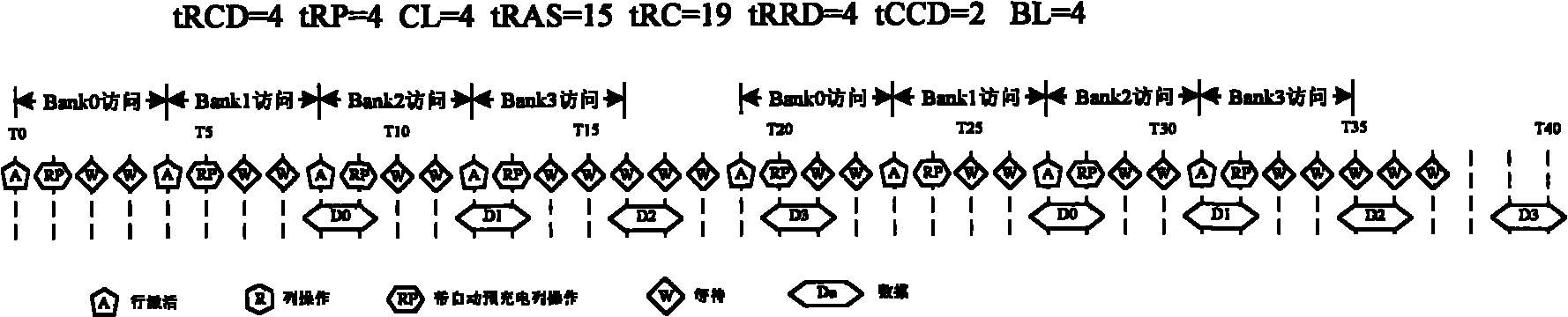

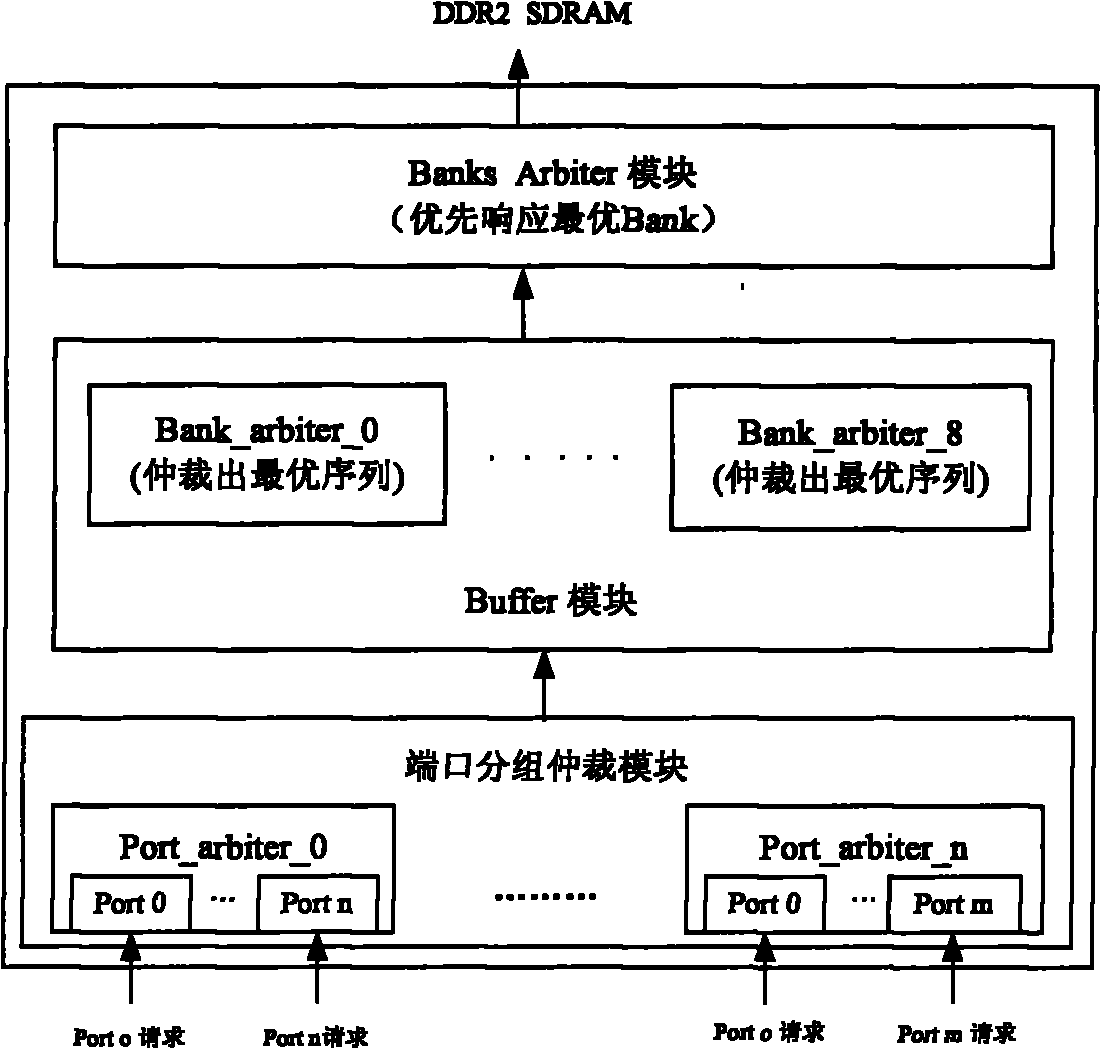

Access control method of synchronous dynamic memory

ActiveCN102033832ASave Bank Change TimeImprove bus efficiencyElectric digital data processingA-weightingOperation time

The invention provides a high-efficiency access control method of a synchronous dynamic memory. By using a Round robin scheduling algorithm improved by combining a port grouping arbitration mechanism, a Bank internal arbitration mechanism and a Bank intermediate arbitration mechanism, a high-efficiency disorder scheduling algorithm, a weighting system arbitration algorithm and other technical means to realize the high-efficiency access and save sequence, the invention not only retains the advantages of two universal operation sequences, but also avoids the defects of the two operation time sequences and overcomes the defect that an FIFO (First In First Out) cache request mechanism requires to be configured with greater FIFO. According to the method, the requirement for high-efficiency data interaction under various conditions can be met by using smaller cache space.

Owner:HANGZHOU NATCHIP SCI & TECH

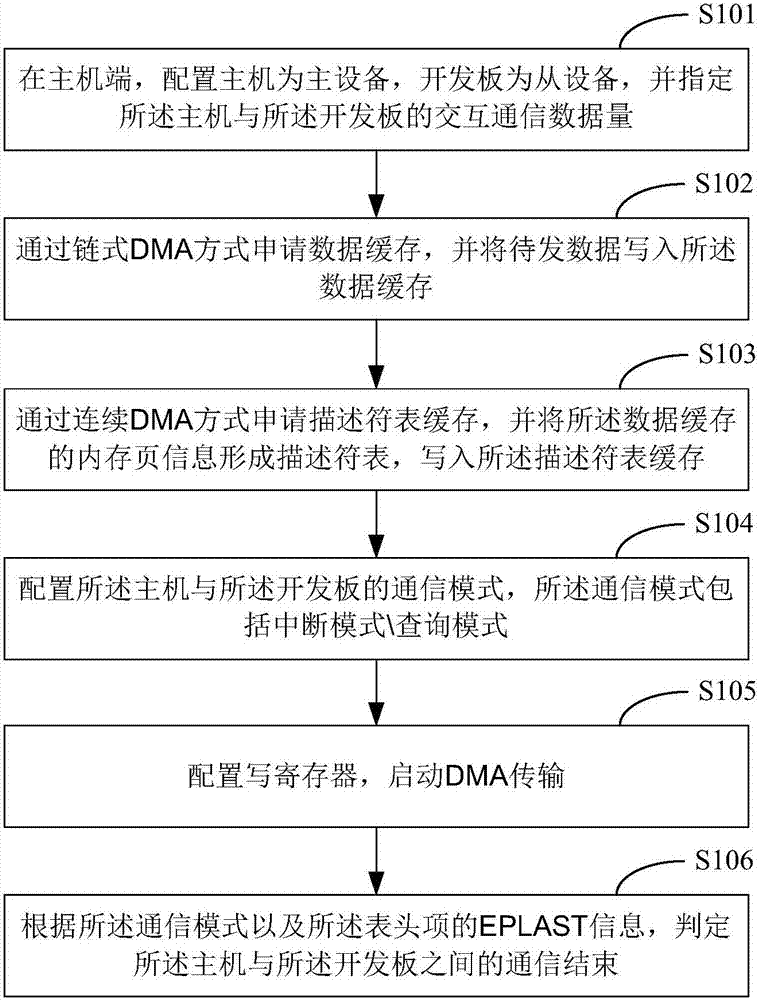

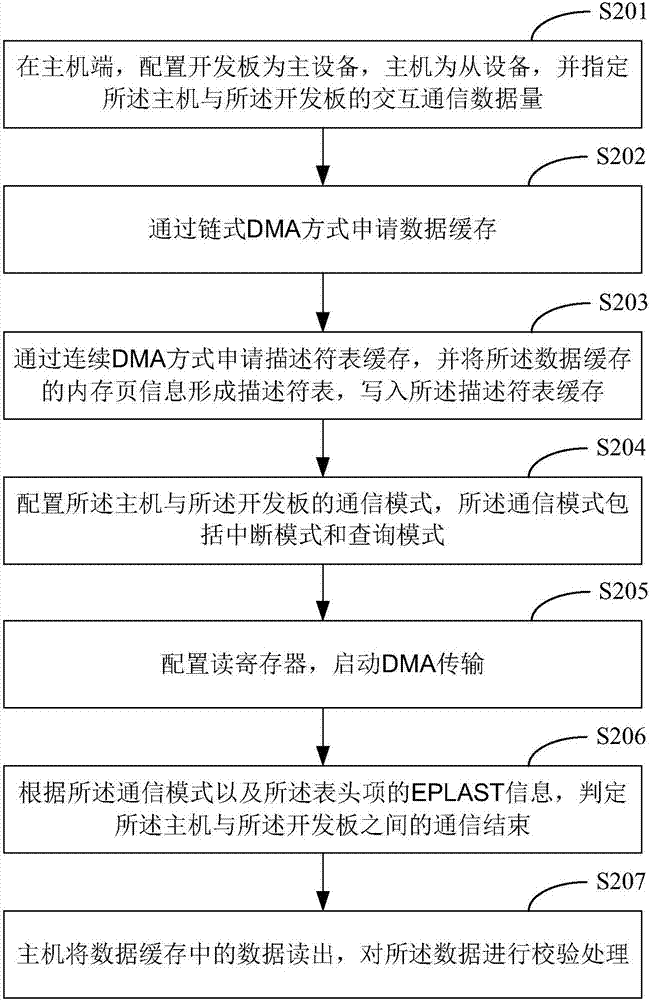

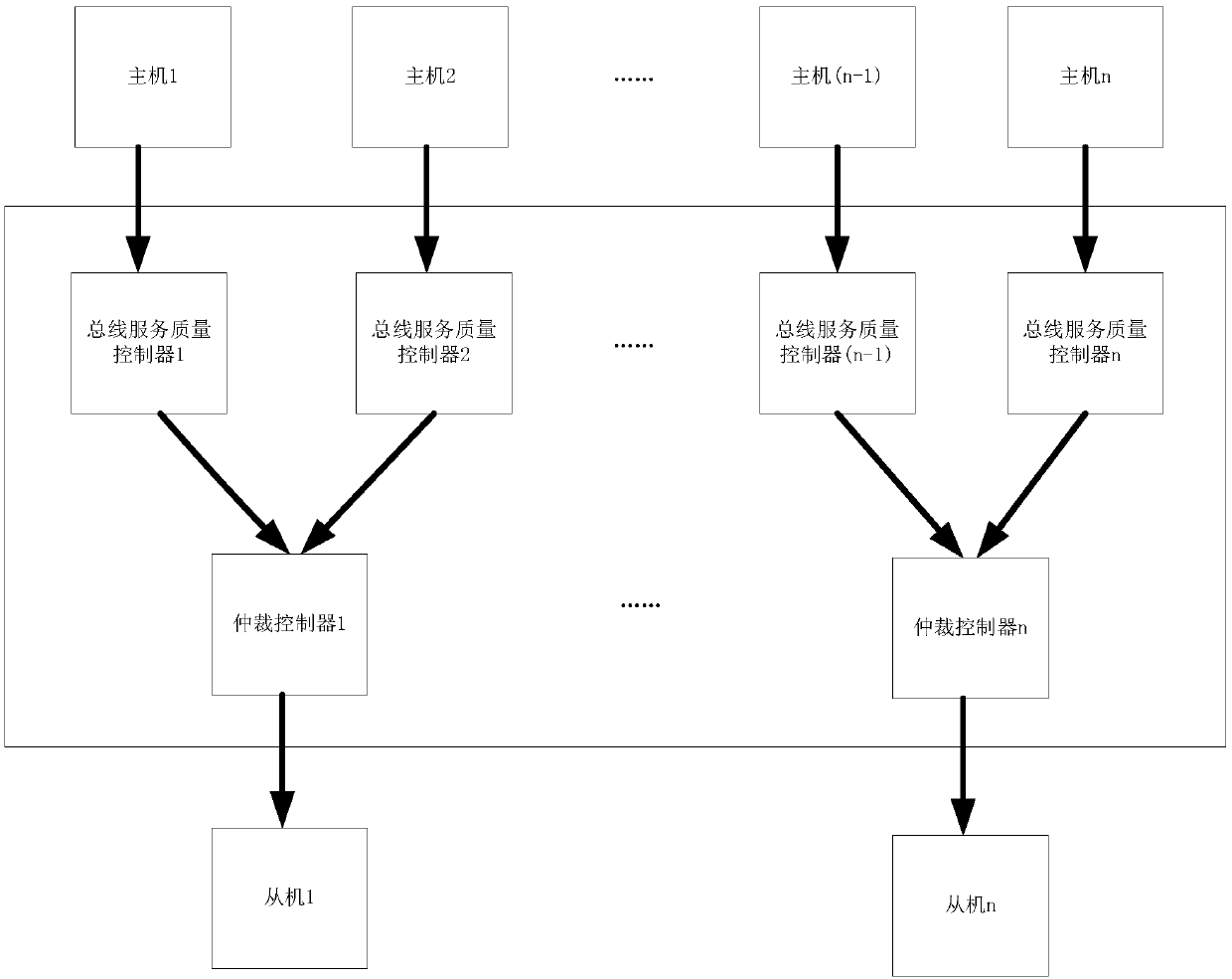

PCIe bus-based master-slave interactive communication platform and method

InactiveCN107066407AMaster-slave interactive communication implementationImprove bus efficiencyElectric digital data processingPhysical addressParallel computing

The invention relates to the technical field of communication, and provides a PCIe bus-based master-slave interactive communication platform and method. The platform comprises a host and a development board, wherein both the host and the development board are equipped with PCIe2.0X4 interfaces; master equipment and slave equipment are configured in the host and the development board; the host is used for configuring interactive communication data size and setting the master equipment and the slave equipment; interactive communication between the host and the development board adopts a query mode or an interruption mode; a memory applied on the host comprises a data cache and a descriptor table cache; the data cache is applied in a chained DMA manner; the descriptor table cache is applied in a continuous DMA manner; the data cache consists of memory pages, physical addresses of which are discontinuous; a descriptor table is formed by information of a plurality of discontinuous memory pages; and the descriptor table comprises a head item which is used for updating EPLAST information of communication ending information. According to the platform and the method, the PCIe bus-based master-slave interactive communication is realized, the bus efficiency is improved and the broadband performance maximization is realized.

Owner:TOEC TECH

Asynchronous bridge and data transmission

ActiveCN100483377CImplementation supportImprove bus efficiencyElectric digital data processingBurst transmissionData signal

A asynchronous bridge consists of asynchronous slave interface for emitting transmission request signal, secondary synchronous unit for secondary-synchronizing said transmission request signal, asynchronous master interface for setting up bus transmission of the second clock domain, two-way storage with its one end being connected to asynchronous slave interface and another end being connected to asynchronous master interface for storing data signal of bus burst transmission. Its data transmitting method is also disclosed.

Owner:HUAWEI TECH CO LTD

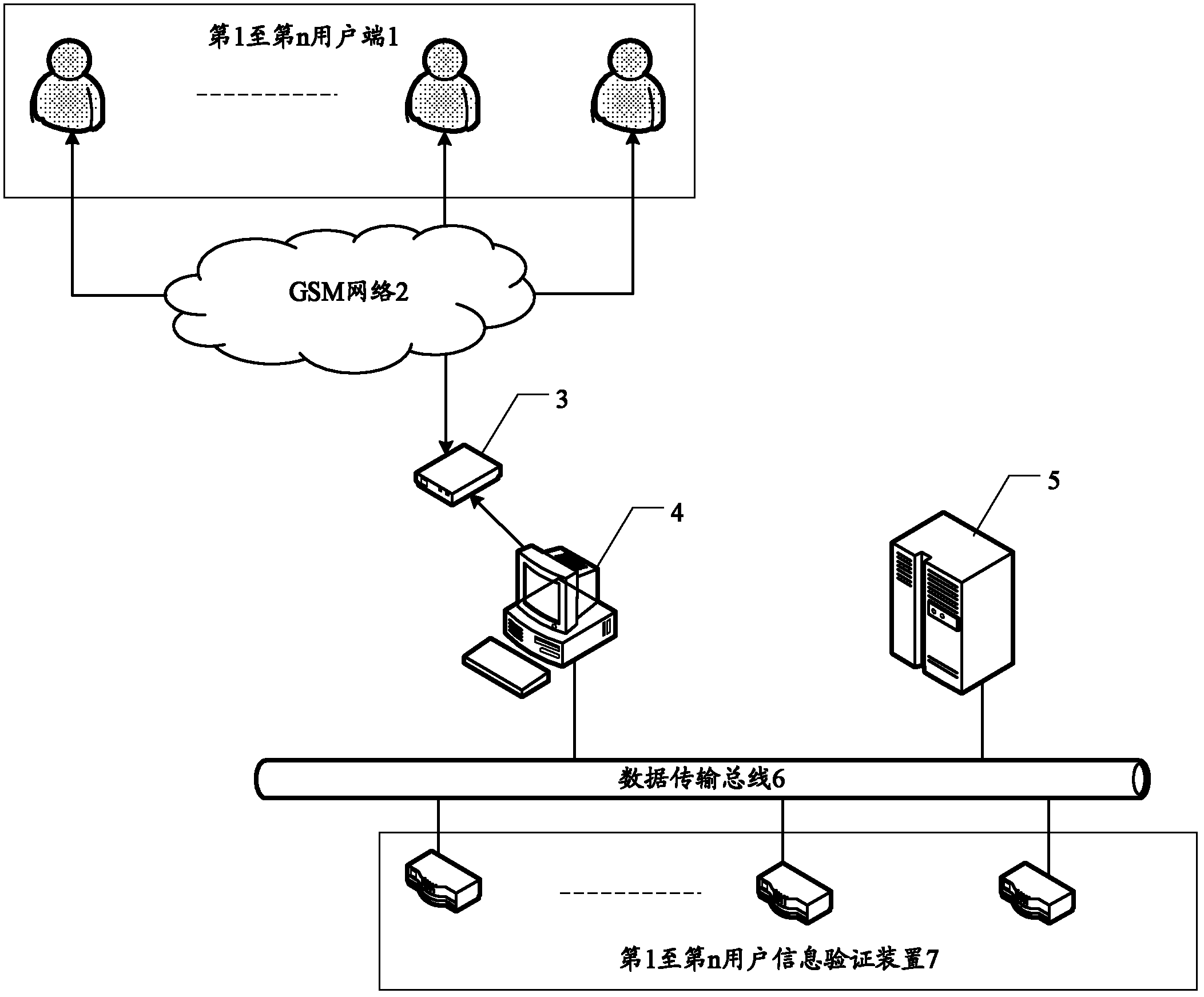

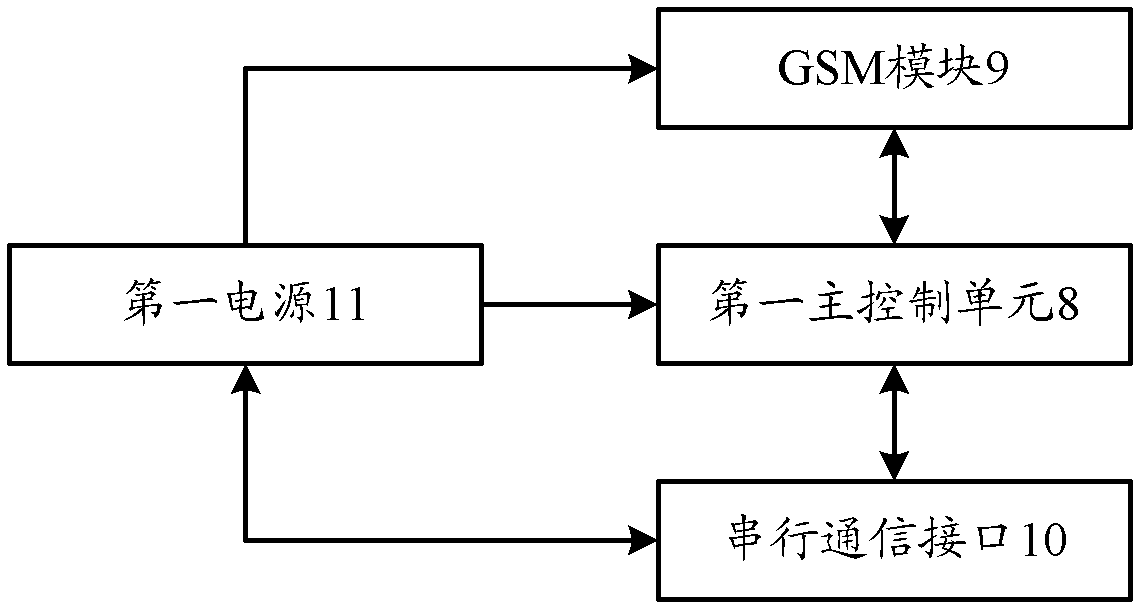

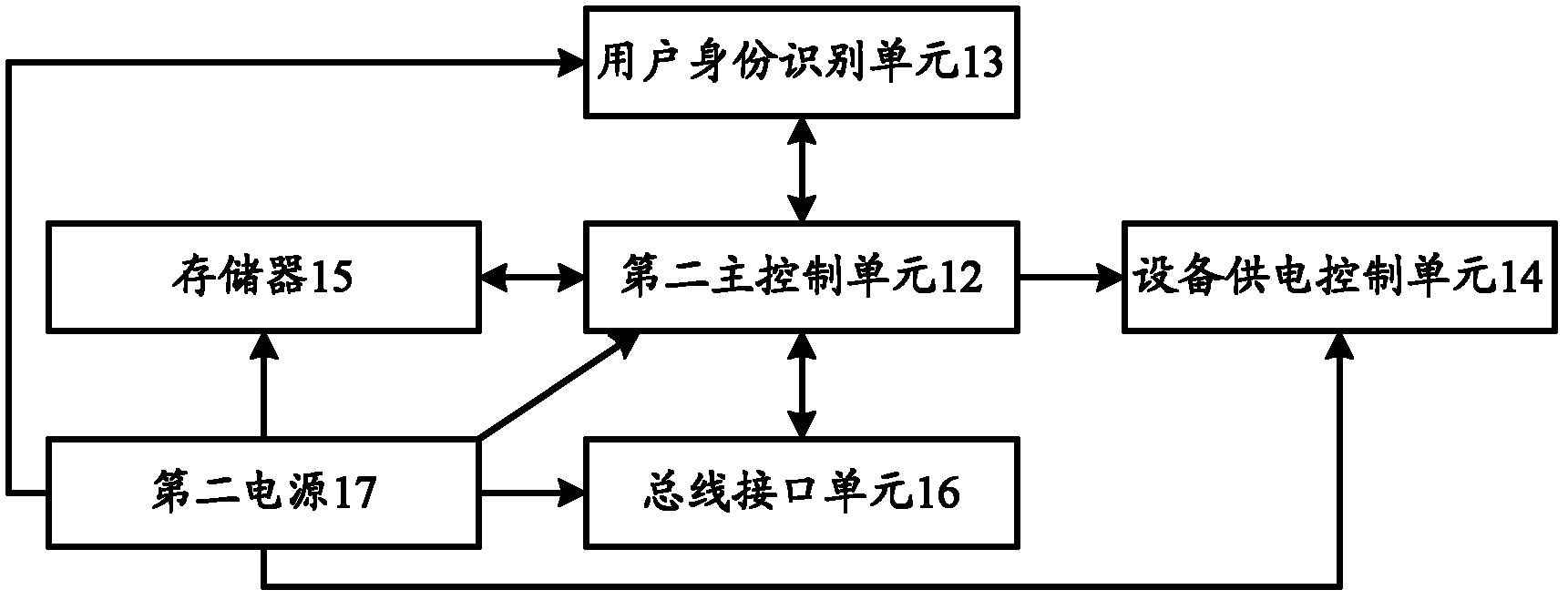

Short-message-based reservation and verification system and method

InactiveCN102196385AControl throughputReduce computing pressureMessaging/mailboxes/announcementsTransceiverDatabase server

The invention discloses a short-message-based reservation and verification system and a short-message-based reservation and verification method. The system comprises a plurality of users, a global system of mobile communication (GSM) network, a short message transceiver terminal, a management terminal platform, a database server, a data transmission bus and a plurality of user information verification devices, wherein the plurality of user information verification devices are connected with the management terminal platform and the database server by the data transmission bus respectively; and the plurality of users are sequentially connected with the short message transceiver terminal and the management terminal platform by the GSM network respectively. By the short-message-based reservation and verification system and the short-message-based reservation and verification method, the shortcomings of resource wasting, inconvenience of use, low management efficiency and the like of the prior art can be overcome, and the advantages of resource saving, convenience of use and high management efficiency can be achieved.

Owner:李元熙

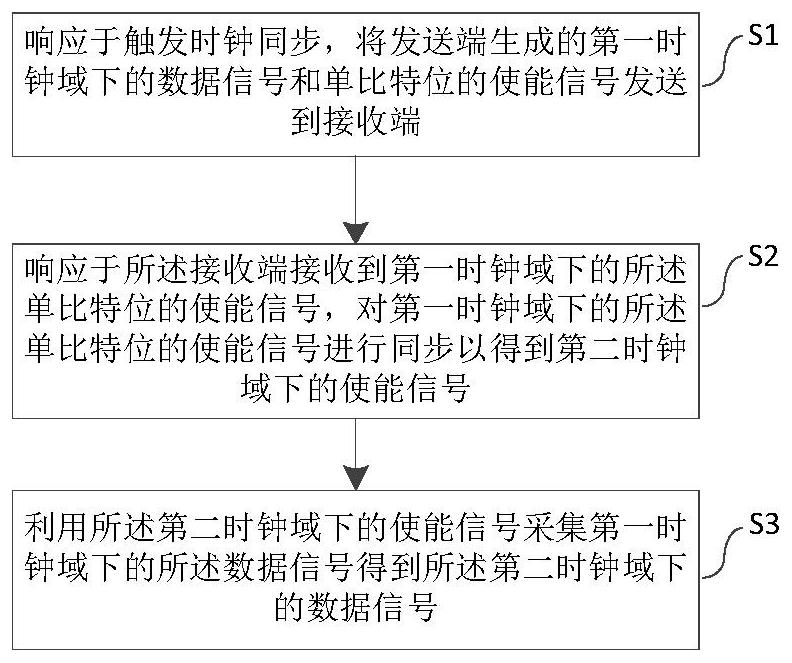

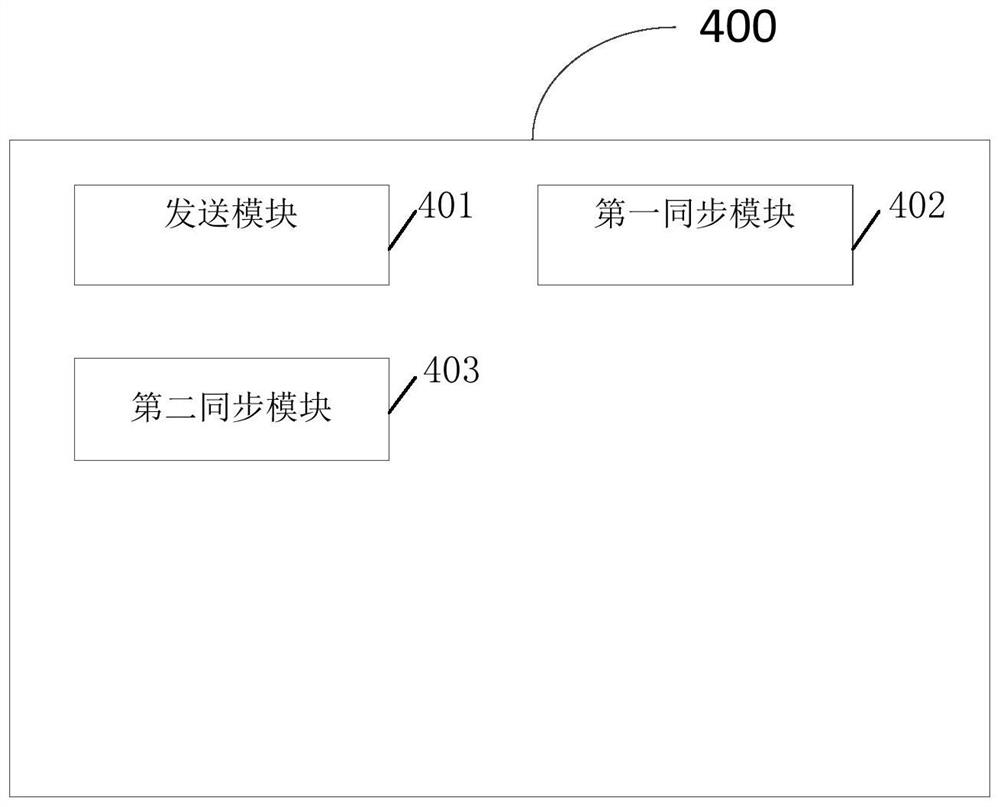

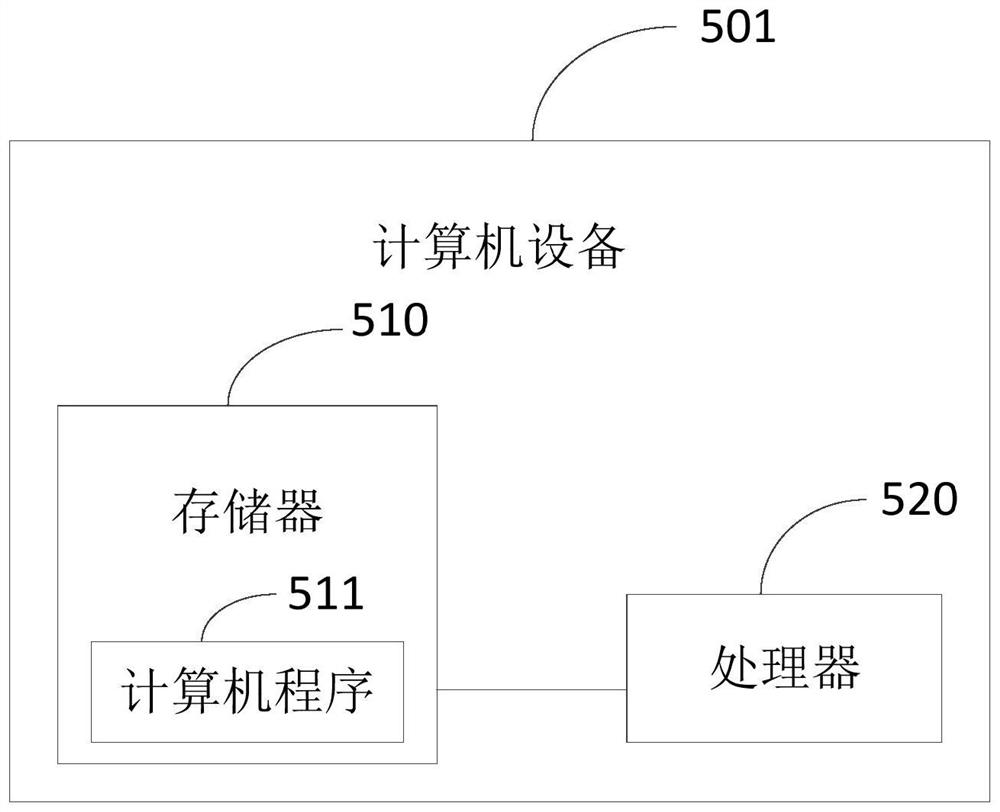

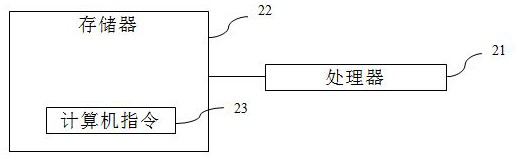

Cross-clock domain data signal synchronization method, system and device and medium

PendingCN114115443AReduce bus areaImprove bus efficiencyGenerating/distributing signalsEmbedded systemComputer equipment

The invention discloses a cross-clock domain data signal synchronization method, which comprises the following steps of: in response to triggering clock synchronization, sending a data signal in a first clock domain generated by a sending end and a single-bit enable signal to a receiving end; in response to the single-bit enable signal in a first clock domain received by the receiving end, synchronizing the single-bit enable signal in the first clock domain to obtain an enable signal in a second clock domain; and acquiring the data signal in the first clock domain by using the enable signal in the second clock domain to obtain the data signal in the second clock domain. The invention further discloses a system, computer equipment and a readable storage medium. The scheme provided by the invention can be used for realizing cross-clock domain synchronization of multi-bit wide data signals in the bus.

Owner:山东云海国创云计算装备产业创新中心有限公司

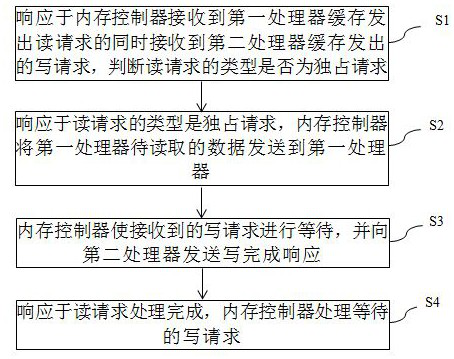

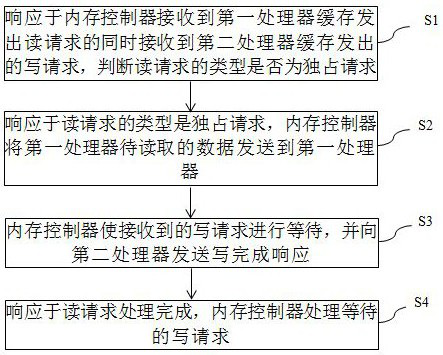

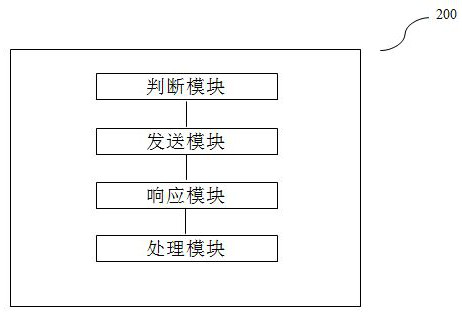

Cache consistency write-back method, device and equipment and medium

ActiveCN114116531AImprove bus efficiencyReduce bandwidth requirementsMemory systemsEngineeringCache consistency

The invention provides a cache consistency write-back method, device and equipment and a medium, and the method comprises the steps: in response to a situation that a memory controller receives a read request sent by a first processor cache and simultaneously receives a write request sent by a second processor cache, judging whether the type of the read request is an exclusive request; in response to the fact that the type of the read request is an exclusive request, the memory controller sends to-be-read data of the first processor to the first processor; the memory controller waits the received write request and sends a write completion response to the second processor; and in response to the completion of the read request processing, the memory controller processes the waiting write request. By using the scheme of the invention, the bus efficiency of the cache consistency system can be improved, and the bandwidth requirement of writing into the memory can be reduced.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

System and method for data packet segmentation and reassembly based on clos switching network

ActiveCN104954292BImprove throughputAvoid the case of short packetsData switching networksNetwork packetVariable length

Owner:FENGHUO COMM SCI & TECH CO LTD +1

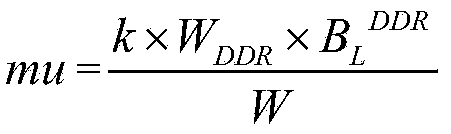

Method and device for achieving convolution interleave/de-interleave

ActiveCN103916140AImprove reading and writing efficiencyImprove bus efficiencyError correction/detection using convolutional codesEmbedded systemConvolution

The invention provides a method and device for achieving convolution interleave / de-interleave. The method and device improve bus efficiency and reduce DDR bandwidth. The method at least includes the steps that the minimum occupied bandwidth of a DDR is calculated according to the interleave transmission rate of a transmitting / receiving system; according to convolution interleave parameters, DDR storage space needed for the minimum occupied bandwidth is calculated; according to the DDR parameters, AXI bus parameters and interleave parameters, parameters of a data shaping storage device are calculated, and a Local address and an AXI bus continuous read or write range are generated; according to the generated parameters of the data shaping storage device, the Local address is converted into an AXI bus address, and data interaction with the DDR is finished. According to the method, considerations are preferably given to reduction of the DDR bandwidth and the improvement of the bus efficiency, a storage rule and a read-write address are specifically designed, so that DDR bandwidth occupied by interleave is minimized, and meanwhile read-write efficiency of a bus is improved substantially.

Owner:SHANGHAI HIGH DEFINITION DIGITAL TECH IND

Image processing apparatus and image processing interface circuit

ActiveUS9552619B2Improve bus efficiencyImage memory managementElectric digital data processingDirect memory accessImaging processing

An image processing apparatus includes a plurality of image processing module parts, a module arbiter part, and a DMAC (Direct Memory Access Controller) part. Each of the image processing module parts includes a module core for executing a predetermined image processing. The plurality of image processing module parts is connected to the module arbiter part. The module arbiter part arbitrates memory access which is given by the plurality of image processing module parts through a bus. The DMAC part is connected between the module arbiter part and the bus, and executes memory access related to the arbitration result obtained by the module arbiter part.

Owner:MEGACHIPS +1

Bus systems, apparatuses, and methods of operating a bus

InactiveUS7389469B2Increase speedImprove bus efficiencyError prevention/detection by using return channelFrequency-division multiplex detailsError checkData transmission

Owner:SAMSUNG ELECTRONICS CO LTD

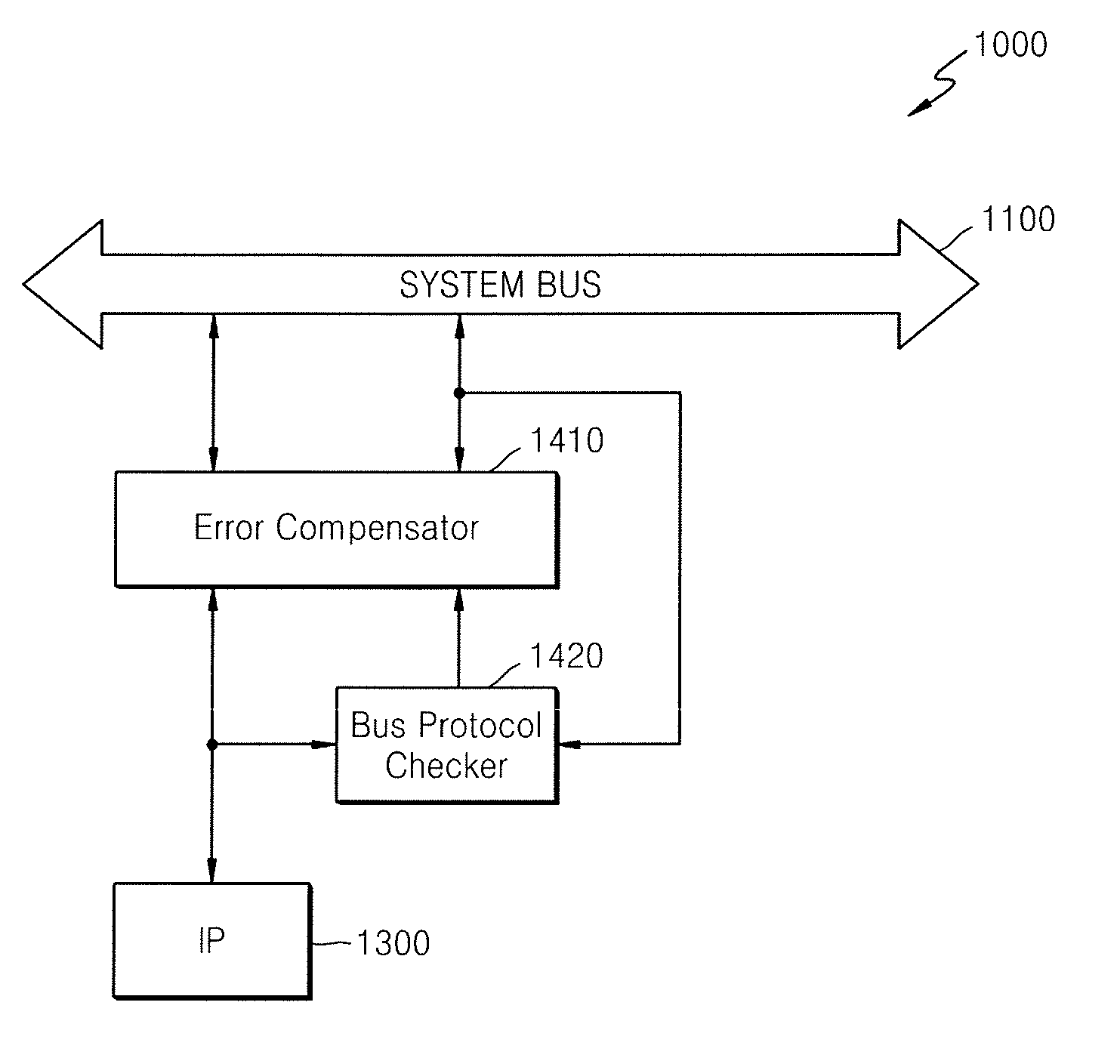

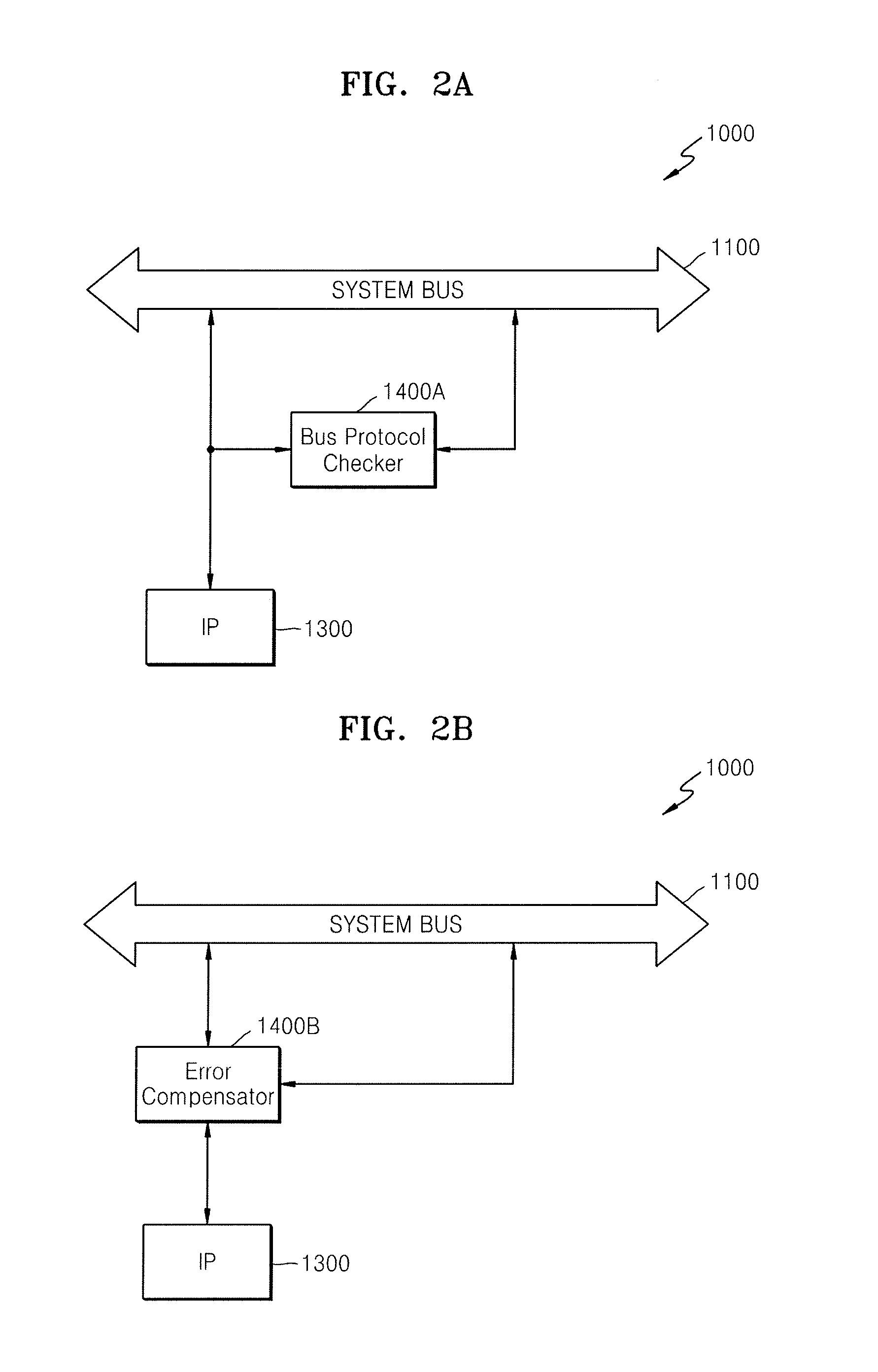

Bus protocol checker, system on chip including the same, bus protocol checking method

InactiveUS20140281759A1Improve bus efficiencyFault responseDetecting faulty computer hardwareComputer architectureEngineering

A system on chip (SoC) includes a system bus; a plurality of intellectual properties (IPs) outputting bus signals via the system bus; and one or more checkers disposed to correspond to at least some of the plurality of IPs, wherein the checker includes: a first environment setting register for setting information about a check target and list, on which a bus protocol check operation will be performed, wherein the setting may be variable according to an access from outside via the system bus; and a check logic receiving the bus signal and performing a bus protocol check operation on a signal included in the bus signal according to the information set in the first environment setting register.

Owner:SAMSUNG ELECTRONICS CO LTD

Image data accessing and decoding method and decoding device

ActiveCN100579225CIncrease profitReduce areaColor signal processing circuitsBrightness and chrominance signal processing circuitsAccess methodVideo decoder

Owner:HUAWEI TECH CO LTD

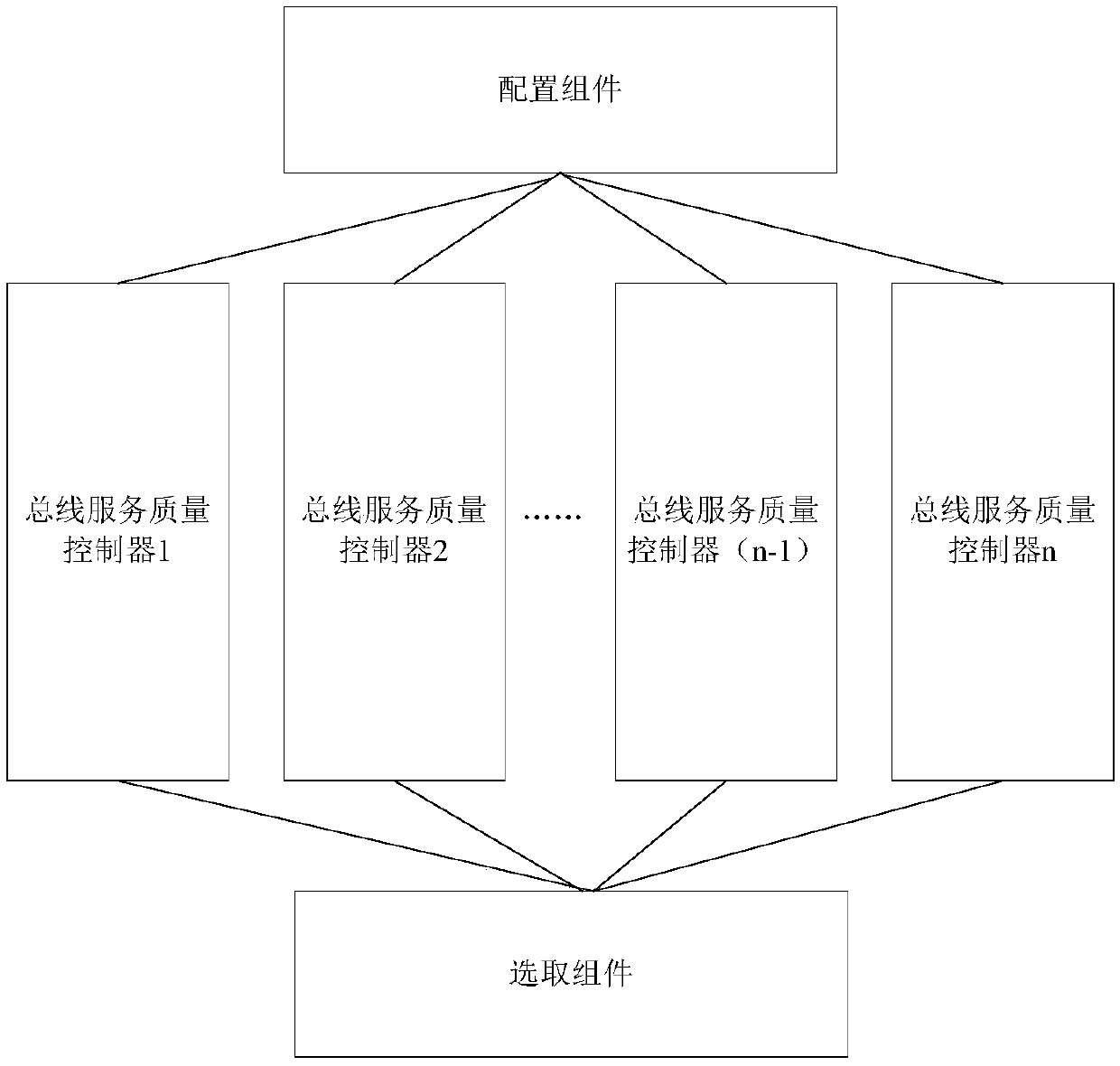

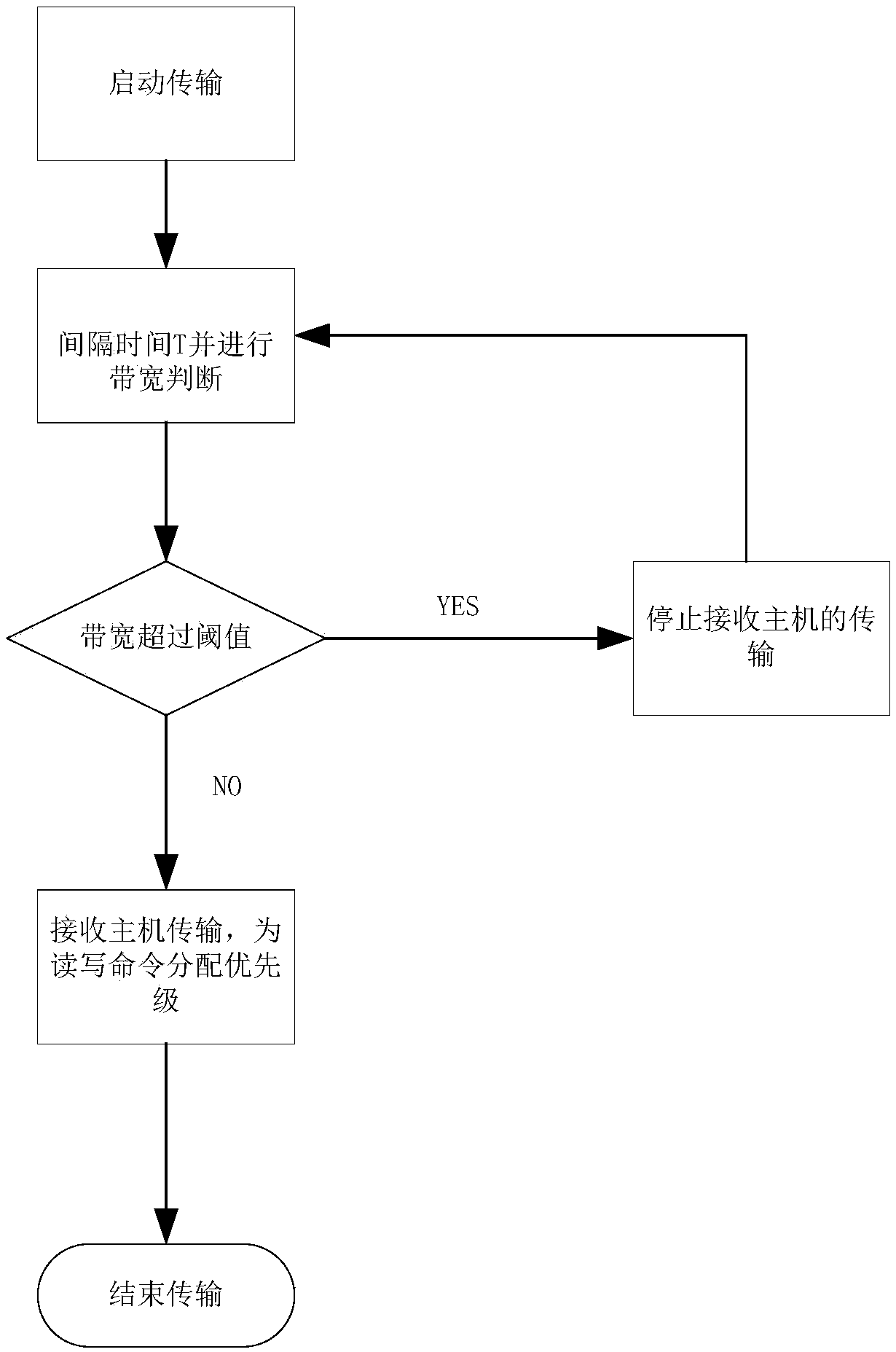

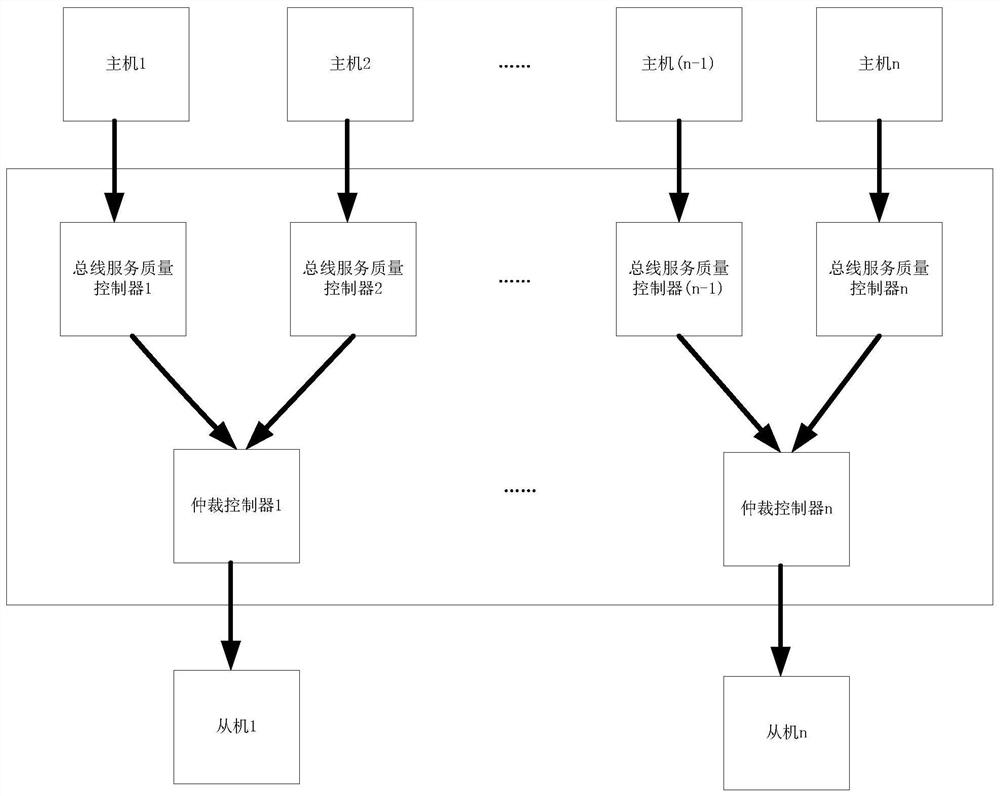

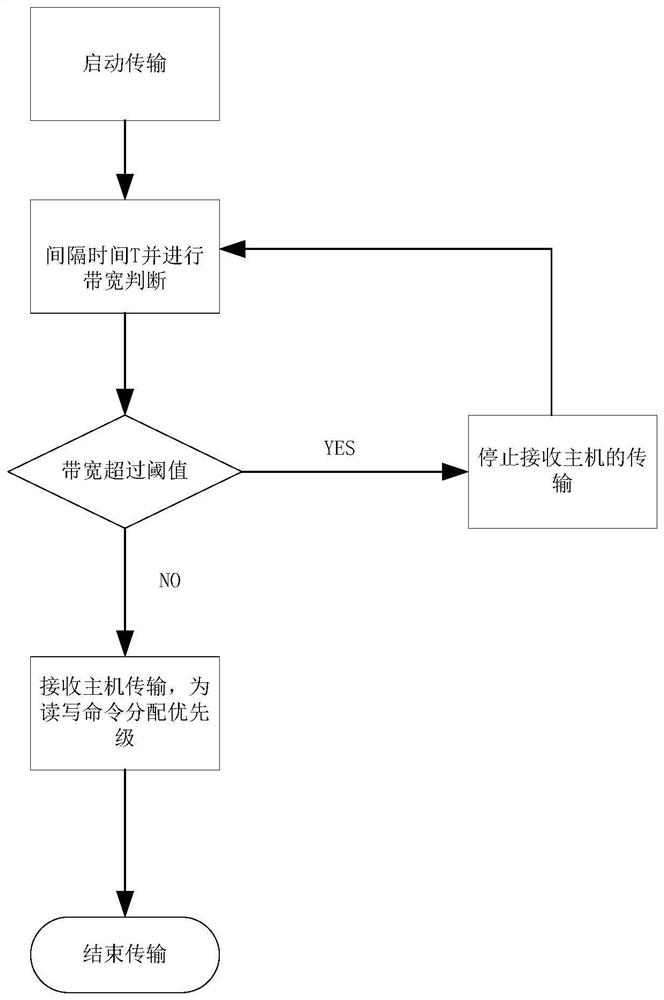

Bus transmission control device and method

ActiveCN110391960AAlleviate bandwidth performance bottlenecksImprove bus efficiencyBus networksEmbedded systemService control

The invention discloses a bus transmission control device and method. The device comprises a configuration component, a selection component and a plurality of bus service quality controllers, the configuration component is used for correspondingly allocating a bus service quality controller to each device requesting transmission; the selection component is used for selecting a current bus servicequality control mode of each bus service quality controller from preset bus service quality control modes; and each bus service quality controller is used for carrying out service control on the corresponding first bus link according to the current bus service quality control mode. According to the invention, the bus transmission efficiency of the chip is effectively improved.

Owner:ALLWINNER TECH CO LTD

A PCI bus controller and its control method

ActiveCN105224488BFlexible useMeet different requirementsElectric digital data processingProgrammable read-only memoryDirect memory access

The invention discloses a PCI (Peripheral Component Interconnect) bus controller and a control method thereof. Through SPI (Serial Peripheral Interface) signal multiplexing, two configuration information initialization ways including EEPROM (Electrically Erasable Programmable Read-Only Memory) loading or unloading are provided so as to be flexible in use; and through the arrangement of a plurality of interface modules, a SPI bus, a PCI bus, a Local bus and corresponding pin interfaces can be realized. The PCI bus controller can be used as PCI master / slave equipment, has a wide application range and meets different requirements of a system; and when the PCI bus controller is used as the PCI master equipment, DMA (Direct Memory Access) data transmission is carried out, CPU (Central Processing Unit) intervention is avoided, and system efficiency is improved. When the PCI bus controller is used as the PCI bus master equipment to initiate a bus operation, data interaction between system memory and Local equipment is finished; and during non DMA transmission, the PCI bus controller is used as the PCI bus slave equipment to response to the bus operation. The PCI bus controller provides 8-bit, 16-bit, 32-bit multiplex / non-multiplex Local bus interfaces, can configure and realize various working ways including emergency, prefetching, internal waiting, external waiting, write cycle maintaining, read-write gating delay, big end and small end alignment, local chip selection, local interruption and the like, and is high in universality.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

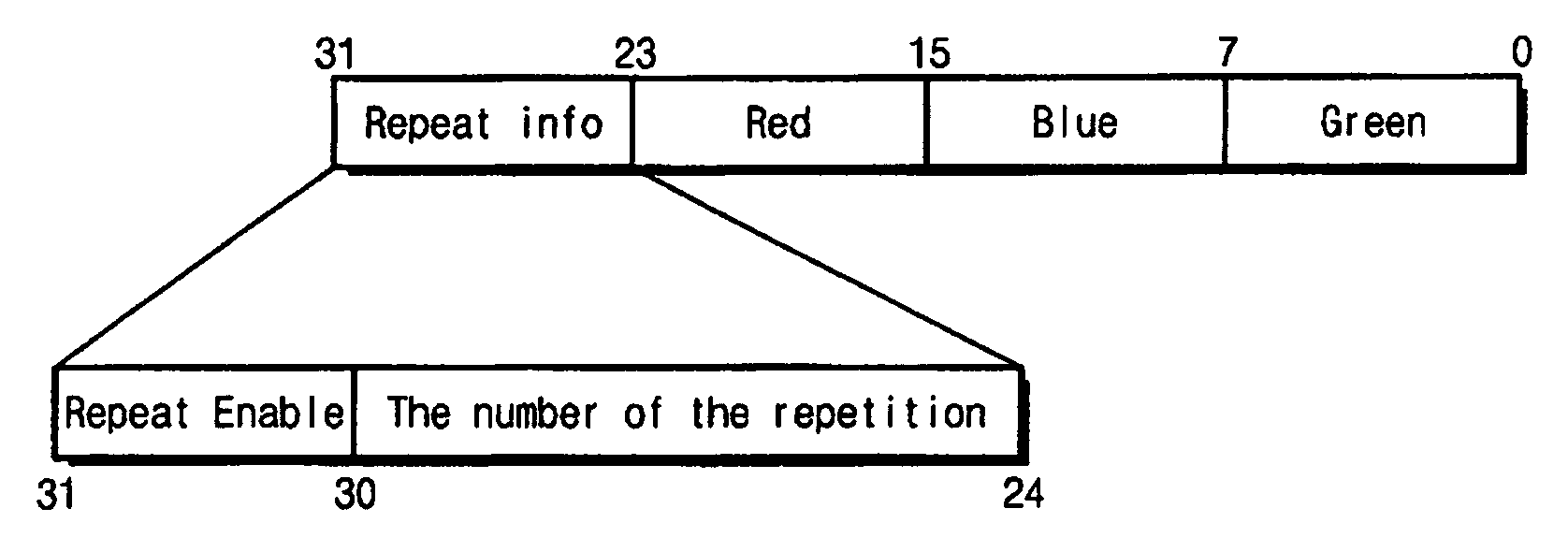

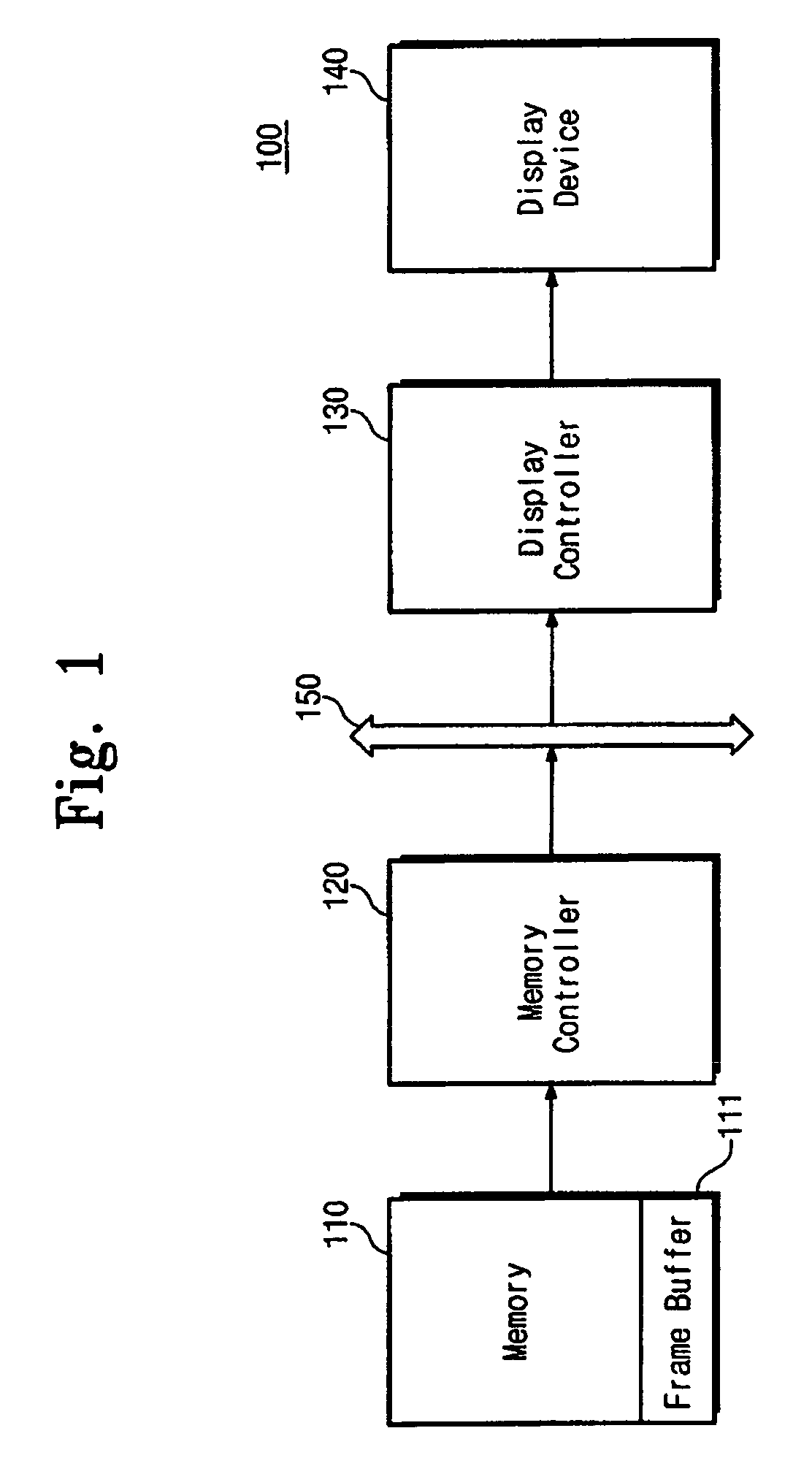

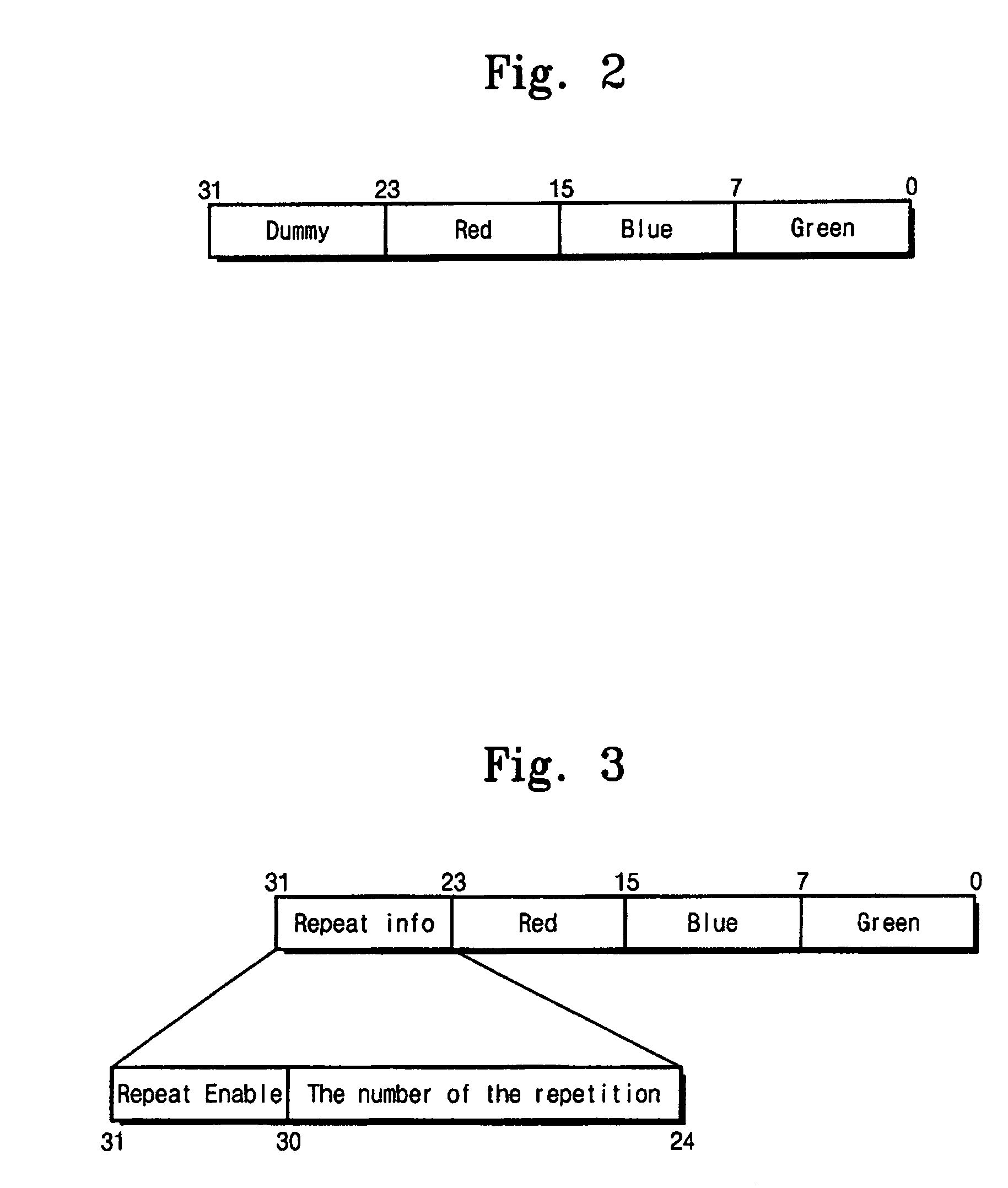

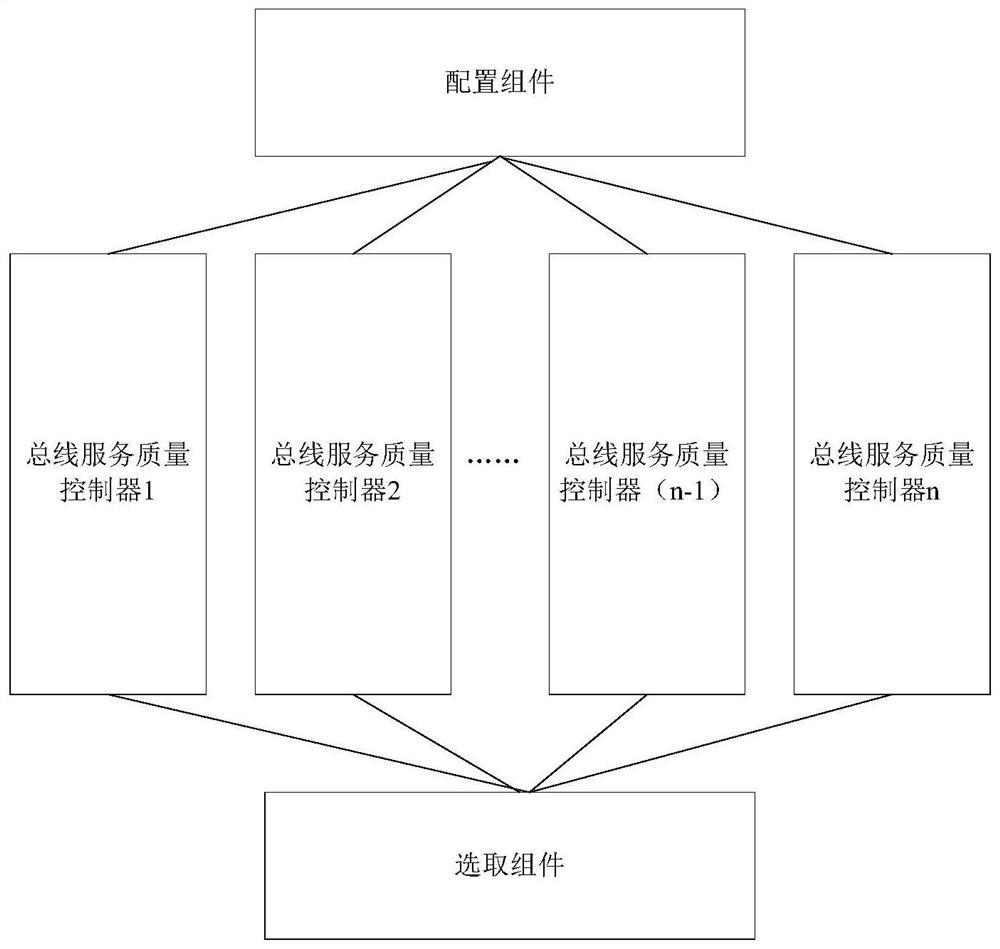

Image display system and method for increasing efficiency of bus bandwidth

ActiveUS8477144B2Improve bus efficiencyLimited bandwidthImage memory managementCathode-ray tube indicatorsData displayDisplay device

An image display system includes: a frame buffer having a plurality of lines, each of which stores image data and repetition information of the image data; a memory controller in signal communication with the frame buffer for reading the image data and the repetition information from the frame buffer; a display controller in signal communication with the memory controller for regenerating the image data, which is provided from the memory controller, in accordance with the repetition information provided from the memory controller; and a display device in signal communication with the display controller for displaying the regenerated image data, which is provided from the display controller, under regulation by the display controller.

Owner:SAMSUNG ELECTRONICS CO LTD

Bus transmission control device and method

ActiveCN110391960BAlleviate bandwidth performance bottlenecksImprove bus efficiencyBus networksService controlEmbedded system

The invention discloses a bus transmission control device and method. The device includes a configuration component, a selection component and a plurality of bus service quality controllers; the configuration component is used to assign a bus service to each device requesting transmission Quality controller; the selection component is used to select the current bus quality of service control mode of each bus quality of service controller from the preset bus quality of service control mode; each bus quality of service controller is used to select the current bus quality of service control mode according to the current The bus quality of service control mode performs service control on the corresponding first bus link. The invention effectively improves the bus transmission efficiency of the chip.

Owner:ALLWINNER TECH CO LTD

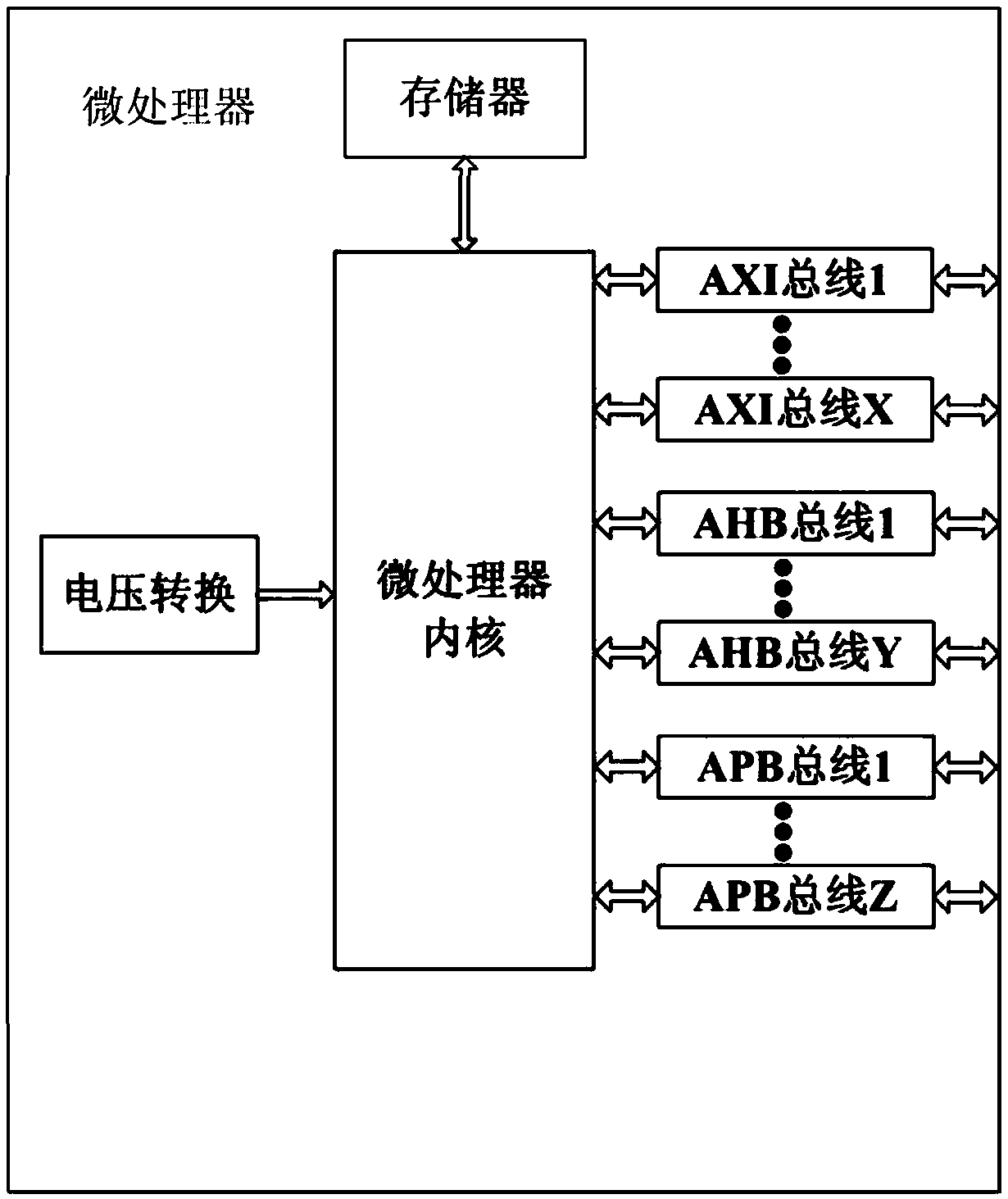

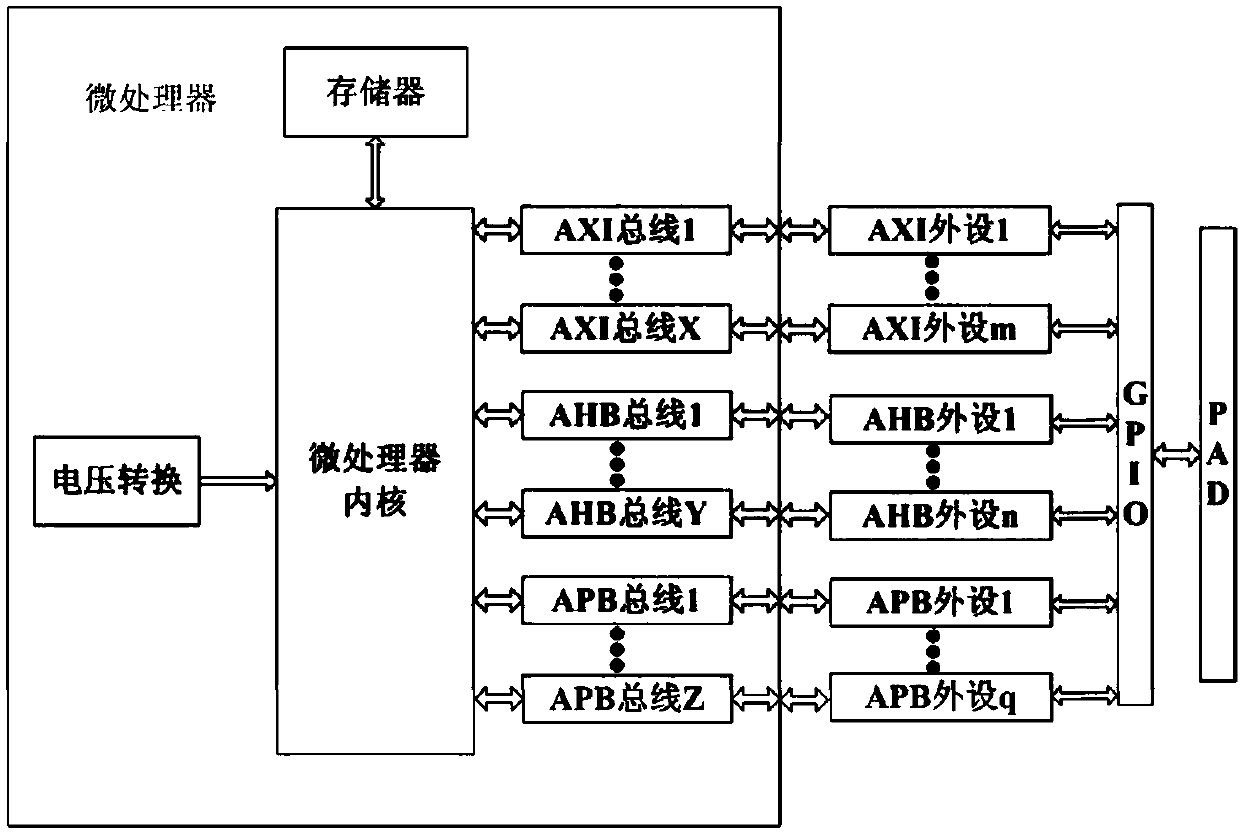

configurable multi-channel IO direct connection type microprocessor system

PendingCN109582624AImprove scalabilityImprove bus efficiencyArchitecture with single central processing unitElectric digital data processingBus interfacePeripheral

The invention relates to a configurable multi-channel IO direct connection type microprocessor system which comprises a microprocessor kernel, a memory module and a voltage conversion module, and themicroprocessor kernel is connected with a peripheral device through an AXI bus, an AHB bus and an APB bus. According to the system, a user can directly carry out multi-class and multi-group bus connection on the microprocessor core, and the microprocessor peripheral is directly connected with the microprocessor core through different bus interfaces. According to the system, the microprocessor kernel can control microprocessor peripherals, and reading and writing are not affected by other modules.

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

A method, apparatus, device, and medium for cache-coherent write-back

ActiveCN114116531BImprove bus efficiencyReduce bandwidth requirementsMemory systemsEngineeringTerm memory

The present invention provides a cache consistency write-back method, device, device, and medium. The method includes: in response to the memory controller receiving a read request issued by the first processor cache and simultaneously receiving a read request from the second processor cache. write request, determine whether the type of the read request is an exclusive request; in response to the type of the read request being an exclusive request, the memory controller sends the data to be read by the first processor to the first processor; the memory controller makes the received The write request waits and sends a write completion response to the second processor; in response to the completion of the read request processing, the memory controller processes the pending write request. By using the solution of the present invention, the cache coherence system bus efficiency can be improved, and the bandwidth requirement for writing memory can be reduced.

Owner:SUZHOU METABRAIN INTELLIGENT TECH CO LTD