Cross-clock domain data signal synchronization method, system and device and medium

A data signal, cross-clock domain technology, applied in the field of data synchronization, can solve the problems of complex cross-clock processing, asynchronous FIFO increase, and difficult timing convergence, etc., to achieve the effect of reducing the system bus area and improving the system bus efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] In order to make the object, technical solution and advantages of the present invention clearer, the embodiments of the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0043] It should be noted that all expressions using "first" and "second" in the embodiments of the present invention are to distinguish two entities with the same name but different parameters or parameters that are not the same, see "first" and "second" It is only for the convenience of expression, and should not be construed as a limitation on the embodiments of the present invention, which will not be described one by one in the subsequent embodiments.

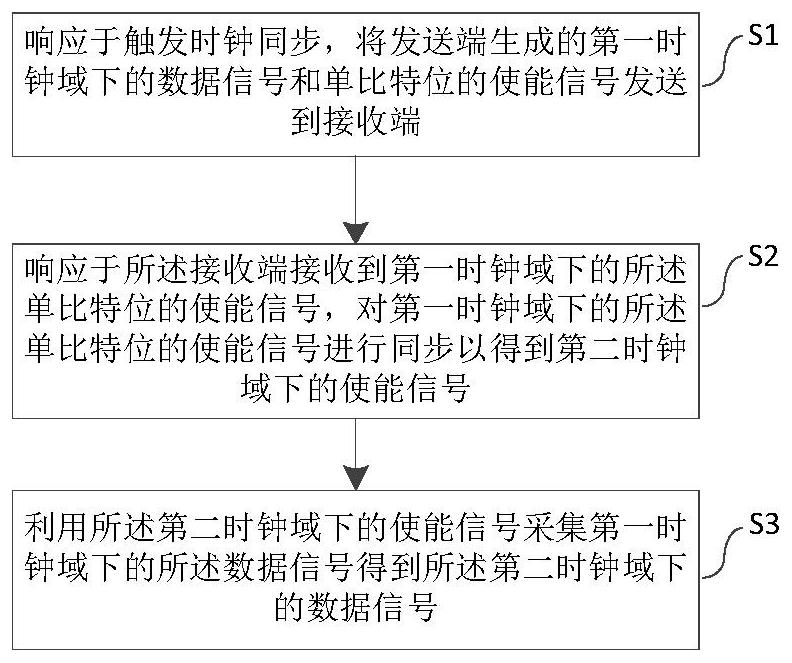

[0044] According to one aspect of the present invention, an embodiment of the present invention proposes a data signal synchronization method across clock domains, such as figure 1 As shown, it may include the steps of:

[0045] S1, in response to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More