Method and device for calibrating sleep clock of TD-SCDMA terminal

A TD-SCDMA, clock calibration technology, applied in synchronization devices, selection devices, advanced technologies, etc., can solve the problems of short sleep time of terminals, adverse effects of standby time, etc., to reduce the average duration, prolong the actual sleep time, The effect of reducing the number of times

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

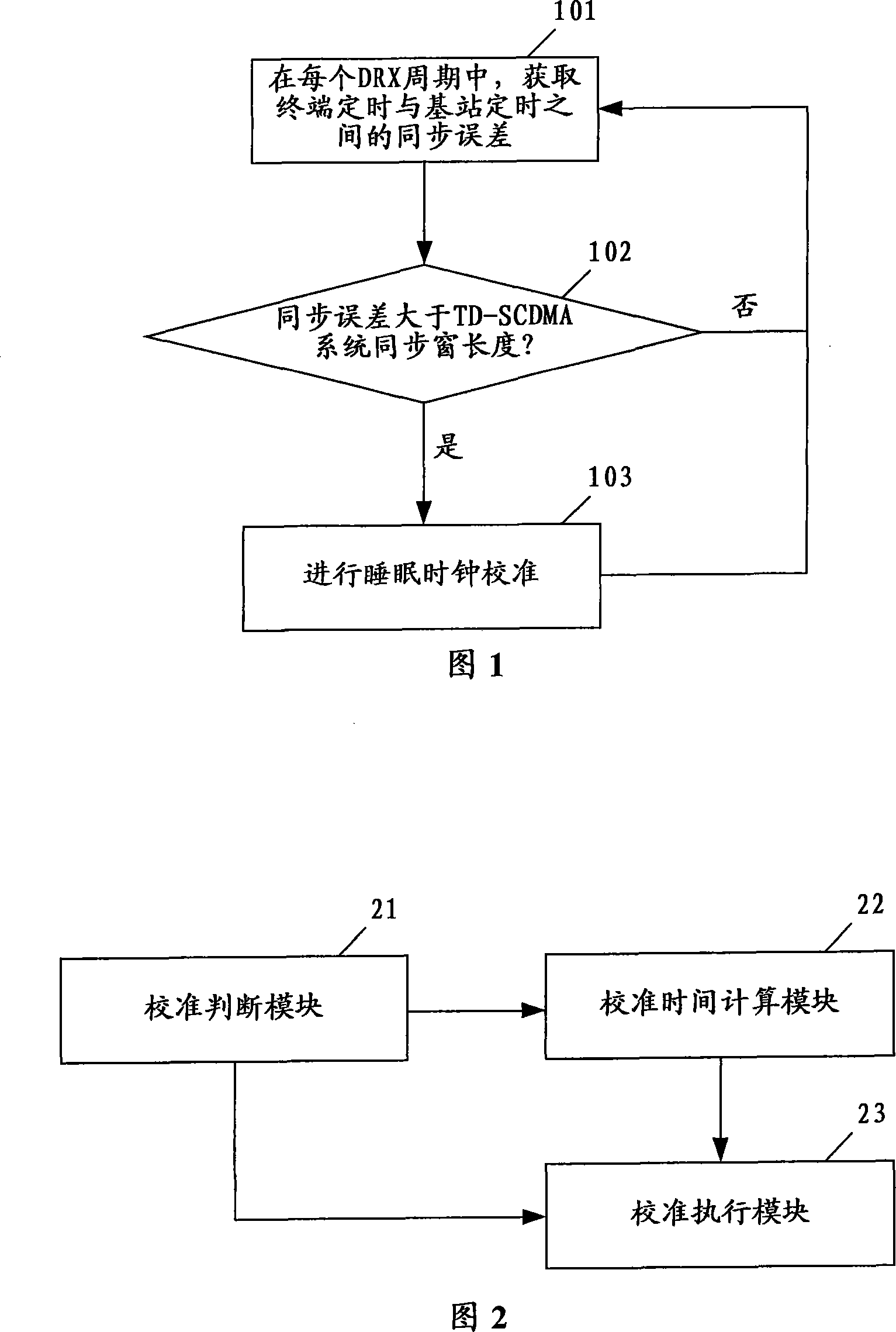

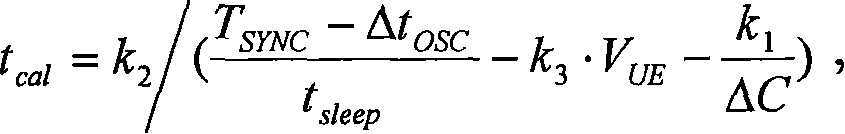

[0032] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in detail below with reference to the accompanying drawings and specific embodiments.

[0033] The key of the present invention is: since the TD-SCDMA terminal in standby mode needs to wake up once in each DRX cycle and synchronize with the DwPTS of the base station, if the synchronization error between the terminal timing and the base station timing is not greater than the synchronization window of the system length, there is no need to perform sleep clock calibration; further, on the premise of satisfying the clock calibration accuracy, the calibration duration is dynamically adjusted by using the parameters of the network side in the TD-SCDMA system and the environmental parameters of the terminal itself.

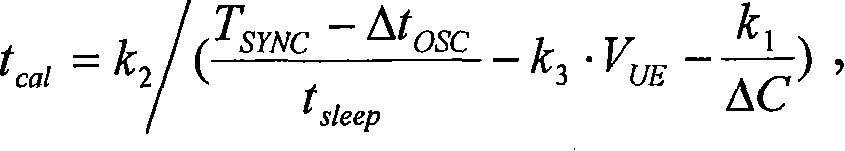

[0034] Suppose the synchronization window length of TD-SCDMA system is T SYNC (The length of the synchronization window corresp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More