Layout architecture with high-performance and high-density design

A layout and electrical connection technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of excessively long connecting lines, waste of layout area, and increased difficulty of winding, and achieve enhanced driving capabilities and high-performance design Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

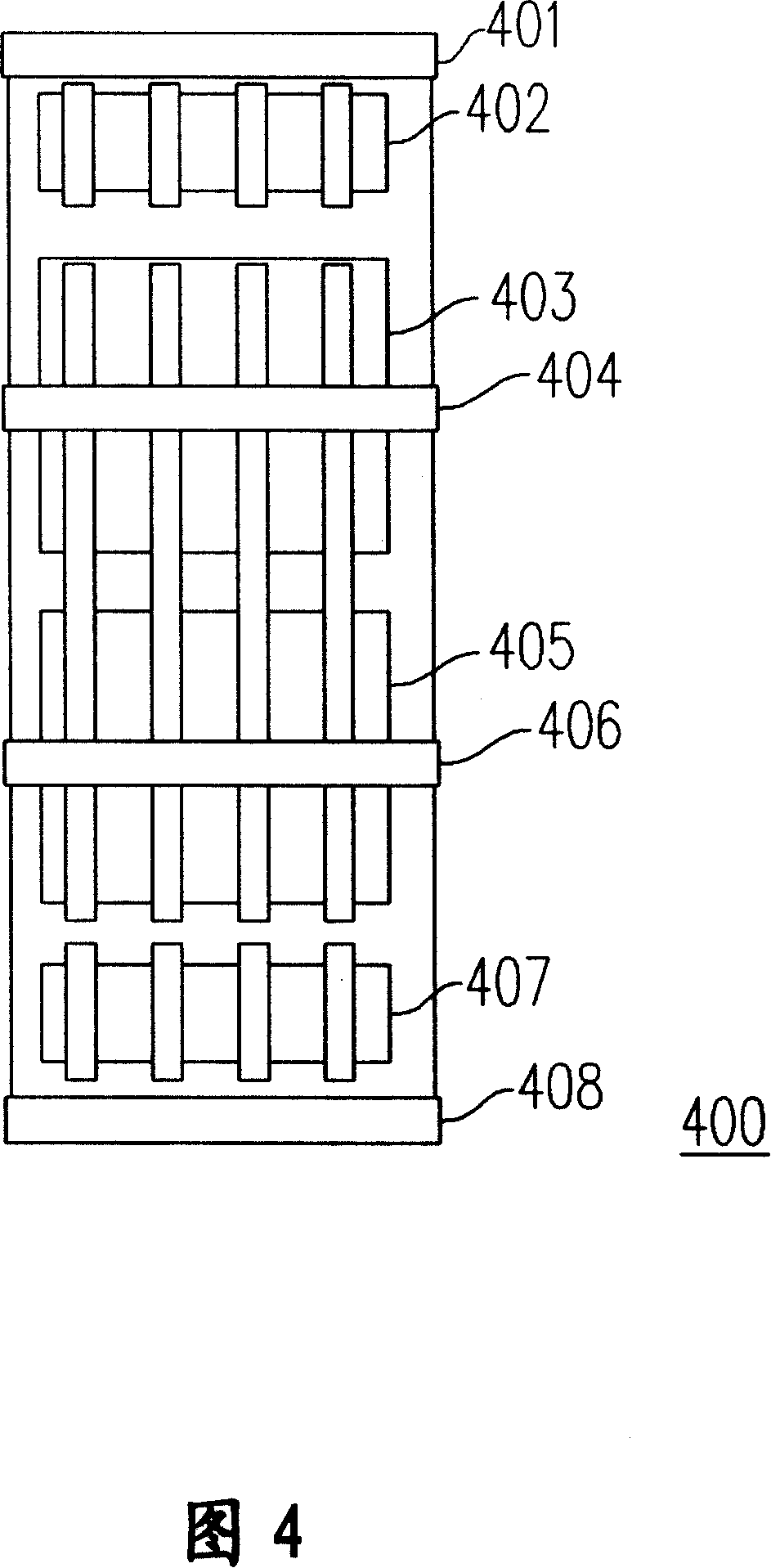

[0032] FIG. 4 is a layout diagram of a high-performance and high-density layout architecture 400 according to an embodiment of the present invention. The standard unit 400 includes a base (not shown), and conductors 401, 404, 406, 408 and element regions 402, 403, 405, 407 are arranged on the base, the conductors 401, 406 have a voltage VCC, and the conductors 404, 408 have a voltage VCC GND.

[0033] The element area 402 is configured with a plurality of P-type metal oxide semiconductor (MOS) transistors for short, and the element area 402 is connected to the conductor 401 to obtain the voltage VCC, and the element area 402 is connected to the element area 403 . The element area 403 is configured with a plurality of N-type MOS transistors, the element area 403 is connected to the element area 402 and the element area 405 , and the element area 403 is located under the conductor 404 . The device area 403 can obtain the voltage GND through the connection conductor 404 . The e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More